|

Главная |

Фоннеймановская архитектура ВМ

|

из

5.00

|

-

Принцип двоичного кодирования.

Принцип двоичного кодирования. - Принцип однородности памяти.

Как программы (команды), так и относящиеся к программам данные хранятся в одной и той же памяти

- Принцип адресуемости памяти.

Структурно основная память состоит из пронумерованных ячеек;

Все команды располагаются в памяти и выполняются последовательно, одна после завершения другой, в последовательности, определяемой программой.

- Принцип жесткости архитектуры.

Неизменяемость в процессе работы топологии, архитектуры, списка команд.

Компьютеры, построенные на этих принципах, относят к типу фоннеймановских.

Алгоритм выборки команды в ВМ с фоннеймановской архитектурой.

Когда устройство управления завершит выполнение команды, оно должно выбрать следующую команду из памяти в РгК. Адрес следующей команды содержится в специальном регистре, называемом Счетчиком Команд (СчК). Всякий раз при выборке команды устройство управления одновременно увеличивает содержимое СчК на единицу, чтобы после выполнения команды можно было произвести выборку следующей. Таким образом, устройство управления работает с командами в порядке, в котором они помещены в ОЗУ.

Когда устройство управления завершит выполнение команды, оно должно выбрать следующую команду из памяти в РгК. Адрес следующей команды содержится в специальном регистре, называемом Счетчиком Команд (СчК). Всякий раз при выборке команды устройство управления одновременно увеличивает содержимое СчК на единицу, чтобы после выполнения команды можно было произвести выборку следующей. Таким образом, устройство управления работает с командами в порядке, в котором они помещены в ОЗУ.

Последовательность выборки команды:

а) копируется адрес следующей команды из СчК в РгАП (адрес 8 в примере на рис);

б) прибавляется 1 к содержимому СчК СчК:=СчК+1 ( 9 );

в) содержимое ячейки (команда), которая адресуется РгАП, пересылается в РгД;

г) содержимое РгД копируется в РгК.

*РгАП – регистр адреса памяти

Представление чисел в ВМ.

Машинным изображением числа называют его представление в разрядной сетке ЭВМ. В вычислительных машинах применяются две формы представления чисел:

- естественная форма или форма с фиксированной запятой (точкой);

- нормальная форма или форма с плавающей запятой (точкой);

Пример:(естественная форма) 452,34 = 452340*10-3 = 0,0045234*105 = 0,45234*103(нормальная форма)

Всякое десятичное число, прежде чем оно попадает в память компьютера, преобразуется по схеме: X10 → X2 = M1 × [102]r

После этого осуществляется ещё одна важная процедура: мантисса с её знаком заменяется кодом мантиссы с её знаком; порядок числа с его знаком заменяется кодом порядка с его знаком.

Существуют следующие коды двоичных чисел:

- Прямой код; Обратный код; Дополнительный код.

Последние две формы применяются особенно широко, так как позволяют упростить конструкцию арифметико-логического устройства компьютера путем замены разнообразных арифметических операций операцией сложения.

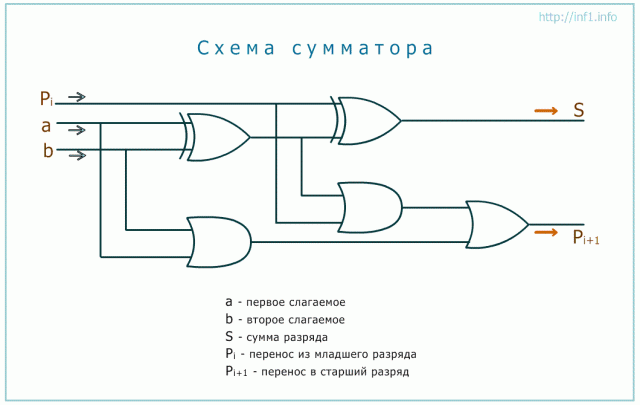

Сумматоры.

Арифметико-логическое устройство процессора (АЛУ) обязательно содержит в своем составе такие элементы как сумматоры. Эти схемы позволяют складывать двоичные числа.

Арифметико-логическое устройство процессора (АЛУ) обязательно содержит в своем составе такие элементы как сумматоры. Эти схемы позволяют складывать двоичные числа.

Как происходит сложение? Допустим, требуется сложить двоичные числа 1001 и 0011. Сначала складываем младшие разряды (последние цифры): 1+1=10. Т.е. в младшем разряде будет 0, а единица – это перенос в старший разряд. Далее: 0 + 1 + 1(от переноса) = 10, т.е. в данном разряде снова запишется 0, а единица уйдет в старший разряд. На третьем шаге: 0 + 0 + 1(от переноса) = 1. В итоге сумма равна 1100.

Сумматор учитывает перенос из предыдущего разряда, поэтому имеет три входа.

Чтобы учесть перенос приходится схему усложнять. По-сути она получается, состоящей из двух полусумматоров.

Чтобы учесть перенос приходится схему усложнять. По-сути она получается, состоящей из двух полусумматоров.

Рассмотрим один из случаев. Требуется сложить 0 и 1, а также 1 из переноса. Сначала определяем сумму текущего разряда. Судя по левой схеме ИСКЛЮЧАЮЩЕЕ ИЛИ, куда входят a и b, на выходе получаем единицу. В следующее ИСКЛЮЧАЮЩЕЕ ИЛИ уже входят две единицы. Следовательно, сумма будет равна 0.

Рассмотрим один из случаев. Требуется сложить 0 и 1, а также 1 из переноса. Сначала определяем сумму текущего разряда. Судя по левой схеме ИСКЛЮЧАЮЩЕЕ ИЛИ, куда входят a и b, на выходе получаем единицу. В следующее ИСКЛЮЧАЮЩЕЕ ИЛИ уже входят две единицы. Следовательно, сумма будет равна 0.

Теперь смотрим, что происходит с переносом. В один вентиль И входят 0 и 1 (a и b). Получаем 0. Во второй вентиль (правее) заходят две единицы, что дает 1. Проход через вентиль ИЛИ нуля от первого И и единицы от второго И дает нам 1.

Проверим работу схемы простым сложением 0 + 1 + 1 = 10. Т.е. 0 остается в текущем разряде, и единица переходит в старший. Следовательно, логическая схема работает верно.

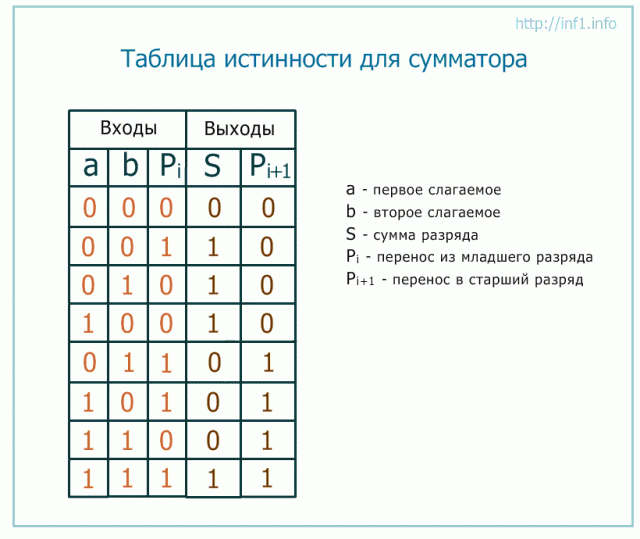

Работу данной схемы при всех возможных входных значениях можно описать следующей таблицей истинности.

Арифметико-логические устройства. Их классификация.

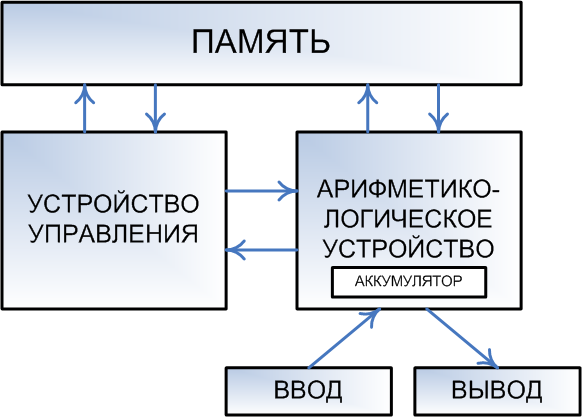

Арифме́тико-логи́ческое устро́йство (АЛУ) (англ. arithmetic and logic unit, ALU) — блок процессора, который под управлением устройства управления (УУ) служит для выполнения арифметических и логических преобразований (начиная от элементарных) над данными, представляемыми в виде машинных слов, называемыми в этом случае операндами

По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами. В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

По способу представления чисел различают АЛУ:

· для чисел с фиксированной точкой;

· для чисел с плавающей точкой;

· для десятичных чисел.

По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы..

Структура АЛУ для сложения и вычитания чисел с фиксированной точкой.

Операция сложения в АЛУ обычно сводится к арифметическому сложению кодов чисел путём применения инверсных кодов - дополнительного или обратного для представления отрицательных чисел. Обратный код имеет два представления нуля (+0, -0), что затрудняет анализ результата операции. Поэтому чаще используется дополнительный код.

Алгоритм сложения двоичных чисел с фиксированной запятой, при использовании дополнительного кода для представления отрицательных чисел, заключается в следующем. Производится сложение двоичных кодов, включая разряды знаков. Если при этом возникает перенос из знакового разряда суммы при отсутствии переноса в этот разряд, или возникает перенос в знаковый разряд при отсутствии переноса из разряда знака, то происходит переполнение разрядной сетки. Такой результат получается как при отрицательной, так и положительной суммах. Если нет переносов из знакового и в знаковый разряд суммы или есть оба эти переноса, то переполнения нет. Если получен 0 в знаковом разряде, то сумма положительна и представлена в прямом коде. Если получена 1 в знаковом разряде, то сумма отрицательна и представлена в дополнительном коде.

На рис. 4.3.2 представлена упрощённая структурная схема АЛУ для операций сложения и вычитания n-разрядных (нулевой разряд знаковый) двоичных чисел с фиксированной запятой. редполагается, что отрицательные числа хранятся в памяти в дополнительном коде.

Рисунок 4.3.2- Структура АЛУ для операций сложения и вычитания

В состав АЛУ входят n-разрядный параллельный комбинационный сумматор См, регистр сумматора РгСМ, входные регистры сумматора РгA и РгB, входной регистр АЛУ Рг1.

Операнды читаются из оперативной памяти и поступают в АЛУ по входной ШД (в дальнейшем- ШВХ). Для рассматриваемой структуры АЛУ положительные числа должны быть представлены прямым кодом, а отрицательные - дополнительным. Первый операнд размещается в РгB (первое слагаемое или уменьшаемое), а второй в РгА (второе слагаемое или вычитаемое); Рг1 связан с РгA цепями прямой и инверсной передачи кода. Прямая передача используется при операции сложения, а инверсная - при операции вычитания. Результат операции выдается из АЛУ в оперативную память по выходной ШД (в дальнейшем- ШВЫХ).

Структура АЛУ для умножения чисел с фиксированной точкой.

Так как операция умножения относится к длинным операциям, для уменьшения времени ее выполнения существуют различные методы ускорения. Все методы делят на аппаратные и логические. И те и другие методы требуют дополнительных затрат оборудования. При использовании аппаратных методов дополнительные затраты оборудования прямопропорциональны числу разрядов. Данные методы вызывают усложнение схемы, ее удорожание и снижение надежности. Логические методы не зависят от разрядов операндов. Усложняется схема управления АЛУ(Алгоритм работы).Обычно применяется комбинация данных методов.

К аппаратным методам относятся:

1)выполнение операции сложения и сдвига позволяющие за 1 такт производить сдвиг информации сразу на несколько разрядов.

2)совмещение операций сложения и сдвига.

3)построение комбинационных схем множительных устройств (реализация табличного умножения).

Среди логических методов наиболее распространены методы позволяющие за один цикл умножения обработать сразу несколько разрядов множителя.

Структурная схема АЛУ для ускоренного умножения чисел в формате с фиксируемой запятой.

АЛУ вкл.

- Входной регистр множимого Рг1, -Регистры множителя Рг2 и Рг2’, -Сумматор для образования суммы частичных произведений,- РгА -для формирования частичного произведения ,-РгВ -для накопления суммы частичных произведений, -Рг См -регистр суммы, -Сч- счетчик циклов, - Т-тригер коррекции

Последовательность выполнения операции состоит из следующих частей:

1. Начальная установка.

2. Вычисление суммы частичных произведений.

3. Вывод результата.

Методы ускорения умножения.

Методы ускорения умножения делятся на аппаратурные и логические. Как те, так и другие требуют дополнительных затрат оборудования. При использовании аппаратурных методов дополнительные затраты оборудования прямо пропорциональны числу разрядов в операндах. Эти методы вызывают усложнение схемы АЛУ.

Дополнительные затраты оборудования при реализации логических методов ускорения умножения не зависят от разрядности операндов. Усложняется в основном схема АЛУ. В ЭВМ для ускорения умножения часто используется комбинации этих методов.

К аппаратурным методам ускорения умножения относятся ускорение выполнения операций сложения и сдвига, введение дополнительных цепей сдвига, позволяющих за один такт производить сдвиг информации в регистрах сразу на несколько разрядов, совмещение по времени операций сложения и сдвига, построение комбинационных схем множительных устройств, реализующих «табличное» умножение.

Среди логических методов наиболее распространены в настоящее время методы, позволяющие за один шаг умножения обработать несколько разрядов множителя.

Структура АЛУ для деления чисел с фиксированной точкой.

При делении чисел с фиксированной запятой сама операция сводится к операциям вычитания (сложения) и сдвига.

Деление реализуется двумя основными способами:

1. Деление с неподвижным делимым и сдвигаемым вправо делителем.

2. Деление с неподвижным делителем и сдвигаемым вправо делимым.

3. Деление с неподвижным делителем с восстановлением остатка.

Алгоритм деления аналогичен алгоритму деления уголком, используемом при ручном счете.

Z=X/Y

X – делимое. Обычно представляется двойным словом (содержит 2n или 2n-1 разрядов), Y – делитель,

Z – частное (содержит n или n-1 разряд).

Данная схема имеет 2 разновидности:

- Деление с неподвижным делителем с восстановлением остатка.

- Деление с неподвижным делителем без восстановления остатка.

1.1) Берутся модули от делимого и делителя. СчЦ (счетчик цикла) устанавливается в значение разрядности регистров.

1.2) Исходное значение частичного остатка делится равным старшим разрядам делимого двойной длины. Младшая и старшая часть делимого хранится в разных регистрах одинаковой длины.

1.3) Частичный остаток удваивается путем сдвига на 1 разряд влево. При этом в освободившийся при сдвиге младший разряд частичного остатка заносится очередная цифра делимого из разрядов младшей половины делимого (регистр 2 нулевой разряд).

1.4) Из сдвинутого частичного остатка вычитается делитель и анализируется знак результата вычитания. Если результат вычитания положителен, то очередная цифра частного равна 1, если результат вычитания отрицателен, то очередная цифра равна 0.

Данные этапы выполняются последовательно для получения всех цифр модуля частного.

1.5) Происходит вычисление знака частного (XOR).

Существует другой метод деления – деление без восстановления остатка.

Данные два способа отличаются последовательностью вычисления частного и остатка. В первом методе сначала вычислялось частное, потом вычислялся остаток, во втором методе одновременно вычислялся (на каждом цикле) и частное, и остаток.

Этапы алгоритма деления без восстановления остатка:

1) Берутся модули от делимого и делителя, в СчЦ (счетчик цикла) устанавливается значение разрядности регистров.

2) Исходное значение частичного остатка делается равным старшим разрядам делимого двойной длины. Младшая и старшая часть делимого содержатся в разных регистрах одинаковой длины.

3) Частичный остаток удваивается путем сдвига на 1 разряд влево. При этом в освобождающийся при сдвиге младший разряд заносится очередная цифра делимого.

4) Если остаток больше нуля, то из сдвинутого частичного остатка вычитается делитель; если остаток меньше нуля, то к сдвинутому частичному остатку прибавляется делитель.

5) Если результат вычитания больше нуля, то очередная цифра модуля частного равна 1; если результат вычитания меньше нуля, то очередная цифра модуля частного равна 0. Данные этапы выполняются до получения всех цифр модуля частного.

6) Определяется знак частного (XOR)

1. АЛУ для выполнения различных арифметических действий структурно почти идентичны, что позволяет реализовать как блочные, так и многофункциональные АЛУ.

2. Ускорение вычислений может достигаться алгоритмически (появление новых связей, изменение алгоритма работы) либо улучшением элементной базы (внедрение 2n, 4n разрядных устройств).

Операции десятичной арифметики.

Арифметические операции над десятичными числами (сложение, вычитание, умножение, деление) выполняются аналогично операциям над целыми двоичными числами. Основой АЛУ десятичной арифметики является сумматор двоично-десятичных кодов. Такой сумматор, как правило, строится на основе двоичного путем добавления некоторых цепей.

Рассмотрим, каким образом можно выполнить сложение двоично-десятичных кодов. Пусть необходимо сложить модули двух двоично-десятичных чисел X и Y. Первое слагаемое X преобразуем в код с избытком 6 (обозначим Х6), получаемый путем прибавления к каждой цифре X двоичного числа 6. Переход от X к Х6 изменяет все тетрады X так, что в каждой тетраде Х6 находится число 6 - 15.

Складывая Х6 и Y по правилам двоичного сложения, получаем результат Z'. В Z' одни тетрады совпадают, а другие не совпадают с тетрадами двоично-десятичной суммы Z.

Если результат сложения в i-м разряде X [i] + Y[i] + Р [i] >= 10, где Р [i] - десятичный перенос в i-й разряд, то i-я десятичная цифра Z [i] = X [i] + Y[i] + Р [i] – 10 и Р [i + 1] = 1, где Р [i + 1] - десятичный перенос в (i + 1)-й разряд. Для Z'[i] в этом случае получаем

Z'[i] = Х6[1] + У[i] +P[i] - 16= 6+ X[i] + Y[i] + Р[i] - 16 = Z[i].

При этом возникает перенос в (i+1)-ю тетраду.

Если 1-я десятичная цифра Z(i) должна получаться из X [i] + Y[i] + Р [i] < 10, то Z[i] = X [i] + У[i] + Р [i] и Р[i+1] = 0.

Для Z'(i) в этом случае получаем

Z’[i] =X6[i] + Y[i] + Р[i] = 6 + Х[i] + У[i] + Р[i] =Z[i] + 6.

Перенос в (i + 1)-ю тетраду здесь не возникает (Р[i+1] = 0), так как

Z' [i] < 16.

Таким образом, складывая Х6 и Y как двоичные числа, получаем Z'. В Z' тетрады, из которых возникал перенос, совпадают с тетрадами двоично-десятичного результата Z, а тетрады, из которых не было переноса при сложении, представлены с избытком 6. Для получения суммы Z необходимо откорректировать Z' путем уменьшения на 6 тех тетрад Z , из которых не было переноса при сложении Х6 и Y.

Вычитание числа 6 из тетрад, требующих коррекции, можно реализовать путем подсуммирования числа 10 с одновременным игнорированием переноса, возникающего при этом из тетрад. Если Z' [i] нуждается в коррекции, то Z' [i] = Z[i]+ 6. Поэтому Z'[i] + 10 >= 16, значит, после прибавления 10 из тетрады возникнет перенос, т. е. в тетраде останется (Z' [i] + 10)-16 = Z[i]-6.

Вычитание двоично-десятичных модулей X-Y осуществляется следующим образом.

Все разряды Y инвертируются, что дает дополнение каждой цифры Y до 15, при этом получается обратный код двоично-десятичного Y с избытком 6, обозначенный Уобр6. Затем, складывая X + Уобр6 и прибавляя 1 к младшему разряду, получаем Z. Результат Z' является положительным числом, если из старшей тетрады его возникает перенос, при этом Z' корректируется по тем же правилам, что и при сложении модулей.

Если из старшей тетрады 2' нет переноса, то получен отрицательный результат, представленный в дополнительном коде. В этом случае код Z' инвертируется и к нему прибавляется 1 младшего разряда. Новое Z' корректируется, при этом к тетрадам, из которых возникал перенос при получении (X + Уобр6 + 1), прибавляется 10, а к остальным не прибавляется.

Выполнение сложения и вычитания чисел со знаками сводится к выполнению сложения или вычитания модулей путем определения фактической выполняемой операции по знакам операндов и виду выполняемой операции. Знак результата определяется отдельно. Например, при X < 0 и Y < 0 вычитание X- Y заменяется вычитанием | Y | - | X |. Затем знак результата меняется на противоположный знаку (| Y | - | X |).

Двоично-десятичное умножениесводится к образованию и многократному сложению частичных двоично-десятичных произведений. Умножение двоично-десятичных чисел выполняется следующим образом:

1) сумма частичных произведений полагается равной нулю;

2) анализируется очередная цифра (тетрада) множителя, и множимое прибавляется к сумме частичных произведений столько раз, какова цифра множителя;

3) сумма частичных произведений сдвигается вправо на 1 тетраду, и повторяются действия, указанные в п. 2, пока все цифры множителя не будут обработаны.

Для ускорения умножения часто отдельно формируются кратные множимого 8Х, 4Х, 2Х и IX, при наличии которых уменьшается число сложений при выполнении п. 2.

Двоично-десятичное деление выполняется путем многократных вычитаний, подобно тому, как это делается при обычном делении.

Операции над числами с плавающей точкой.

Арифметические операции над числами с плавающей запятой более сложны, чем операции над числами с фиксированной запятой. Алгоритм сложения и вычитания чисел с плавающей запятой выглядит следующим образом:

Производится выравнивание порядков чисел. Порядок меньшего (по модулю) числа принимается равным порядку большего, а мантисса меньшего числа сдвигается вправо на число разрядов, равное разности порядков чисел.

Производится сложение (вычитание) мантисс, в результате чего получается мантисса суммы (разности).

Порядок результата принимается равным порядку большего числа.

Полученная сумма (разность) нормализуется.

Выравнивание порядков начинается с их сравнения. Мантисса числа с меньшим порядком при выравнивании сдвигается вправо на число разрядов, равное разности порядков.

Сложение (вычитание) мантисс производится по правилам сложения (вычитания) чисел с фиксированной запятой.

При умножении чисел с плавающей запятойпорядки сомножителей складываются, а мантиссы перемножаются. Произведение нормализуется, и ему присваивается знак плюс, если сомножители имеют одинаковые знаки, и знак минус, если знаки разные.

Если мантисса множимого или множителя равна 0, то произведению можно присвоить значение 0 без выполнения умножения мантисс. Если при суммировании порядков возникло переполнение и порядок отрицательный, то это означает, что произведение меньше минимального представляемого в машине числа, и в качестве результата операции может быть записан 0 без перемножения мантисс.

Если при суммировании порядков возникает переполнение и порядок положительный, может оказаться, что результат все-таки находится в диапазоне чисел, представляемых в машине, так как при умножении мантисс возможно нарушение нормализации вправо, и после нормализации мантиссы переполнение в порядке может исчезнуть.

При делении чисел с плавающей запятой мантисса частного равна частному от деления мантиссы делимого на мантиссу делителя, а порядок частного - разности порядков делимого и делителя. Частное нормализуется, и ему присваивается знак плюс, если делимое и делитель имеют одинаковые знаки, и знак минус, если разные.

Если делимое равно 0, то в частное может быть записан 0 без выполнения деления. Если при вычитании порядков образовалось переполнение с положительным знаком или если делитель равен 0, то деление не производится и формируется сигнал прерывания.

При делении нормализованных чисел с плавающей запятой может оказаться, что мантисса делимого больше мантиссы делителя, и мантисса частного образуется с переполнением. Для устранения этого явления перед делением мантисс нарушают нормализацию делителя сдвигом на разряд влево. Тогда нарушения нормализации частного влево не возникает.

Многофункциональные АЛУ.

По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

Устройство управления ЭМВ и ВС.

Устройство управления (УУ) управляет работой процессора, обеспечивая автоматическое выполнение команд программы. Выполнение команды процессором представляет собой последовательность следующих действий (иногда называемых машинными циклами):

- выборка команды из памяти и ее декодирование (дешифрация кода операции);

- формирование адреса следующей команды;

- формирование исполнительного адреса операнда и выборка его из памяти;

- исполнение операции и запись результата в память.

Для выполнения каждого машинного цикла необходим ряд управляющих сигналов, формируемых устройством управления.

В зависимости от способа формирования управляющих сигналов различают два основных типа УУ:

- аппаратные (с жесткой или схемной логикой);

- микропрограммные (с хранимой в памяти логикой).

В аппаратных УУ для каждой операции, задаваемой кодом операции команды, строится набор схем, которые в нужных тактах формируют соответствующие управляющие сигналы.

В УУ с микропрограммным управлением каждой операции соответствует набор микрокоманд, хранимых в памяти микрокоманд. Каждая микрокоманда несет информацию о микрооперациях, подлежащих выполнению в течение машинного такта и указания, какая микрокоманда должна быть выбрана из памяти следующей. Последовательность микрокоманд, выполняющая одну машинную команду или некоторую процедуру, образует микропрограмму.

Устройство управления с жесткой логикой.

Управляющие устройства с жесткой логикой представляют собой логические схемы, вырабатывающие распределенные во времени управляющие сигналы. В отличие от управляющих устройств с хранимой в памяти логикой в аппаратных УУ нельзя изменить логику работы без изменения их схемы. Типичная структурная схема управляемого автомата с жесткой логикой показана на рисунке 4.4.2.1. Её можно рассматривать в качестве автомата с конечным числом состояний (конечный автомат), который на каждом такте

Рисунок 4.4.2.1- Схема блока формирования сигналов управления

переходит из одного состояния в другое, определяемое содержимым регистра команды, кодами условий и внешними сигналами. Выходами такого автомата являются управляющие сигналы. Формируемая им последовательность операций задается физическими связями между логическими элементами.

В состав схемы входят регистр кода операции, являющейся частью регистра команд процессора, счетчик тактов, дешифратор тактов и дешифратор кода операции (Дешифратор КОП), а также логические схемы формирования управляющих сигналов. На счетчик тактов поступают сигналы от генератора тактовых импульсов (ГТИ). Состояние счетчика представляют собой номера тактов, изменяющие от 1 до m. Дешифратор тактов формирует на i-м выходе единичный сигнал при i-м состоянии счетчика тактов, т.е. во время i-го такта.

Принцип построения логических схем формирования управляющих сигналов поясняется на рисунке 4.4.2.2 На нем изображен фрагмент схемы, обеспечивающий выработку управляющих сигналов y1, y2 и y3 выполнения команды сложения на тактах T1,T2, T6.

В общем случае значения управляющих сигналов зависят еще от оповещающих сигналов U={u1, u2… un}, отражающих ход вычислительного процесса. Для реализации этих зависимостей логические элементы, представленные на рисунке 4.3.2.2, берутся многовходовыми и на них подаются требуемые сигналы логических условий.

Рисунок 4.4.2.2- Фрагмент логической схемы формирования управляющих сигналов

Сигналы y0 и yk (см. рисунок 4.3.2.1) обычно используются для определения моментов начала и окончания выполнения команд. С этой целью они используются для управления работой счетчика тактов. Управляющий сигнал y0 (Пуск) указывает на начало выполнения команды. Когда он установлен в 1, в конце каждого тактового цикла значение счетчика увеличивается на 1. Если же его значение становится равным 0, отсчет шагов прекращается. Сигнал yk (Останов) сбрасывает счетчик тактов в начальное состояние, обеспечивая начало нового цикла выборки команды.

Серьезным недостатком рассмотренных схем является одинаковое число тактов, необходимых для выполнения всех команд, значение которого выбирается по наиболее длинной команде. Это приводит к непроизводительным затратам времени и, как следствие, к уменьшению быстродействия процессора. Для устранения этого недостатка применяют УУ с переменным числом тактов, в котором используют счетчик тактов с изменяемым модулем счета. Для коротких команд используют счетчик с небольшим модулем счета и наоборот.

При реализации простой системы команд узлы устройства управления с жесткой логикой экономичны и позволяют обеспечить наибольшее быстродействие среди всех возможных методов построения УУ. Однако с возрастанием сложности системы команд усложнялись и схемы автоматов с жесткой логикой, при этом их быстродействие уменьшалось.

Принцип микропрограммного управления.

Альтернативой аппаратного способа реализации УУ является микропрограммное управление, согласно которому сигналы генерируются программой, подобной программе, написанной на машинном языке для ЭВМ. Этот принципиально иной подход был предложен английским ученым М. Уилксом в начале 50-х годов. Его называют принципом микропрограммного управления. Он позволяет преодолеть сложности реализации УУ с жесткой логикой. В основу принципа микропрограммного управления заложен тот факт, что каждой машинной команде соответствует уникальный код, называемый микрокомандой. Последовательность микрокоманд, реализующих машинную команду, образует микропрограмму. Микропрограммы размещаются в специальной управляющей памяти, называемой памятью микропрограмм. Выполнение команд в процессоре реализуется путем последовательного извлечения микрокоманд из памяти микропрограмм с последующей их дешифрацией для формирования управляющих сигналов, необходимых при выполнении конкретной команды.

Память ЭВМ. Назначение. Классификация. Основные

Компью́терная па́мять (устройство хранения информации, запоминающее устройство) — часть вычислительной машины, физическое устройство или среда для хранения данных, используемых в вычислениях, в течение определённого времени. Память, как и центральный процессор, является неизменной частью компьютера с 1940-х. Память в вычислительных устройствах имеет иерархическую структуру и обычно предполагает использование нескольких запоминающих устройств, имеющих различные характеристики.

КЛАССИФИКАЦИЯ:

|

из

5.00

|

Обсуждение в статье: Фоннеймановская архитектура ВМ |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы