|

Главная |

Представление данных в модели

|

из

5.00

|

МГЭУ им. А.Д. Сахарова

Минск

Содержание

Практическая работа № 1. Знакомство с моделью учебной ЭВМ... 3

Практическая работа № 2. Архитектура ЭВМ и система команд.. 22

Практическая работа № 3. Команды управления и ветвления.. 33

Практическая работа № 4. Применение косвенной адресации.. 39

Практическая работа № 5. Подпрограммы и стек.. 44

Практическая работа № 6. Командный цикл процессора.. 50

Практическая работа № 7. Программирование внешних устройств 56

Практическая работа № 8. Знакомство с организацией кэш-памяти учебной ЭВМ... 71

Контрольная работа и методические указания по выполнению 80

Требования к оформлению отчета по практической или лабораторной работе.. 81

Аппаратные средства

Информационных технологий

Практическая работа № 1. Знакомство с моделью учебной ЭВМ

Цель работы:

1. Знакомство с архитектурой модели учебной ЭВМ.

2. Изучение системы команд модельной ЭВМ, действиями основных классов команд и способов адресации.

3. Освоение программы реализующей модель учебной ЭВМ. Знакомство с интерфейсом пользователя модели ЭВМ, методами ввода и отладки программы.

4. Изучение процесса программирования на модели учебной ЭВМ.

Теоретические сведения:

Описание архитектуры учебной ЭВМ

Современные процессоры и операционные системы — не слишком благоприятная среда для начального этапа изучения архитектуры ЭВМ.

Одним из решений этой проблемы может быть создание программных моделей учебных ЭВМ, которые, с одной стороны, достаточно просты, чтобы обучаемый мог освоить базовые понятия архитектуры (система команд, командный цикл, способы адресации, уровни памяти, способы взаимодействия процессора с памятью и внешними устройствами), с другой стороны — архитектурные особенности модели должны соответствовать тенденциям развития современных ЭВМ.

Программная модель позволяет реализовать доступ к различным элементам ЭВМ, обеспечивая удобство и наглядность. С другой стороны, модель позволяет игнорировать те особенности работы реальной ЭВМ, которые на данном уровне рассмотрения не являются существенными.

Структура ЭВМ

Моделируемая ЭВМ включает:

- процессор;

- блок регистров общего назначения;

- оперативную память (ОЗУ);

- сверхоперативную память (СОЗУ) (кэш-память);

- устройства ввода (УВв);

- устройства вывода (УВыв).

Процессор, в свою очередь, состоит из:

- центрального устройства управления (УУ);

- арифметического устройства (АУ);

- блока системных регистров (CR, PC, SP и др.).

Структурная схема ЭВМ показана на рисунке 1.

Рис. 1. Общая структура учебной ЭВМ

В ячейках ОЗУ хранятся команды и данные. Емкость ОЗУ составляет 1000 ячеек. По сигналу MWr выполняется запись содержимого регистра данных (MDR) в ячейку памяти с адресом, указанным в регистре адреса (MAR). По сигналу MRd происходит считывание — содержимое ячейки памяти с адресом, содержащимся в MAR, передается в MDR.

Блок регистров общего назначения (РОН) с прямой адресацией содержит десять регистров общего назначения R0—R9. Доступ к ним осуществляется (аналогично доступу к ОЗУ) через регистры RAR и RDR.

АУ осуществляет выполнение одной из арифметических операций, определяемой кодом операции (СОР), над содержимым аккумулятора (Асc) и регистра операнда (DR). Результат операции всегда помещается в Асc. При завершении выполнения операции АУ вырабатывает сигналы признаков результата:

- Z (равен 1, если результат равен нулю);

- S (равен 1, если результат отрицателен);

- OV (равен 1, если при выполнении операции произошло переполнение разрядной сетки). В случаях, когда эти условия не выполняются, соответствующие сигналы имеют нулевое значение.

В модели ЭВМ предусмотрены внешние устройства двух типов.

Во-первых, это регистры IR и OR, которые могут обмениваться с аккумулятором с помощью безадресных команд in (Асс := IR) и out (OR := Асс).

Во-вторых, это набор моделей внешних устройств, которые могут подключаться к системе и взаимодействовать с ней в соответствии с заложенными в моделях алгоритмами. Каждое внешнее устройство имеет ряд программно-доступных регистров, может иметь собственный обозреватель (окно видимых элементов). Подробнее эти внешние устройства описаны в разделе описания программы моделирующей работу ЭВМ.

УУ осуществляет выборку команд из ОЗУ в последовательности, определяемой естественным порядком выполнения команд (т. е. в порядке возрастания адресов команд в ОЗУ) или командами передачи управления; выборку из ОЗУ операндов, задаваемых адресами команды; инициирование выполнения операции, предписанной командой; останов или переход к выполнению следующей команды.

В качестве сверхоперативной памяти может подключаться модель кэш-памяти.

В состав УУ ЭВМ входят:

· PC — счетчик адреса команды, содержащий адрес текущей команды;

· CR — регистр команды, содержащий код команды;

· RB — регистр базового адреса, содержащий базовый адрес;

· SP — указатель стека, содержащий адрес верхушки стека;

· RA — регистр адреса, содержащий исполнительный адрес при косвенной адресации.

Регистры данных, такие как : - Асc, DR, IR, OR, CR и все ячейки ОЗУ и РОН имеют длину 6 десятичных разрядов, а регистры команд: - PC, SP, RA и RB — 3 разряда.

Представление данных в модели

Данные в ЭВМ представляются в формате, показанном на рис. 2. Это целые десятичные числа, изменяющиеся в диапазоне "-99 999... +99 999", содержащие знак и 5 десятичных цифр.

Рис. 2. Формат десятичных данных учебной ЭВМ

Старший разряд слова данных используется для кодирования знака: плюс (+) изображается как 0, минус (-) — как 1. Если результат арифметической операции выходит за пределы указанного диапазона, то говорят, что произошло переполнение разрядной сетки. АЛУ в этом случае вырабатывает сигнал переполнения OV = 1. Результатом операции деления является целая часть частного. Деление на ноль вызывает переполнение.

Система команд

При рассмотрении системы команд ЭВМ обычно анализируют три аспекта: форматы, способы адресации и систему операций.

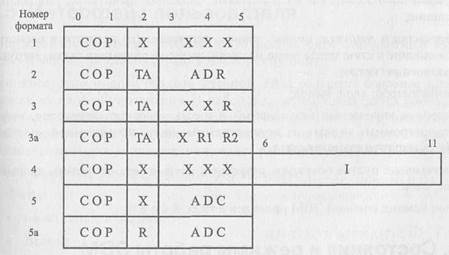

Форматы команд

Большинство команд учебной ЭВМ являются одноадресными или безадресными, длиной в одно машинное слово (6 разрядов). Исключение составляют двухсловные команды с непосредственной адресацией и команда mov, являющаяся двухадресной.

В форматах команд выделяется три поля:

· два старших разряда [0:1] определяют код операции СОР;

· разряд 2 может определять тип адресации (в одном случае (формат 5а) он определяет номер регистра);

· разряды [3:5] могут определять прямой или косвенный адрес памяти, номер регистра (в команде mov номера двух регистров), адрес перехода или короткий непосредственный операнд. В двухсловных командах непосредственный операнд занимает поле [6:11].

Полный список форматов команд показан на рис. 3, где приняты следующие обозначения:

· СОР — код операции;

· ADR — адрес операнда в памяти;

· ADC — адрес перехода;

· I — непосредственный операнд;

· R, Rl, R2 — номер регистра; П ТА — тип адресации;

· X — разряд не используется.

Рис. 3. Форматы команд учебной ЭВМ

Способы адресации

В ЭВМ принято различать пять основных способов адресации:

- прямая,

- косвенная,

- непосредственная,

- относительная,

- безадресная.

Каждый способ адресации имеет разновидности. В модели учебной ЭВМ реализованы семь способов адресации, приведенные в табл. 1.

Таблица 1.Адресация в командах учебной ЭВМ

| Код ТА | Тип адресации | Исполнительный адрес |

| Прямая (регистровая) | ADR (R) | |

| Непосредственная | — | |

| Косвенная | O3Y(ADR)[3:5] | |

| Относительная | ADR + RB | |

| Косвенно-регистровая | POH(R)[3:5] | |

| Индексная с постинкрементом | POH(R)[3:5], R:=R + 1 | |

| Индексная с преддекрементом | R:=R-1,POH(R)[3:5] |

Система операций

Система команд учебной ЭВМ включает команды следующих классов:

· арифметико-логические и специальные:

o сложение,

o вычитание,

o умножение,

o деление;

· пересылки и загрузки:

o чтение,

o запись,

o пересылка (из регистра в регистр),

o помещение в стек,

o извлечение из стека,

o загрузка указателя стека,

o загрузка базового регистра;

· ввода/вывода:

o ввод,

o вывод;

· передачи управления:

o Безусловный переход

o шесть команд условного перехода,

o вызов подпрограммы,

o возврат из подпрограммы,

o цикл,

o программное прерывание,

o возврат из прерывания;

· системные:

o пустая операция,

o разрешить прерывание,

o запретить прерывание,

o стоп.

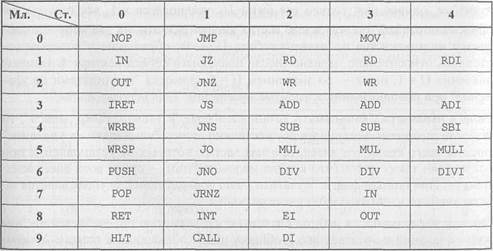

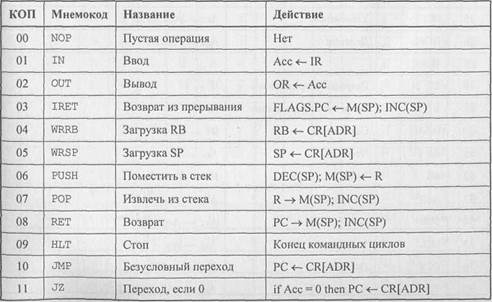

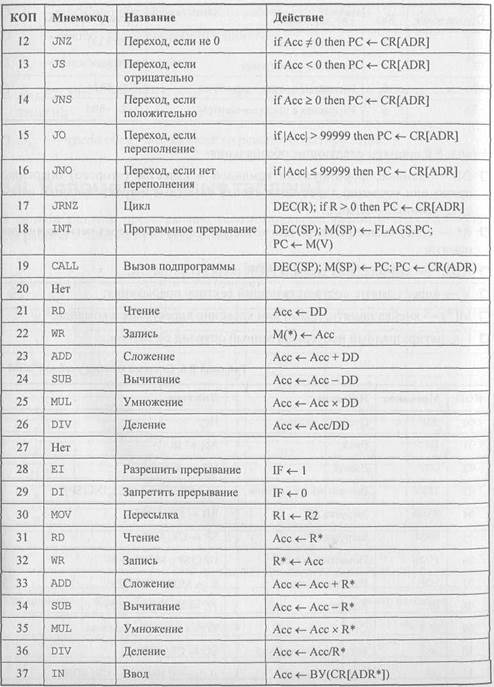

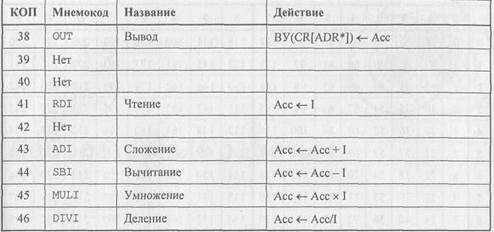

Список команд учебной ЭВМ приведен в табл. 2 и 3.

Таблица 2. Таблица команд учебной ЭВМ

В таблице 3 приняты следующие обозначения:

· DD — данные, формируемые командой в качестве (второго) операнда: прямо или косвенно адресуемая ячейка памяти или трехразрядный непосредственный операнд;

· R* — содержимое регистра или косвенно адресуемая через регистр ячейка памяти;

· ADR* — два младших разряда ADR поля регистра CR;

· V — адрес памяти, соответствующий вектору прерывания;

· М(*) — ячейка памяти, прямо или косвенно адресуемая в команде;

· I — пятиразрядный непосредственный операнд со знаком.

Таблица 3. Система команд учебной ЭВМ

Таблица 3 (продолжение)

|

|

из

5.00

|

Обсуждение в статье: Представление данных в модели |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы