|

Главная |

Арифметические устройства

|

из

5.00

|

Двоичный сумматор(SM - SuМ - сумма) - это комбинационное цифровое устройство, предназначенное для арифметического сложения чисел, представленных в виде двоичных кодов. Сумматоры используются в операциях суммирования и вычитания чисел, а также составляют основу умножения и деления чисел.

По принципу обработки разрядов чисел различают последовательные и параллельные сумматоры. В последовательных сумматорах сложение чисел осуществляется поразрядно (последовательно), в параллельных – все разряды обрабатываются одновременно.

По числу выводов различают полусумматоры, одноразрядные сумматоры и многоразрядные сумматоры.

Полусумматор (HS - HalfSum - полусумма), - это устройство, производящее сложение двух одноразрядных двоичных чисел:

0+0=0;

0+1=1+0=1;

1+1=10.

Сложение двух одноразрядных двоичных чисел можно отразить таблицей сложения (таблицей истинности), в которой А и В - значения входных чисел, S - значение результата суммирования и Р - значение переноса в старший разряд (рис. 1,а). Работа устройства, реализующего эту таблицу истинности (полусумматора), описывается уравнениями: S = A  B (исключающее ИЛИ), P=A·B (И) и имеет логическую структуру, изображенную на рис. 1,б.

B (исключающее ИЛИ), P=A·B (И) и имеет логическую структуру, изображенную на рис. 1,б.

| A | B | P | S |

а

б

Рис. 1

Поскольку полусумматор имеет только два входа, он может использоваться для суммирования лишь в младшем разряде.

Полный сумматор.При суммировании двух многоразрядных чисел для каждого разряда (кроме младшего) необходимо использовать устройство, имеющее дополнительный вход переноса. Такое устройство называют полным сумматором.

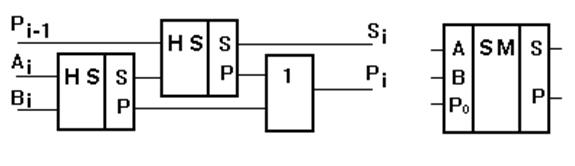

Полный одноразрядный сумматор суммирует три одноразрядных двоичных числа: два слагаемых Ai, Bi и перенос, поступивший из младшего разряда Pi-1. Полный одноразрядный сумматор можно построить из двух полусумматоров HS и логического элемента ИЛИ (рис. 2). Один полусумматор используется для сложения i-го разряда двоичных чисел, а второй полусумматор складывает результат первого полусумматора с переносом из (i-1) разряда.

а

а

| Входы | Выходы | |||

| Ai | Bi | Pi-1 | Si | Pi |

б

Рис. 2

Для сложения двух многоразрядных двоичных чисел используют многоразрядные сумматоры, представляющие собой в простейшем виде последовательное соединение одноразрядных сумматоров (рис. 3,а). Сигнал переноса последовательно передается с выхода предыдущего разряда сумматора на вход переноса следующего разряда. Рассмотренный сумматор называется параллельным сумматором.

а б

Рис. 3

В виде интегральных микросхем выпускаются одноразрядные, двухразрядные и четырехразрядные двоичные сумматоры. В корпусе микросхемы К155ИМ3 четыре полных одноразрядных сумматора объединены в схему четырехразрядного сумматора (рис. 3,б). С целью наращивания разрядности суммируемых чисел микросхемы соединяют последовательно, для чего выход переноса Р непосредственно соединяют со входом переноса Р0 микросхем, принадлежащим более высоким разрядам. У микросхемы, суммирующей младшие разряды чисел, вход переноса Р0 следует соединять с общим проводом.

Вычитание двух чисел. Рассмотренные сумматоры можно использовать для вычитания двоичных чисел. В этом случае операция вычитания заменяется сложением уменьшаемого А с вычитаемым В (Впр=В4В3В2В1), представленным в дополнительном коде. Дополнительный код Вдоп образуется из обратного (инверсного) кода (  ) добавлением к нему единицы (Вдоп=Вобр+1).

) добавлением к нему единицы (Вдоп=Вобр+1).

Очевидно, для четырехразрядных чисел, записанных в этих кодах, справедливы равенства

Впр+ Вобр=1111;

Впр+ Вдоп= Впр+ Вобр+1=1111+1=10000;

Впр=10000 – Вдоп=10000 – Вобр – 1.

Следовательно, операцию вычитания можно представить в виде

Апр – Впр = Апр + Вдоп – 10000 или Апр – Впр = Апр + Вобр+1 – 10000.

Пример.

10 – 7 = 3;

Апр=1010,

Впр=0111, Вобр=1000, Вдоп=1000+0001=1001,

Апр – Впр = Апр + Вдоп – 10000=1010 + 1001 – 10000=0011.

Следует отметить, что если А > В, то ответ формируется в прямом коде, при этом образуется 1 переноса в более старший разряд, при А < В ответ формируется в обратном коде и 1 переноса в более старший разряд не образуется.

На рисунке 4 представлена схема вычитателя на базе сумматора. Наличие или отсутствие логической 1 на выходе переноса Р, используют для распознавания знака результата, образуя циклический перенос, т. е. соединяя выход переноса Р со входом переноса Р0. Когда сигнал переноса соответствует логической 1, то на выходах S4S3S2S1 формируется результат в прямом коде, при нулевом значении сигнала переноса результат формируется в обратном коде, который несложно преобразовать в прямой.

Рис. 4

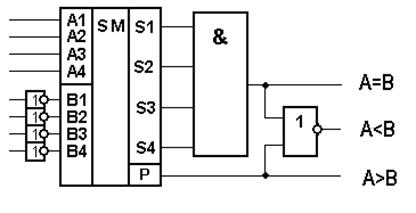

Цифровой компаратор. Цифровые компараторы выполняют сравнение двух двоичных чисел. Они могут определять равенство двух двоичных чисел А и В с одинаковым количеством разрядов либо вид неравенства А>В или А<В.

Цифровой компаратор можно построить на сумматоре, подавая на один суммирующий вход прямой код числа А, на другой - инверсный код числа В (рис. 5). Легко убедиться, что при А=Вна выходах S4S3S2S1 формируются логические единицы, подключив к ним элемент И, получим 1 на его выходе. При A>Bединица формируется на выходе переноса Р. Для определения неравенства А<В к выходам элемента И и переноса Р подключен элемент ИЛИ-НЕ. При А<В на выходах элемента И и переноса Р будут логические 0, а на выходе элемента ИЛИ-НЕ – 1.

Рис. 5

Контрольные вопросы.

1. Что называется полусумматором?

2. Опишите принцип действия полусумматора.

3. Что называется полным одноразрядным сумматором?

4. Опишите принцип действия полного одноразрядного сумматора.

5. Опишите структуру и принцип действия многоразрядного сумматора.

6. Как с помощь сумматора осуществляется операция вычитания?

7. Как с помощь сумматора осуществляется сравнение двух двоичных чисел?

Лабораторная работа №6.Изучение четырехразрядного параллельного сумматора

Цель работы.Изучение устройства и принципа действия четырехразрядного параллельного сумматора.

Задание.

1. Провести исследование работы четырехразрядного параллельного сумматора. В процессе исследования провести сложение двоичных чисел указанных преподавателем. Полученные результаты занести в таблицу 1. Провести проверку путем перевода слагаемых и суммы в десятичную систему.

Таблица 1.

| А(2) | В(2) | S(16) | S(2) | А(10)+В(10)=S(10) | |

| P (HL1) | HG1 | ||||

2. Провести вычитание двоичных чисел указанных преподавателем, заменив его сложением прямого кода уменьшаемого с дополнительным кодом вычитаемого. Полученные результаты занести в таблицу 2. Провести проверку путем перевода уменьшаемого, вычитаемого и разности в десятичную систему.

Таблица 2.

| А(2) | В(2) | Bобр | Вдоп | S(16) | S(2) | А(10)+В(10)=S(10) | |

| P (HL1) | HG1 | ||||||

3. Провести сравнение двоичных чисел указанных преподавателем. Полученные результаты занести в таблицу 3. Провести проверку путем перевода двоичных чисел в десятичную систему.

Таблица 3.

| А(2) | В(2) | Bобр | P (HL1) | HG1 | >, <, = | А(10) ? В(10) |

| А … В | ||||||

| А … В | ||||||

| А … В | ||||||

| А … В | ||||||

| А … В | ||||||

| А … В | ||||||

| А … В |

Указания по выполнению лабораторной работы.

Работа выполняется на универсальном стенде с использованием платы П3 и технологической карты III-3.

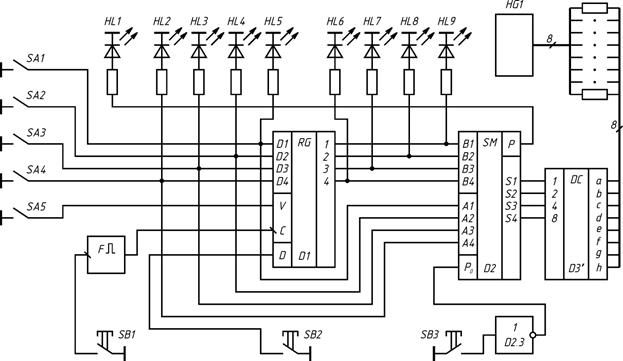

Рис. 6. Схема к карте III-3.

Карта III-3 (рис. 6) предназначена для исследования работы сумматора двух четырехразрядных двоичных чисел на микросхеме К155ИМ3 (D2). Для задания двух четырехразрядных слагаемых используются тумблеры SA4 – SA1 (слагаемое А) и регистр D1 (слагаемое В). Ввод слагаемого В в регистр может осуществляться как в параллельном коде с тумблеров SA4 – SA1 (тумблер SA5 должен находиться в верхнем положении), так и в последовательном с кнопки SB2 (SA5 - в нижнем положении) (см. л.р. №3). Импульс записи задается кнопкой SB2.

Индикация слагаемых осуществляется индикаторами HL2 – HL5 и HL6 – HL9. Сумма в четырех первых разрядах дешифруется в блоке индикации и высвечивается в виде шестнадцатеричного числа на семисегментном индикаторе HG1. Сигнал переноса P в старший (пятый) разряд подается на индикатор HL1. Таким образом, сигнал переноса P также является 0 или 1 в старшем (втором) разряде шестнадцатеричного числа суммы, а число на индикаторе HG1 – числом в младшем (первом) разряде.

Замену вычитания двоичных чисел сложением на стенде можно проводить двумя способами.

1-й способ. Записать в регистр дополнительный код вычитаемого, тумблерами SA4 – SA1 набрать прямой код уменьшаемого. Индикатор HG1 покажет результат вычитания в виде шестнадцатеричного числа. Сигнал на выходе переноса Р (индикатор HL1) не учитывается.

2-й способ. Записать в регистр обратный код вычитаемого, тумблерами SA4 – SA1 набрать прямой код уменьшаемого. Недостающая 1 прибавляется сигналом на входе переноса Р0 путем нажатия кнопки. Сигнал на вход переноса Р0 подается через инвертор D2.3 (при отпущенной кнопке SB3 Р0=0, при нажатой Р0=1).

Для сравнения двух двоичных чисел в регистр записать обратный код числа В и тумблерами SA4 – SA1 набрать прямой код числа А. При А=В индикатор HG1 покажет шестнадцатеричное число F (S=11112). При А>В загорится индикатор HL1 (Р=1). Во всех остальных случаях А<В.

Техническое описание стенда универсального ОАВТ

Стенд предназначен для выполнения лабораторных работ по электронике.

На передней (наклонной) панели стенда установлены разъем X1, тумблеры (SA1 – SA5) и кнопки (SB1 – SB3) ввода информации и задания режимов работы, исследуемых устройств, а так же светодиодный дисплей. Разъем X1 предназначен для подключения сменных плат с исследуемыми устройствами.

Переключатели SA1 – SA4, SB2 и SB3 предназначены для подачи логических сигналов с уровнями «0» (соответствующий вывод замкнут на общий провод) или «1» (вывод – на +5В). Тумблер SA5 подключается всеми своими выводами к разъему и поэтому может использоваться в качестве переключателя «двух сигналов в одну линию» или, наоборот, «одного сигнала на два направления». Кнопка SB1 подключена к схеме защиты от «дребезга» на триггере. С помощью этой кнопки формируется одиночный импульс с крутыми фронтами, необходимый для нормальной работы исследуемых триггеров, регистров и счетчиков. При нажатии SB1 на соответствующем контакте разъема X1 появляется логический 0, а при отпускании – логическая 1. Этот блок на схемах обозначается как формирователь одиночного импульса (F  ).

).

Светодиодный дисплей служит для индикации режимов работы, а также входной и выходной информации исследуемых устройств. Дисплей состоит из девяти светодиодов HL1 – HL9, позволяющих индицировать в 9 разрядах уровни логической «1» (светодиод светится) и логического «0» (не светится), и семисегментного индикатора HG1 для индикации числа в десятичном или шестнадцатеричном кодах.

|

из

5.00

|

Обсуждение в статье: Арифметические устройства |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы