|

Главная |

Выбор и обоснование направления проектирования

|

из

5.00

|

В результате обзора широкого спектра литературы и интернет источников, были найдены аналоги устройства, которые выполняют схожие задачи. Практически все устройства схожи с техническим заданием, но не до конца удовлетворяют его требованиям. Проблемой также стало отсутствие, в большинстве случаев, детальной информации по найденным аналогам, позволяющей использовать их проектировании необходимого устройства.

Транзитивный метод физического кодирования сигнала Манчестер-2 (Manchester code, также за рубежом Phase Encoding или PE) на данный момент один из самых распространенных в различных САУ и ЛВС. Так, например, Манчестер-2 применятся в стандартах сетевых протоколов Ethernet, Token Ring, MIL-STD-1553B(ГОСТ. 52070-2003), MIL-STD-1760 и многих других, применяемых в различных областях от построения коммерческих локальных сетей, до бортовых САУ в авиации и судостроении. Такое широкое применение Манчестерского кодирования обуславливает довольно большое количество электронных кодирующих устройств, в частности, на западе выпускают ряд КМДП монолитных кодеров/декодеров Манчестера(CMOS Manchester Encoder/Decoder) : серий 3D7501, ACT-15530, а также HI-15530, HD-15530, HD-15531, СТ-10894 и другие. В России разнообразие не столь велико, удалось найти информацию лишь о КМДП ИС К588ВГ3 и К588ВГ6, созданных ещё в конце 80-х годов. Ниже, на рисунке 1.1, для ознакомления показаны условное графическое представление К588ВГ3.

Рисунок 1.1 – Условные графические представления К588ВГ3

Но ни одна из названных БИС не удовлетворяет условиям технического задания - все имеют недостаточный диапазон тактовых частот: для микросхем серии 3D7501, предназначенных для работы в сетевых картах, он доходит до 50 МГц, а для ACT15530, HI-15530, К588ВГ3 и К588ВГ6 предназначенных для работы в сетях протокола MIL-STD-1553, всего лишь до 1,25 МГц. Остальные существенные параметры К588ВГ3 приведены в таблице 1.

Кроме того, практически все упомянутые ИС кодируют биполярный Манчестер-2, проектируемое же устройство, согласно техническому заданию кодирует униполярную разновидность Манчестера-2.

Таблица 1 – Электрические параметры К588ВГ3, КР588ВГ3

| Номинальное напряжение питания | 5 В ± 5% |

| Выходное напряжение низкого уровня | 0,4 В |

| Выходное напряжение высокого уровня | (Uп – 0,4) В |

| Ток потребления | ≤ 0,1 мА |

| Время задержки распространения сигнала (от входа 10 до выхода 36) | ≤ 80 нс |

| Максимальная емкость нагрузки | 100 пФ |

| Частота работы канала | 1,25 МГц |

Однако причиной невысокой, по современным меркам, частоты работы канала является не принципиальный изъян используемых в этих БИС принципов кодирования, а не достаточная скорость работы элементной базы. Таким образом, используя более быстрые компоненты, можно достичь необходимой тактовой частоты без изменения схемы работы этих устройств. В этом ключе, их несомненно можно рассматривать как аналоги при разработке курсового проекта. По зарубежным ИС не удалось найти электронных принципиальных и элементных схем. Поэтому проанализируем отечественную БИС К588ВГ3, которая, в целом, идентична HI-15530 (не исключаю возможности, что К588ВГ3 была напрямую скопирована с зарубежных образцов, в виду небольшого отставания СССР в области компьютерных технологий в те годы и внедрения в производство стандарта сетевых протоколов ГОСТ 26765.52-87 (MIL-STD-1553)).

|

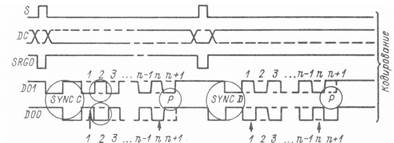

Рисунок 1.2 – Структура и принципиальная временная диаграмма работы кодера К588ВГ3

В состав кодера (CD) БИС КДК входят:

DIV 6 — делитель на 6, используемый для получения из частоты синхронизации декодера (12f) частоты синхронизации кодера (2f);

DIV 2 — делитель на 2, используемый для получения из частоты синхронизации кодера 2f частоты приема данных в кодер (1f);

CDM — кодер манчестерского кода;

СТ2 — счетчик числа передаваемых в слове битов.

Для нас наиболее важен кодер, находящийся в блоке CDM, остальные части ИС К588ВГ3 выполняют действия, в которых, согласно техническому заданию, нет необходимости.

В таблице 2 описаны выводы БИС кодера.

Временная диаграмма, поясняющая общие принципы использования БИС КДК, приведена на рисунке 1.3. При передаче строом SRGO производится запись слов, подлежащих кодированию, во внешний параллельно-последовательный регистр, данные из которого в последовательном коде поступают на вход DI по синхроимпульсам С1. При приеме информации из МК стробом SRGI может выбираться внешний последовательно-параллельный регистр, используемый для накопления декодированных данных, поступающих с выхода DO по синхроимпульсам СО в последовательном коде. Формирование сигналов SRGI и SRGO производится внешней схемой на основе сигналов TD и GD (выходы синхронизации приема/передачи слова).

При передаче кодер в зависимости от уровня сигнала на входе DC автоматически вырабатывает нужный синхроимпульс SYNC С или SYNC D и вставляет бит четности (Р). Согласование работы кодера с оконечным устройством осуществляется сигналами запуска передачи S, запрета на выдачу очередного слова ST и строба выдачи слов CD .

Таблица 2 –Описание выводов БИС кодера К588ВГ3

| Обознач. | Номер контакта | Назначение вывода |

| DI0, DI1 | 12, 13 | Униполярные фазоманипулированные инверсные входы «нуля» и «единицы» декодера (прямые) |

| DO0, DO1 | 26, 29 | Униполярные фазоманипулированные выходы «нуля» и «единицы» кодера (инверсные) |

| FO | 24 | Выход частоты синхронизации кодера (2 МГц) |

| С I | 36 | Выход тактовой частоты приема кодера (1 МГц) |

| MR | 22 | Вход общего сброса КДК |

| DC | 32 | Вход задания типа генерируемого синхроимпульса (SYNC D или SYNC С) |

| S | 34 | Вход запуска кодера |

| ST | 28 | Вход разрешения выдачи биполярного кода |

| PS | 33 | Вход задания полярности контрольного бита шифратора кодера |

| F | 39 | Вход делителя на шесть (12 МГц) |

Рассмотрим организацию непосредственно кодера Манчестерского кода, обозначенного на схеме аббревиатурой CDM. На рисунке 4 представлена его функциональная схема вместе с другими блоками, работающими в кодере К588ВГ.

Перед тем как попасть непосредственно на шифратор информация проходит через счётчик битов СТ2, (показан на рисунке 3), который сравнивает код на входах С0 – С4 с числом тактов, в течение которого принимается слово, причёмподсчет битов ведется по модулю п+4 (n – число битов), так как слово включает синхроимпульс и бит четности. Также перед шифратором находятся счетчики/делители, организованные по обычной схеме и реализуемые на основе одного (Т6) и трех ( T 7— T 9) триггеров (соответственно DIV 2 и DIV 6 – показан только на рисунке 3).

Схема шифратора (построена на триггерах Т10—Т16) подстраивает фазу передаваемых сигналов к частоте 2f, принимаемой по входу FI , и синхрочастотой С I стробирует ввод данных с входа DI ; код «Манчестер-2» выдается на выходы DO 0, DO 1. Сигнал ST заведен на выходные элементы, стробирующие выдачу информации. Триггер Т10 включен по схеме счетчика и накапливает сумму передаваемого кода по четности или нечетности в зависимости от полярности сигнала PS .

Несложно заметить, что данная схема, как и другие найденные аналоги, избыточна и чрезмерно сложна, по сравнению с устройством, которое необходимо разработать по техническому заданию.

Рисунок 1.3 – Функциональная схема кодирующей части К588ВГ3

Это объясняется тем, что эти БИС являются не просто кодерами Манчестера-2, полноценными блоками бита/слова входящими в состав любого терминала САУ выполняя функции шифрации/дешифрации информации в формате слов определенных стандартом, формирует синхроимпульсы, генерирует бит четности, обнаруживает при приеме ошибки кода и четности слова. Поэтому эффективней самостоятельно создать кодирующую схему, чем вычленять необходимые компоненты из блока CDM БИС КДК К588ВГ3.

Для этого подробней рассмотрим суть Манчестерского кодирования. В Манчестерском коде для кодирования единиц и нулей используется перепад сигнала, то есть фронт импульса. Каждый такт делится на две части. Информация кодируется перепадами потенциала, происходящими в середине каждого такта. Единица кодируется перепадом от низкого уровня сигнала к высокому, а ноль – обратным перепадом (хотя существует стандарт Манчестера-2, где наоборот единица кодируется переходом от высокого к низкому уровню, а ноль - соответственно от низкого к высокому). В начале каждого такта может происходить служебный перепад сигнала, если нужно представить несколько единиц или нулей подряд. Графически это представлено на рисунке 1.4.

Рисунок 1.4 – Представление сигнала в коде Манчестер-2

Так как сигнал изменяется по большей мере один раз за такт передачи одного бита данных, то манчестерский код обладает хорошими самосинхронизирующими свойствами. У него нет постоянной составляющей, а основная гармоника в худшем случае (при передаче последовательностей нулей и единиц) имеет частоту N Гц, а в лучшем (при передаче чередующихся единиц и нулей) – N/2 Гц. Поскольку отсутствие высокого или низкого уровня в течение всего интервала бита недопустимо, появление таких ситуаций может свидетельствовать об ошибке. Ложное декодирование («1» →«0» или «0» → «1») в манчестерском коде может произойти только тогда, когда из-за помехи инверсия логических уровней будет иметь место в каждой половине интервала одного бита, однако вероятность одновременной инверсии фазы в пределах одного бита невелика.

Из всего вышесказанного можно прийти к следующим выводам:

1. Чтобы преобразовать последовательный двоичный код (он представляет собой потенциальный код, где единица кодируется высоким уровнем сигнала, а ноль низким уровнем сигнала, причём состояния меняются на границе тактов) в Манчестер-2 кодер должен выполнять 4 типа операций:

а) При низком уровне в такте входящего кода (кодирование логического нуля), создать в исходящем коде перепад с высокого уровня на низкий в середине такта;

б) При высоком уровне в такте входящего кода (кодирование логического единицы), создать в исходящем коде перепад с низкого уровня на высокий в середине такта;

в) При кодировании двух и более подряд идущих логических нулей, обеспечить подъём сигнала с нижнего на верхний уровень на границе тактов (чтобы на следующем такте можно было выполнить операцию а));

г) При кодировании двух и более подряд идущих логических единиц, обеспечить переход сигнала с верхнего на нижний уровень на границе тактов (чтобы на следующем такте можно было выполнить операцию б));

2. Кроме сигнала последовательного двоичного кода для кодирования Манчестера-2 необходимо два вида синхросигнала:

а) Синхросигнал, синхроимпульсы в котором приходятся на начало каждого такта. Обозначим его как SYNC B (от англ. сокращения SYNC – synchronizing signal (синхронизирующий сигнал) и B – boundary (граница));

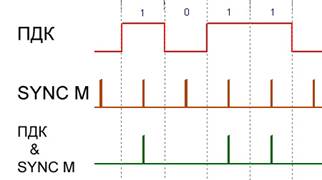

б) Синхросигнал, синхроимпульсы в котором приходятся на середину каждого такта. Обозначим его как SYNC M (от англ. M – middle (середина)).

Согласно техническому заданию синхросигналы внешние, что существенно упрощает разработку устройства, в виду избавления от необходимости проектировать генератор синхросигнала и решать проблему с подстройкой синхрочастоты.

Итак, определив конкретный круг задач, приступим непосредственно к созданию функциональной схемы проектируемого устройства. Начнём проектировать «с конца», т.е. с конечных элементов устройства. Очевидно, что внутри устройства логические элементы будут работать на кратковременных импульсах, однако сигнал выходящий из устройства в коде Манчестер-2, должен обладать высоким уровнем в течении необходимого по протоколу кода времени (такт или полтакта). Следовательно, надо использовать цифровое устройство способное при получении кратковременного импульса на вход подавать длительный сигнал на выход. В качестве такого устройства используем асинхронный RS-триггер.

Асинхронного RS-триггер обладает двумя информационными входами: S – По которому производится установка триггера в состояние логической «1» и R - по которому производится установка триггера в состояние логического «0». Следовательно, на вход S мы будем подавать сигналы, соответствующие подъему сигнала в Манчестерском коде с низкого уровня на высокий. А так как такой подъём происходит в Манчестерском коде либо при кодировании логической единицы (тогда он происходит в середине такта), либо при кодировании двух и более нолей расположенных непосредственно друг за другом (тогда в начале такта), то на вход S будет работать блок элементов, формирующий именно эти сигналы. И соответственно для информационного входа R мы создадим структуры формирующие сигналы, соответствующие переходу Манчестерского кода с высокого уровня на низкий (случай кодирования логического ноля – в середине такта или последовательности единиц – в начале такта).

Для того чтобы сформировать импульс для входа S, который будет приходиться на границу тактов и обозначать служебный переход с низкого уровня на высокий, используем двухвходовый логический элемент «И». На один из его входов подадим синхросигнал SYNC B (потому что его синхроимпульсы как раз приходятся на границу тактов), а на другой вход - инвертированный последовательный двоичный код. На выходе из логического элемента «И» получим импульсы равные по длительности синхроимпульсам и располагающиеся только в тех тактах, в которых входящий в устройство последовательный двоичный код имеет низкий уровень, то есть кодирует логический ноль. Работа этого узла изображена на рисунке 1.5, где - это инвертированный последовательный двоичный код, SYNC B – синхросигнал, а нижняя кривая показывает результат логического умножения этих двух сигналов.

Для того чтобы сформировать импульс для входа S, который будет приходиться на границу тактов и обозначать служебный переход с низкого уровня на высокий, используем двухвходовый логический элемент «И». На один из его входов подадим синхросигнал SYNC B (потому что его синхроимпульсы как раз приходятся на границу тактов), а на другой вход - инвертированный последовательный двоичный код. На выходе из логического элемента «И» получим импульсы равные по длительности синхроимпульсам и располагающиеся только в тех тактах, в которых входящий в устройство последовательный двоичный код имеет низкий уровень, то есть кодирует логический ноль. Работа этого узла изображена на рисунке 1.5, где - это инвертированный последовательный двоичный код, SYNC B – синхросигнал, а нижняя кривая показывает результат логического умножения этих двух сигналов.

Рисунок 1.5 –

Для получения на вход S импульса, устанавливающего триггер в состояния логической единицы и соответствующего моменту кодирования единицы в Манчестере-2, т.е. располагающегося в середине такта, используем элемент «И», к входам которого подключаем последовательный двоичный код, на этот раз не инвертированный, и синхросигнал SYNC M. На выходе получаем в середине каждого такта, в котором последовательный двоичный код обладает высоким уровнем сигнал по длительности равный синхросигналу. Этот процесс визуализирован на рисунке 1.6.

Рисунок 1.6 –

Чтобы оба полученных на элементах «И» сигнала попали на информационный вход триггера S, складываем их посредством логического элемента «ИЛИ».

Практически такой же блок элементов необходимо подключить к входу R. В него также включены 2 элемента «И» и один «ИЛИ», а также элемент «НЕ» для инвертирования ПДК. Отличие заключается в том, что инвертированный ПДК логически перемножается с синхросигналом SYNC M, а не с SYNC B, как в предыдущем случае. Таким образом, мы получаем сигнал, вызывающий переключение триггера в состояния логического ноля в середине такта, в результате на выходе Q триггера в манчестерском коде происходит переход с высокого уровня на низкий в середине такта.

Соответственно, ко второму элементу «И» подключены ПДК и SYNC B, на выходе мы получаем сигнал, который позволяет производить служебное переключение уровней с низкого на высокий в манчестерском коде, при кодировании подряд идущих логических единиц.

Как видно из сказанного выше, логическая формула сигнала поступающего на вход S выглядит соответствующим образом:

. (1)

. (1)

А для сигнала на вход R формула имеет следующий вид:

. (2)

. (2)

Рисунок 1.7 – Функциональная схема проектируемого кодера Манчестера-2

Временные диаграммы работы кодера Манчестера-2 построенного по данной функционально схеме, представлены на рисунке 1.8.

Рисунок 1.8 – Временные диаграммы работы кодера Манчестера-2

2. Расчет на структурном уровне

Проведём назначение требований к блокам функциональной схемы, представленной на рисунке 1.7, в соответствии с техническим заданием.

Так как проектируемый кодер Манчестера-2 не преобразует аналоговую величину в цифровую или наоборот, то отпадает необходимость рассчитывать уровни квантования и погрешности блоков. Это существенно уменьшает объём расчётов на структурном уровне.

Особенностью составленной функциональной схемы является то, что все блоки, кроме RS-триггера представляют собой стандартные логические вентили.

Наиболее критическим параметром для всех узлов проектируемого устройства является время задержки распространения сигнала (tPHL и tPLH), которое, согласно эмпирически полученным значениям, для устойчивой и корректной работы кодера должно быть около 0,5 - 1 нс при длительности стробирующих синхроимпульсов – 2-3 нс, так как при предельной тактовой частоте работы кодера, равной 80 МГц, длина такта составляет всего 12,5 нс.

Согласно техническому заданию синхросигналы внешние, в уровнях КМДП ИС. Таким образом, верхний уровень напряжения равен 5В, нижний нулю. Длительность строб-импульса должна быть чуть больше или равна максимальной задержке логических вентилей используемых в устройстве, для их надёжного срабатывания. В устройство подаётся два вида синхросигнала: строб-импульсы первого приходятся на начало такта, стробы-импульсы второго на середину. Внешняя схемотехника, генерирующая синхроимпульсы отвечает за их тактовую синхронизацию с поступающим в устройство последовательным кодом.

Входное и выходное напряжение высокого уровня для сигнала для всех блоков должно равняться 5 В, а напряжение низкого уровня фактически нулю. RS-триггер, согласно указанным в техническом задании требованиям о величине внешней нагрузки, должен работать на нагрузку 50 Ом.

3. Выбор элементов электрической схемы

Согласно условиям, поставленным в техническом задании, и расчёта на структурном уровне логические должен быть построен на базе КМДП-технологии и обладать высоким быстродействием – время задержки должно быть порядка 0,5 - 1 нс. Входное и выходное напряжение высокого уровня для сигнала для всех блоков должно равняться 5 В, а напряжение низкого уровня фактически нулю. Этим требования почти в полной мере удовлетворяют микросхемы быстродействующей серии ИС КР1554, разработанной по современной технологии обеспечивающей сочетание малого энергопотребления, характерного для КМДП схем, с высоким быстродействием, свойственного биполярным технологиям. Быстродействие КР1554 вполне удовлетворяет требованиям, поставленным в техническом задании, в любом случае более быстрые КМДП ИС в широком доступе отсутствуют [4]. (Западные аналоги серии КР1554 не превосходят её по быстродействию, так например инвертор КР1554ЛН1, имеет среднюю задержку распространения сигнала 3,5 нс и максимальную 7,0 нс, в то время как для зарубежного аналога этой микросхемы – 74ACT04 эти величины равны соответственно 4,5 и 7,5 нс). Кроме того вся серия КР1554 способна работать на нагрузку 50 Ом. Напряжение питания для всех элементов выбирается равным +5,5В, так как при таком значении быстродействие вентилей максимально, а также такое напряжение питания обеспечивает необходимое выходное напряжение высокого уровня в 5В.

Микросхемы серии КР1554 изготовляются по 1,4 мкм КМДП технологии с окисной изоляцией, поликремниевым затвором. Использование двухуровневой металлизации позволяет наряду с уменьшением размера кристалла, получить уменьшение амплитуды помех по шинам земли и питания [9].

|

из

5.00

|

Обсуждение в статье: Выбор и обоснование направления проектирования |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы