|

Главная |

Базовая архитектура ПК IBM PC , процессор с точки зрения программиста, регистры общего назначения, регистр флагов

|

из

5.00

|

Понятие «архитектура ЭВМ» включает в себя структурную организацию аппаратных средств (аппаратная организация - набор блоков, устройств, объединенных в единую вычислительную систему) и функциональную организацию, позволяющую реализовать программное управление этой ВС. С точки зрения программиста архитектура ЭВМ - это набор программно-доступных средств.

В современных ПК реализован магистрально-модульный принцип построения. Все устройства (модули) подключены к центральной магистрали, системной шине (единая магистраль), которая включает в себя адресную шину, шину данных и шину управления.

Шина – это набор линий связи, по которым передается информация от одного из источников к одному или нескольким приемникам. Адресная шина однонаправленная, адреса передаются от процессора. Шина данных двунаправленная, данные передаются как от процессора, так и к процессору. В шину управления входят линии связи и однонаправленные и двунаправленные.

Внешние устройства работают значительно медленнее процессора, поэтому для организации параллельной работы процессора и внешних устройств в архитектуру компьютера включается устройство управления внешними устройствами, называемое контроллером (адапт. Плата). Для ускорения работы с ОП – канал прямого доступа к памяти (ДМА). Чтобы это все синхронно работало и автоматически управлялось, существует система прерываний.

Если какому-либо внешнему устройству необходима работа процессора, она посылает процессору сигнал прерывания, процесс приостанавливает выполнение одной программы и переходит к выполнению другой программы, называемой отработчиком прерываний, запомнив предварительно точку возврата.

Архитектура ix86. Процессор ix86 после включения питания устанавливается в реальный режим адресации памяти и работы процессора, который большинство ОС сразу переводит в защищенный режим, обеспечивая многозадачность, распределение памяти, ресурсов и других дополнительных возможностей. Программы пользователей в таких ОС могут работать в еще одном режиме, режиме виртуальных машин, из которого доступны все средства реального режима, но не доступны некоторые средства защищенного режима.

Совокупность программно-доступных средств процессора называется архитектурой процессора, с точки зрения программиста. Начиная с ix86 процессора программисту доступны 16 основных

регистров, 11 регистров для работы с сопроцессором и мультимедийными приложениями, и в реальном режиме доступны некоторые регистры управления и некоторые специальные регистры.

Регистр – это набор из n устройств, способных хранить n-разрядное двоичное число.

32-х разрядные регистры общего назначения без ограничения могут использоваться для временного хранения команд, адресов и данных. Обращение к ним осуществляется по именам EAX, EBX, ECX, EDX при работе с 32-х разрядными данными, по именам AX, BX, CX, DX, при работе со словами - 16-ти разрядными данными, и при работе с байтами могут использоваться восемь 8-миразрядных регистров: AL, AH, BL, BH, CL, CH, DL, DH.

Эти регистры имеют собственные имена, которые говорят о том, как они обычно используются. АХ - аккумулятор, в который чаще всего посылаются результаты операций. DX – регистр данных, в него записывается старшая часть результата, если АХ для этого мало. BX – регистр базы используется для организации специальной адресации операндов по базе. СХ - счетчик используется автоматически для организации циклов и при работе со строками.

Регистры указателей и индексов имеют специальные назначения. Регистры индексов используются для организации способов адресации операндов, а регистры указателей - для организации работы с сегментом стека.

SI – индекс источника, DI – индекс приемника, используется при работе со строками и для сложной адресации операндов. SP и BP – стек-пойнтер, для работы со стеком, первый указывает на вершину стека, второй для сложной адресации.

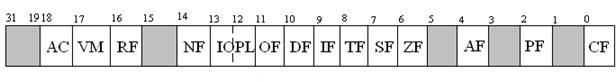

Регистр флагов. Регистр FLAGS или EFLAGS определяет состояние процессора и программы в каждый текущий момент времени.

• CF - перенос

• PF - четность

• AF - полуперенос

• ZF - флаг нуля

• SF - флаг знака

• TF - флаг трассировки

• IF - флаг прерывания

• DF - флаг направления

• OF - флаг переполнения

• AC - флаг выравнивания операндов

• VM - флаг виртуальных машин

• RF - флаг маскирования прерывания

• NT - флаг вложенной задачи

• IOPL - уровень привилегий ввода/вывода.

Биты 1, 3, 5, 15, 19 - 31 - не используются, зарезервированы.

В реальном режиме используют 9 флагов, из них 6 реагируют на результат выполнения команды, 3 определяют режим работы процессора.

В защищенном режиме используются 5 дополнительных флагов, определяющих режим работы процессора.

CF устанавливается в 1, если при выполнении команды сложения осуществляется перенос за разрядную сетку (перенос из старшего разряда), а при вычитании требуется заем. 0FFFFh + 1 = 0000h и CF = 1 при работе со словами

PF = 1, если в младшем байте результата содержится четное количество единиц.

AF = 1 (автоматически по результатам программы), если в результате выполнения команды сложения (вычитания) осуществлялся перенос (заем) из 3-го разряда байта в 4-й ( из 4-го в 3-й).

ZF = 1, если результатом выполнения операции является 0 во всех разрядах результата.

SF всегда равен знаковому разряду результата (равен старшему биту результата. Например, со словами – 15).

TF – при его установки в 1 процессор переходит в пошаговый режим выполнения программы.

DF - определяет направление обработки строк данных, если DF= 0 – обработка строк идет в сторону увеличения адресов, 1 - в сторону уменьшения, ( автоматическое увеличение или уменьшение содержимого регистров индексов SI и DI на 1, 2 или 4 в зависимости от данных, с которыми работают)).

OF = 1, если результат команды превышает максимально допустимый для данной разрядной сетки. Например, при сложении переполнение возникает, если осуществляется перенос из старшего разряда знака за разрядную сетку, а из старшего цифрового разряда перенос не происходит. Или наоборот.

Перечисленные флаги используются в обоих режимах.

IOPL = 1, если уровень привилегии текущей программы меньше значения этого флажка, то выполнение команды ввод/вывод для этой программы запрещен.

NT - определяет режим работы вложенных задач (используется для выхода из вложенных задач).

RF позволяет маскировать (запрещать) некоторые прерывания процессора от внешних устройств, для выполнения критических участков программы.

VM - позволяет перейти из защищенного режима в режим виртуальных машин при установки в 1.

AC =1 приведет к сообщению об ошибке, если адреса операндов длиной в слово или двойное слово не будут кратны двум и четырем соответственно.

3) Организация памяти в реальном режиме работы, сегментные регистры, понятие исполняемого и физического адреса.

Оперативная память состоит из байтов, каждый байт состоит из 8 информационных битов.

|  | ||

зонная часть цифровая часть

32-х разрядный процессор может работать с ОП до 4Гбайт и, следовательно, адреса байтов изменяются от 0 до 232-1, в шестнадцатеричном виде (0000000016 – FFFFFFFF16).

Байты памяти могут объединяться в поля фиксированной и переменной длины. Поля фиксированная длина – слово (2 байта), двойное слово (4 байта) (их собственные имена занимают 2 или 4 байта соответственно). Поля переменной длины могут содержать произвольное количество байтов.

Адресом поля является адрес младшего входящего в поле байта. Адрес поля может быть любым (четным или нечетным). ОП может использоваться как непрерывная последовательность байтов, так и сегментированная.

Физический адрес (ФА) байта записывается как (если она сегментированная):

<сегмент> : <смещение>, т.е. он может быть получен по формуле ФА = АС + ИА, где АС – адрес сегмента, ИА – исполняемый адрес, т.е. ИА – смещение относительно начала сегмента формируется в команде различными способами в зависимости от способа адресации операндов.

В защищенном режиме программа может определить до 16383 сегментов размером до 4 Гбайт, и таким образом может работать с 64 Тбайтами виртуальной памяти.

Для реального режима АС определяется сегментным регистром и для получения двадцатиразрядного двоичного адреса байта необходимо к содержимому сегментного регистра ( 16-ти разрядное), смещенного на 4 разряда влево, прибавить шестнадцатиразрядное смещение - ИА.

Например, адрес следующей исполняемой команды:

ФА = (CS) + (IP)

(CS) = 7A1516 = 011110100001010100002,

(IP) = C7D916 = 11000111110110012.

ФА = 8692916 = 100001101001001010012

Рассматриваемый процессор может работать с оперативной памятью как с непрерывным массивом байт (модель памяти flat), так и с разделенной на много массивов - сегментов.

Во втором случае физический адрес байта состоит из 2 х частей: адрес начала сегмента и смещение внутри сегмента. 3 типа сегментов: кодовые, с. данных и с. стека.

Для получения адреса начала сегмента используются сегментные регистры DS,ES, FS, GS, CS и SS, называемые селекторами. Операционные системы могут размещать сегменты в различных областях оперативной памяти и даже временно записывать на винчестер, если ОП не хватает. С каждым селектором связан программно-недоступный дескриптор, в котором содержится адрес сегмента, размер сегмента и некоторые его атрибуты. Это для защищенного режима работы. В реальном режиме размер сегмента фиксирован и составляет 64 Кбайта. Адрес сегмента кратен 16 и в 16-ой системе счисления может быть записан в виде XXXX016 и четыре старшие цифры адреса сегмента содержатся в сегментном регистре. В защитном режиме размер сегмента может изменяться до 4Гбайт.

DS, ES, FS, GS - 16-ти разрядные сегментные регистры, используемые для определения начала сегментов данных. CS - сегментный регистр кодового сегмента. SS - сегментный регистр для определения сегмента стека.

Сегментных регистров всего 6, но в любой момент пользователь может изменить содержимое этих регистров. Например ,если изменить CS, то процесс перейдет на выполнение другой программы ( программа по другому адресу), но с тем же значением смещения внутри сегмента. А смещение внутри команды (кодового сегмента) содержится в регистре, называемом счетчиком команд, указателем команд. Если изменить содержимое регистра IP,то будет выполняться не следующая команда в том же кодовом сегменте, а какая-то другая. Именно так работают команды передачи управления, команды циклов, команды обращения к под программам.

Адрес начала сегмента стека определяется автоматически ОС с помощью регистра SS, а указатель на вершину стека – это регистр указателей SP (ESP). Cтек организован таким образом, что при добавлении элементов в стек, содержимое указателя стека уменьшается. Стек растет вниз от максимального значения, хранящегося в SS (растет вниз головой). При добавлении в стек адреса уменьшаются. Такая организация необходима при использовании модели памяти flat. В этом случае программа размещается, начиная с младших адресов, а стек размещается в старших адресах.

Стек используется для временного хранения данных, для организации работы с подпрограммами, в том числе и рекурсивными, для передачи параметров подпрограммам, размещения локальных параметров и т.д.

Для того, чтобы стек можно было использовать для хранения и фактических и локальных параметров, после передачи фактических параметров значение указателя на вершину стека можно сохранить в регистре BP и тогда к глобальным параметрам можно обращаться, используя конструкцию

BP - k, а к локальным - BP + n, где k, и n - определяются количеством параметров и их длиной.

|

11) Форматы команд, машинный формат двухадресной команды

Команда – это цифровой двоичный код, состоящий из двух подпоследовательностей двоичных цифр, одна из которых определяет код операции (т.е. определяет какую операцию должен выполнить процессор. Например, сложить, умножить, переслать), вторая – определяет адреса данных, участвующих в операции, или сами данные и место расположения результата операций.

Рассматриваемый процессор может работать с безадресными командами, одно-, двух- и трехадресными командами. Команда в памяти может занимать от 1 до 15 байт и длина команды зависит от кода операции, количества и места расположения операндов. Данные в операции могут находиться непосредственно в команде, в регистрах, процессора или оперативной памяти. Наиболее часто используемыми являются двухадресные команды следующих форматов:

R-R M-M R-M M-R R-D M-D,

где R – регистр, M – память, D – данные.

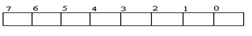

Машинный формат двухадресной команды, для которой один операнд находится всегда в регистре, а второй – в регистре или памяти можно представить следующим образом:

MOD – модификация, reg – регистр, r/m – регистр памяти.

“disp H/disp L” – “старшая / младшая часть смещения.

Поля “код операции” и иногда “reg” определяют выполняемую операцию.

Поле “d” определяет место хранения первого операнда (по какому адресу будет отправлен результат: по адресу 1 или 2 операнда).

Поле “w” определяет с какими данными работают: с байтами, или словами. Если w = 0, команда работает с байтами, w = 1 - со словами.

reg” - определяет один операнд, хранимый в регистре.

Поля “mod”, “disp H” и “disp L” определяют второй операнд, который может храниться в регистре или в памяти.

MOD={00 01 10 11}.

Если mod = 11, то второй операнд находится в регистре, он определяется полем “r/m”, а “disp H/disp L” – отсутствует, команда будет занимать 2 байта в памяти, если mod < > 11, то второй операнд находится в памяти и определяется со смещением r/m.

Значение поля “mod” определяет как используется смещение:

00, disp – отсутствует - операция в памяти, смещение отсутствует.

mod 01, disp = disp L – с распространением знака до 16 (смещение определяется младшим байтом disp L, но с расширением знакового разряда до 16).

10, смещение состоит из disp H и disp L.

Поля “reg” и “r/m” определяют регистры:

| reg / r/m | ||||||||

| w = 0 | AL | CL | DL | BL | AH | CH | DH | BH |

| w = 1 | AX | CX | DX | BX | SP | BP | SI | DI |

Физический адрес определяется так:

| r/m | ИА | ФА |

| (BX) + (SI) + disp | + (DS) (оно смещенное на 4 разряда влево) | |

| (BX) + (DI) + disp | + (DS) (оно смещенное на 4 разряда влево) | |

| (BP) + (SI) + disp | + (SS) (SS смещенное на 4 разряда влево) | |

| (BP) + (DI) + disp | + (SS) | |

| (SI) + disp | + (DS) | |

| (DI) + disp | + (DS) | |

| (BP) + disp | + (SS) | |

| (BX)+ disp | + (DS) |

Если второй операнд в памяти, то физический адрес определяется в зависимости от поля r/m способом, указанным в таблице. ( ) – содержимое регистра, disp – смещение, DS – основной сегмент данных, BP - указатель базы для стека.

27) Способы адресации операндов, примеры команд с использованием различных способов адресации.

Операнды могут находиться в регистрах, памяти и непосредственно в команде и размер операндов может быть - байт, слово или двойное слово.

Исполняемый адрес операнда в общем случае может состоять

из трех частей: <база> <индекс> <смещение>, например, [BX] [SI] M.

Существуют различные способы адресации операндов, такие как:

1. регистровая (операнд находится в регистре)

2. непосредственная (операнд непосредственно в команде)

3. прямая (адрес операнда прямо в команде)

4. косвенно-регистровая (в регистре находится адрес операнда, размещ. В памяти машины)

5. по базе со смещением (базовый регистр)

6. прямая с индексированием (для работы с одномерными массивами)

7. по базе с индексированием (двумерные массивы)

8. косвенная адресация с масштабированием

9. базово-индексная с масштабированием

10. базово-индексная с масштабированием и смещением.

Адресации с 8 по 10 используются только в защищенном режиме.

|

из

5.00

|

Обсуждение в статье: Базовая архитектура ПК IBM PC , процессор с точки зрения программиста, регистры общего назначения, регистр флагов |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы