|

Главная |

Схемы логических блоков

|

из

5.00

|

Как указывалось выше, для логических функций НЕ, И, ИЛИ применяются блоки на диодах, транзисторах, ферритах, ферриттранзисторах и интегральных схемах.

Логические схемы НЕ (или инверторы). Эти схемы реализуют операцию логического отрицания. Наиболее простая схема транзисторного инвертора представлена на рис. VI.45.

Логические схемы НЕ (или инверторы). Эти схемы реализуют операцию логического отрицания. Наиболее простая схема транзисторного инвертора представлена на рис. VI.45.

Как известно, сигналы физического представления двоичных чисел (единиц и нулей) в вычислительных машинах могут быть реализованы в форме двух уровней электрических напряжений (высокого и низкого) или электрических импульсов (положительного и отрицательного). Представим себе, что сигнал высокого уровня подан на вход приведенной схемы. Транзистор отпирается, и вследствие того, что он находится в режиме насыщения, потенциал на выходе будет близок к нулю. Наоборот, при подаче низкого напряжения на вход транзистор оказывается запертым, и потенциал на выходе будет высоким (почти равным Ек). Таким образом, схема, приведенная на рис. VI.45, осуществляет операцию инверсии.

Как известно, сигналы физического представления двоичных чисел (единиц и нулей) в вычислительных машинах могут быть реализованы в форме двух уровней электрических напряжений (высокого и низкого) или электрических импульсов (положительного и отрицательного). Представим себе, что сигнал высокого уровня подан на вход приведенной схемы. Транзистор отпирается, и вследствие того, что он находится в режиме насыщения, потенциал на выходе будет близок к нулю. Наоборот, при подаче низкого напряжения на вход транзистор оказывается запертым, и потенциал на выходе будет высоким (почти равным Ек). Таким образом, схема, приведенная на рис. VI.45, осуществляет операцию инверсии.

Логическая схема И. Эту схему часто называют также схемой совпадения. В структурном отношении схема совпадения представляет собой многополюсник с несколькими входами и одним выходом, прячем сигнал на выходе появляется только в том случае, если одновременно на всех входах имеются определенные сигналы. На рис. VI.46 представлена схема совпадения на полупроводниковых диодах с тремя входами и одним выходом. При подаче на все входы напряжения высокого уровня все диоды будут заперты, ток через резистор R протекать не будет и на выходе появится" сигнал высокого уровня (потенциал -f£). Если на одном из входов будет отсутствовать сигнал напряжения высокого уровня, то соответствующий диод станет проводящим, вследствие чего через резистор R пройдет ток и на резисторе возникнет падение напряжения. На выходе будем иметь низкий потенциал.

Логическая схема И. Эту схему часто называют также схемой совпадения. В структурном отношении схема совпадения представляет собой многополюсник с несколькими входами и одним выходом, прячем сигнал на выходе появляется только в том случае, если одновременно на всех входах имеются определенные сигналы. На рис. VI.46 представлена схема совпадения на полупроводниковых диодах с тремя входами и одним выходом. При подаче на все входы напряжения высокого уровня все диоды будут заперты, ток через резистор R протекать не будет и на выходе появится" сигнал высокого уровня (потенциал -f£). Если на одном из входов будет отсутствовать сигнал напряжения высокого уровня, то соответствующий диод станет проводящим, вследствие чего через резистор R пройдет ток и на резисторе возникнет падение напряжения. На выходе будем иметь низкий потенциал.

На рис. VI.47, а и б приведены примеры логических схем совпадения на ферритовых сердечниках [34]. Магнитный материал сердечников характеризуется петлей гистерезиса, близкой к прямоугольной. Рассмотрим схему, показанную на рис. VI.47, а, предполагая для упрощения, что петля идеально прямоугольная. Подадим на обмотку А импульс намагничивающей силы НА, причем величина НА удовлетворяет неравенству

На рис. VI.47, а и б приведены примеры логических схем совпадения на ферритовых сердечниках [34]. Магнитный материал сердечников характеризуется петлей гистерезиса, близкой к прямоугольной. Рассмотрим схему, показанную на рис. VI.47, а, предполагая для упрощения, что петля идеально прямоугольная. Подадим на обмотку А импульс намагничивающей силы НА, причем величина НА удовлетворяет неравенству

(VI. 152)

(VI. 152)

где НС — коэрцитивная сила магнитного материала.

При этом сердечник не может перемагнититься, а ЭДС, наведенная в выходной обмотке при подаче сигнала, вызовет только помеху. То же самое будет, если на обмотку Б подать импульс НБ, причем

(VI. 153)

(VI. 153)

Но если на входы обмоток А и Б подать одновременно импульсы намагничивающих сил НА и НБ, причем

(VI. 154)

(VI. 154)

и, кроме того, соблюдено условие совпадения фаз сигналов намагничивания, то при согласном включении обмоток произойдет перемагничивание сердечника, и на выходе схемы появится сигнал. Для правильной работы схемы входные импульсы НА и НБ должны быть переменной полярности. Это необходимо для подготовки магнитного состояния сердечника к приему следующих импульсов.

При однополярных входных сигналах используют схему, показанную на рис. VI.47, б. Эта схема действует аналогично предыдущей, но здесь сердечник имеет дополнительную обмотку С, к которой подключено постоянное напряжение смещения, создающее в сердечнике постоянную намагничивающую силу Нсм. Однополярные сигналы, подаваемые на обмотки А и Б, должны теперь удовлетворять неравенству

1/2 (Нс + Нсм) < НА = НБ < Нс + Нсм. (VI. 155)

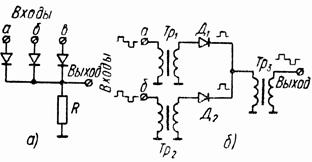

Логическая схема ИЛИ. Эти схемы часто называют схемами собирания. На рис. VI.48, а представлена подобного рода схема на диодах для положительных сигналов. Схема имеет один выход и несколько входов а, б, в, на которые поступают сигналы напряжения высокого уровня. Сигнал на выходе возникает всякий раз, как только хотя бы на одном из входов появляется сигнал высокого уровня.

Логическая схема ИЛИ. Эти схемы часто называют схемами собирания. На рис. VI.48, а представлена подобного рода схема на диодах для положительных сигналов. Схема имеет один выход и несколько входов а, б, в, на которые поступают сигналы напряжения высокого уровня. Сигнал на выходе возникает всякий раз, как только хотя бы на одном из входов появляется сигнал высокого уровня.

На рис. VI.48, б приведена схема логического элемента ИЛИ, построенная на полупроводниковых диодах и трансформаторах. Поступающие нэ входы а и б импульсы переменной полярности трансформируются трансформаторами Тр1 и Тр2 и проходят через полупроводниковые диоды Д1 и Д2, которые пропускают полуволну только положительной полярности. Преобразованные импульсы поступают на выход схемы через трансформатор Тр3. При этом на выходе мы получим импульсы опять переменной полярности.

На рис. VI.48, б приведена схема логического элемента ИЛИ, построенная на полупроводниковых диодах и трансформаторах. Поступающие нэ входы а и б импульсы переменной полярности трансформируются трансформаторами Тр1 и Тр2 и проходят через полупроводниковые диоды Д1 и Д2, которые пропускают полуволну только положительной полярности. Преобразованные импульсы поступают на выход схемы через трансформатор Тр3. При этом на выходе мы получим импульсы опять переменной полярности.

Комбинированные логические схемы. Недостатком логических схем НЕ, И, ИЛИ (см. рис. VI.45-VI.47) является отсутствие порога переключения, т.е. ограниченная возможность каскадирования, и малая нагрузочная способность. В связи с этим в последнее время чаще используют комбинированные блоки, содержащие схемы И, ИЛИ с транзисторным инвертором. Такие блоки И-НЕ, ИЛИ-НЕ являются универсальными, т.е. могут реализовать любую функцию алгебры логики [17].

Рис. VI.49. Схемы комбинированных логических блоков:

а — транзисторно-резисторный логический; б — диодно-транзисторный логический ИЛИ —НЕ; в — транзисторно-логический ИЛИ —НЕ с резистивными связями; г — транзисторный логический ИЛИ — НЕ с резистивно-емкостными связями; д — транзисторный логический ИЛИ—НЕ с эмиттерной связью; е— транзисторный И —НЕ со сложным инвертором.

На рис. VI.49 приведены наиболее распространенные схемы транзисторных комбинированных блоков. Эти схемы достаточно просто реализуются средствами современной микроэлектроники. В СССР и за рубежом [61] в настоящее время такие блоки выпускаются промышленностью в виде интегральных гибридных и полупроводниковых схем. Кроме того, с развитием интегральной микроэлектроники были разработаны новые схемы логических блоков, которые ранее не использовались. Примером может служить типовая схема интегрального транзисторного логического блока И—НЕ (ТТЛ) (рис. VI.49, ё). Здесь операция И реализуется с помощью специфического компонента — многоэмиттерного транзистора, эквивалентного нескольким транзисторам, а операция инверсии осуществляется с помощью сложного инвертора, содержащего три транзистора. Несмотря на относительную сложность схемы по сравнению с транзисторными насыщенными логическими блоками другого типа (рис. VI.49, а—г), данный блок в интегральном исполнении имеет массу, габаритные размеры не больше, чем у других блоков, а потребляемую мощность, быстродействие и надежность — выше.

На рис. VI.50 показана схема блока И—НЕ/ИЛИ—НЕ с одним источником питания. Этот блок характеризуется высокой помехоустойчивостью и отличается высокой надежностью.

Приведем сравнительную оценку блока НЕ—И/ИЛИ—НЕ, изготовленного для различных типов логических схем по одной технологии (табл. VI.5).

Таблица VI.5

| Типы логических схем | Быстродействие, МГц | Зона помехоустойчивости, В |

| ТЛ РТЛ ДТЛ ТТЛ | 0,5—1 5—10 10—25 10—20 | 2—4 0,25—0,80 0,50—1,00 0,50—1,00 |

Сравнительные показатели блока НЕ—И/ИЛИ—НЕ, с различными логическими схемами

Триггер со счетным входом. Типовая схема такого триггера приведена на рис. VI.59. Пусть в исходном состоянии (в отсутствие сигнала на входе) транзистор T1 заперт, транзистор T2 насыщен и на выходе Q поддерживается низкий потенциал. При подаче на счетный вход импульса положительной полярности транзистор T2 также запирается. По окончании действия входного импульса вследствие различия зарядов, накопленных на емкостях С1 и С2, базовый ток, отпирающий транзистор T1, оказывается больше, чем базовый ток транзистора T2. В результате транзистор T1 входит в насыщение, транзистор T2 запирается и на выходе Q устанавливается высокий потенциал. Таким образом, триггер изменяет свое состояние после поступления каждого очередного импульса на счетный вход. Работа триггера иллюстрируется временными диаграммами, приведенными на рис. VI.60.

Триггер со счетным входом. Типовая схема такого триггера приведена на рис. VI.59. Пусть в исходном состоянии (в отсутствие сигнала на входе) транзистор T1 заперт, транзистор T2 насыщен и на выходе Q поддерживается низкий потенциал. При подаче на счетный вход импульса положительной полярности транзистор T2 также запирается. По окончании действия входного импульса вследствие различия зарядов, накопленных на емкостях С1 и С2, базовый ток, отпирающий транзистор T1, оказывается больше, чем базовый ток транзистора T2. В результате транзистор T1 входит в насыщение, транзистор T2 запирается и на выходе Q устанавливается высокий потенциал. Таким образом, триггер изменяет свое состояние после поступления каждого очередного импульса на счетный вход. Работа триггера иллюстрируется временными диаграммами, приведенными на рис. VI.60.

Одна из распространенных модификаций триггера представлена на рис. VI.61. Данная схема выполняет функции RS-триггера, а также имеет счетный вход.

В рассмотренных схемах триггеров емкости, накапливая соответствующий заряд, осуществляют «запоминание» предыдущего состояния триггера и обеспечивают требуемое направление процесса переключения. В современной микроэлектронике реализация в схемах емкостей значительных номиналов затруднительна, поэтому в микроэлектронных триггерных схемах для запоминания состояния часто используют не заряд на емкостях, а например, запоминание на дополнительной бистабильной ячейке. На рис. VI.62 показана одна из схем триггеров со счетным входом, не имеющая реактивных компонентов. Несмотря на относительную сложность, этот триггер легко реализуется в виде интегральной схемы, имеет малые габаритные размеры и массу, высокую надежность и хорошие электрические характеристики.

Свойство триггеров иметь два устойчивых состояния может быть использовано для физического представления двоичных чисел, если одно из двух состояний принять за цифру 0, а другое — за 1. Тогда для изображения заданного числа в двоичной системе достаточно взять столько триггеров, сколько имеется разрядов в числе, и ввести условную отметку нулевых и единичных (рабочих) состояний триггеров. Цепочка из триггеров, которая служит для условной записи одного числа, называется регистром.

Свойство триггеров иметь два устойчивых состояния может быть использовано для физического представления двоичных чисел, если одно из двух состояний принять за цифру 0, а другое — за 1. Тогда для изображения заданного числа в двоичной системе достаточно взять столько триггеров, сколько имеется разрядов в числе, и ввести условную отметку нулевых и единичных (рабочих) состояний триггеров. Цепочка из триггеров, которая служит для условной записи одного числа, называется регистром.

Указанное свойство триггеров позволяет также использовать их для построения счетчиков импульсов.

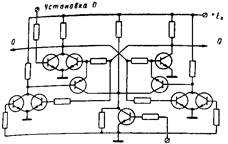

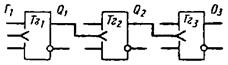

Счетчик (рис. VI.63). Это устройство легко реализуется при использовании триггеров со счетными входами. Временная диаграмма, иллюстрирующая работу счетчика, показана на рис. VI.64. Как видно из диаграммы, на выходе триггера Тг1 (см. рис. VI.63) один импульс формируется после поступления двух входных импульсов (пересчет на два), на выходе Тг2 один импульс формируется после поступления четырех входных (пересчет на четыре), на выходе Тг3 один импульс соответствует поступлению восьми входных (пересчет на восемь).

Счетчик (рис. VI.63). Это устройство легко реализуется при использовании триггеров со счетными входами. Временная диаграмма, иллюстрирующая работу счетчика, показана на рис. VI.64. Как видно из диаграммы, на выходе триггера Тг1 (см. рис. VI.63) один импульс формируется после поступления двух входных импульсов (пересчет на два), на выходе Тг2 один импульс формируется после поступления четырех входных (пересчет на четыре), на выходе Тг3 один импульс соответствует поступлению восьми входных (пересчет на восемь).

Каждый триггер имеет устройство для стирания предыдущей записи и неоновую лампочку для сигнала о том, что триггер находится в рабочем состоянии (запись 1).

Каждый триггер имеет устройство для стирания предыдущей записи и неоновую лампочку для сигнала о том, что триггер находится в рабочем состоянии (запись 1).

|

Если пределом счета является n-разрядное двоичное число, то счетчик должен иметь п триггеров. Импульсы, подлежащие счету, подаются на вход первого триггера, причем к моменту начала счета предыдущие записи триггера должны быть стерты. Чтобы стереть информацию, зафиксированную счетчиком, подают сигнал в форме отрицательного импульса на вход гашения. При этом все

Если пределом счета является n-разрядное двоичное число, то счетчик должен иметь п триггеров. Импульсы, подлежащие счету, подаются на вход первого триггера, причем к моменту начала счета предыдущие записи триггера должны быть стерты. Чтобы стереть информацию, зафиксированную счетчиком, подают сигнал в форме отрицательного импульса на вход гашения. При этом все

триггеры переходят в начальное (нулевое) состояние, что

указывается потухшими неоновыми лампочками.

При поступлении первого импульса триггер Тг1 переходит в рабочее состояние, зажигается его неоновая лампочка. Положительные импульсы, возникающие в системе при переходе триггеров из одного состояния в другое, не пропускаются соответствующими диодами.

Если начальное состояние триггеров отвечает цифре 0, а рабочее — цифре 1, то после первого отрицательного импульса счетчик зафиксирует двоичное число 000 ... 01 = 1. Второй импульс перебросит триггер Тг1 в начальное состояние, его неоновая лампочка погаснет, а отрицательный им-пульс с выхода триггера Тг1 поступит на запуск триггера Тг2 и переведет его в рабочее состояние. Счетчик зафиксирует двоичное число 00 ... 010 = 2.

Следующий импульс, поданный на вход счетчика, переведет триггер Тг1, в рабочее состояние, причем триггер Тг2 сохранит свое предыдущее состояние. Зафиксированное счетчиком двоичное число будет 00... 011 = 3.

Продолжая подавать импульсы, мы заставим счетчик фиксировать их общее число, т. е. выполнять счет импульсов. Счет импульсов происходит со скоростью до 100 000 импульсов в секунду. Для подсчета 107 импульсов требуется счетчик на 20 триггеров.

Схемы счетчиков импульсов разнообразны. Наряду с двоичными счетчиками нередко применяют десятичные счетчики, составленные из триггеров в комбинации с логическими схемами управления.

|

Регистр сдвига (рис. VI.65, а). Это устройство удобно строить, используя RS-триггеры со счетным входом. Временные диаграммы, иллюстрирующие работу регистра, представлены на рис. VI.65, б. Предварительно в регистр записывается начальная информация установкой триггеров в соответствующие состояния. После поступления каждого тактового импульса информация сдвигается по цепи триггеров вправо, т. е. последующий триггер принимает состояние предыдущего.

Сумматор. На рис. VI.66 приведена простейшая схема сумматора, в которой используются триггеры со счетным входом и логические элементы ИЛИ. Одно из слагаемых, представленное в двоичном коде, поразрядно записывается в регистр триггеров. Второе слагаемое подается на счетные входы триггеров через элементы ИЛИ. Происходит логическое суммирование сигналов и формируются соответствующие выходные перепады напряжений. Емкости дифференцируют выходные перепады и формируют импульсы переноса из младших разрядов в старшие. Импульсы переноса, задержанные на время т, достаточное для окончания переходных процессов в триггере, поступают через элемент ИЛИ на счетный вход старшего разряда. Происходит суммирование единиц переноса, и в сумматоре устанавливается окончательный результат.

Запоминающие устройства (ЗУ). Запоминающие устройства, действие которых основано на различных физических принципах, находят широкое применение в вычислительной технике и автоматике. Они предназначены для записи, хранения и выдачи числовой и командной информации, записанной в дискретной форме, и имеют разнообразные наименования: накопители информации, блок памяти, запоминающие устройства, устройства хранения.

Основными показателями, характеризующими запоминающее устройство, являются емкость, или число элементов информации, которое можно разместить в запоминающем устройстве; время, потребное для записи информации и для ее считывания; плотность записи информации, приходящейся на единицу измерения носителя. В тех случаях, когда требуется многократная запись информации в одни и те же ячейки памяти запоминающего устройства, оно должно иметь приспособление для уничтожения сделанной ранее записи. Существует много типов носителей информации, на которых могут быть созданы ячейки ЗУ.

Выше мы уже отмечали свойство триггера, позволяющее записывать хранить и считывать числа. Таким образом, триггер является элементом памяти, с помощью которого можно построить запоминающее устройство для записи чисел или другой информации с произвольной длительностью хранения и возможностью стирания.

Остановимся кратко на некоторых часто встречающихся запоминающих устройствах с различными носителями информации.

ЗУ, в которых используются перфоленты и перфокарты. Перфоленты и перфокарты применяются в ЗУ ввода и вывода ЦВМ, в ЗУ систем автоматического регулирования для задания программ регулирования, например, программ для автоматической обработки изделий на станке. Это широко распространенный и дешевый носитель информации. Движение перфоленты может быть непрерывным или пульсирующим с постоянным шагом. Запись на перфолентах и перфокартах не стирается, допускает длительное хранение и многократное использование. Перфоленты хранятся в виде рулонов, а перфокарты — в виде массивов. Таким образом, можно иметь библиотеку различных программ, команд, инструкций и прочей информации, оформленной на перфолентах и перфокартах.

Наиболее сложной задачей при использовании рассматриваемого вида запоминающих устройств является задача считывания и записи с перфолент или перфокарт. Приборы считывания называют считывающими головками или трансмиттерами. Считывание может выполняться электромеханическим способом или с помощью фотоэлемента. Наибольшая скорость считывания при помощи электромеханического трансмиттера обычно не выше шести цифр в секунду для одного ряда. Для фотоэлектрических трансмиттеров эта скорость достигает 2500 цифр в секунду, а скорость перемещения ленты до 6 м/с.

|

из

5.00

|

Обсуждение в статье: Схемы логических блоков |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы