|

Главная |

Новые возможности процессора с введением SSE2 и SSE3

|

из

5.00

|

SSE2 значительно расширяет возможности обработки нескольких операндов по принципу SIMD. Используется 144 новых команды, обеспечивающих одновременное выполнение операций над несколькими операндами, которые располагаются в памяти и в 128-разрядных регистрах ХММ. В регистрах могут храниться и одновременно обрабатываться два числа с плавающей запятой в формате двойной точности (64 разряда) или 4 числа в формате одинарной точности (32 разряда), любые целочисленные типы данных, способные разместиться в 128-разрядных регистрах. Команды SSE2 существенно повышают эффективность процессора при реализации трехмерной графики и Интернет - приложений, обеспечение сжатия и кодирования аудио- и видеоданных и в ряде других приложений.

SSE3 включает 5 новых операций с комплексными числами, 5 потоковых операций над числами с плавающей запятой, 2 команды для синхронизации потоков и одну специальную инструкцию для применения при кодировании видео.

Расширения AES-NI и AVX

AES-NI – набор из 6 новых SIMD-инструкций, ускоряющий процесс шифрования и дешифрования информации по стандарту AES. Стандарт AES является стандартом шифрования США, принятым в 2000-ом году. Он специфицирует алгоритм Rijndael, который представляет собой симметричный блочный шифр, работающий с блоками длиной 128 бит, и использует ключи длиной 128, 192 и 256 бит.

AVX – расширение системы команд х86 для микропроцессоров с новой микроархитектурой Intel Sandy Bridge и процессоров AMD Bulldozer. Представляет различные улучшения, новые инструкции и новую схему кодирования машинных кодов. Размер векторных регистров SIMD увеличивается с 128-ми до 256 бит. Существующие 128-битные инструкции будут использовать только младшую половину новых YMM-регистров. Набор инструкций AVX позволяет использовать любую двухоперандную инструкцию ХММ в трехоперандном виде без модификации 2-х регистров-источников, с отдельным регистром для результата. Добавлены инструкции с количеством операндов, более трех. Новая система кодирования машинных кодов VEX предоставляет новый набор префиксов кода, которые расширяют пространство возможных машинных кодов.

Особенности архитектуры процессоров x86-64

процессор, построенный на основе х86-64, может безо всяких проблем исполнять существующие 32-битные приложения, Причем, эти приложения могут выполняться без каких бы то ни было потерь в производительности. Существующие в х86 регистры общего назначения расширены с 32 до 64 бит и к ним добавлены еще 8 новых 64 разрядных регистров.

В 64-битном режиме обеспечивается поддержка:

- 64-битных виртуальных адресов;

- 8 новых и расширенных 64-битных регистров общего назначения;

- 64-битного указателя инструкций RIP;

- сплошного адресного пространства с единым пространством для инструкций, данных и стека.

- 64-битных арифметических и логических операций над целыми числами.

AMD64

архитектура AMD64 предполагает поддержку процессорами 2-х режимов: Long Mode («длинный» режим), имеющего два подрежима – 64-битный режим и Compatibility mode (режим совместимости), и Legacy Mode (наследственный режим). Что они собой представляют, можно понять из табл. 2.2.

Итак, в 64-битном режиме обеспечивается поддержка:

- 64-битных виртуальных адресов;

- 8 новых и расширенных 64-битных регистров общего назначения;

- 64-битного указателя инструкций RIP;

- сплошного адресного пространства с единым пространством для инструкций, данных и стека.

- 64-битных арифметических и логических операций над целыми числами.

Данный режим снимает ограничение в размерности адресного пространства оперативной памяти, которое в современных 32-разрядных х86 системах составляет 232 = 4 Гбайт.

Для адресации новых регистров в команды введены так называемые «префиксы расширения регистра», кодирование которых осуществляется кодами, использующимися для команд INC <регистр> и DEC <регистр> в 32- и 16-битных режимах. Команды INC и DEC в 64-битном режиме должны кодироваться в более общей, двухбайтовой форме.

Intel 64

Архитектура Intel 64 (технология EM64T) в сочетании с соответствующим программным обеспечением поддерживает работу 64-разрядных приложений на серверах, рабочих станциях, настольных ПК и ноутбуках. Она, как и х86-64 от AMD, реализует 64-разрядное расширение регистров, те же режимы работы процессора, ту же программную совместимость с 16- и 32-битными приложениями, а главное – эта технология расширяет адресное пространство виртуальной и физической памяти.

Архитектура Intel 64 поддерживает следующие возможности:

- 64-разрядное сплошное пространство виртуальных адресов;

- 64-разрядные указатели;

- 64-разрядные регистры общего назначения;

- 64-разрядная поддержка вычислений с целыми числами;

- до 1 Тбайт адресного пространства платформы.

· 44. Обобщенный формат команд x86

· Базовый набор команд обеспечивает выполнение операций над операндами, которые находятся в регистре, памяти или непосредственно в команде. В набор входят безадресные, одно-, двух- и трехадресные команды. Процессор реализует следующие типы двухадресных команд: регистр – регистр; память – регистр; непосредственный операнд – регистр; регистр – память; память – память; непосредственный операнд – память.

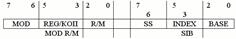

· Операнды могут содержать 8, 16 или 32 разряда. Для реализации различных типов команд определены форматы, задающие порядок размещения информации о выполняемой операции и способах выбора операндов. Обобщенный вид формата команды допускает наличие следующих полей: кода операции (1 или 2 байта); байтов адресации (0, 1 или 2 байта); байтов смещения (0, 1, 2 или 4 байта); байтов непосредственных данных — операндов (0, 1, 2 или 4 байта).

· Команды содержат от 1 до 12 байт. В среднем длина команды составляет 4 – 5 байт.

· Назначение основных полей кода команды:

· Код операции определяет тип выполняемой операции. В некоторых командах в первом байте содержится бит, задающий разрядность операндов.

· В ряде команд первый байт КОП содержит поля reg или sreg, определяющие адрес используемых регистров. Трехбитовое поле reg задает выбираемый регистр в соответствии с разрядностью обрабатываемых операндов. Поле sreg (двух или трехбитовое) определяет адрес сегментных регистров. Байт адресации MОD R/M содержит три поля. Поля MОD и R/M задают адрес одного из операндов, который может храниться в регистре или ячейке памяти. Кодировка этих полей определяет выбираемый способ адресации.

|

из

5.00

|

Обсуждение в статье: Новые возможности процессора с введением SSE2 и SSE3 |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы