|

Главная |

Архитектура процессора

|

из

5.00

|

Под архитектурой процессора понимают совокупность его средств, обеспечивающих выполнение программы.

Понятие архитектуры является комплексным и включает в себя: структурную схему ЭВМ, организация и разрядность интерфейса ЭВМ, набор и доступность регистров, организация и адресация памяти, набор команд, форматы команд и данных и др. Таким образом понятие архитектуры включает в себя всю необходимую для программиста информацию о компьютере. Основные принципы архитектуры Д. фон Неймана:

1)Принцип хранимой программы - код программы и ее данные находятся в 1 адресном пространстве ОЗУ.

2)Принцип микропрограммирования - машинная команда не является самой простой операцией, выполняемой ЭВМ. Она представляет собой совокупность элементарных микроопераций(микрокоманд) - микропрограмму. В состав ЦП обязательно входит блок микропрограммного управления (БМУ), который вырабатывает набор управляющих сигналов, необходимых для выполнения 1 машинной команды. Виды микроопераций : инвертирование, сдвиг, двоичное сложение и др.

3)Линейное пространство памяти - память ЭВМ - совокупность ячеек памяти, которым присвоили адреса.

4)Последовательность выполнения программы - ЦП выбирает команды из памяти строго последовательно. Для изменения последовательного хода выполнения программы(ветвления программы) необходимо использовать специальные команды условного или безусловного перехода.

5)С точки зрения ЦП принципиальной разницы между командами и данными нет, те и другие находятся в 1 адресном пространстве в виде последовательности 0 и 1. Содержание любой ячейки памяти ЦП может трактовать как команду, поэтому в программе пространство памяти и данных надо четко разделять.

Гарвардская архитектура.

В гарвардской архитектуре память программ и память данных разделены, имеют свои собственные адресные пространства и способы доступа к ним. Это способствует более рациональному доступу к памяти.

Основные типы архитектур процессоров: а — фон-неймановская; 6 — гарвардская

05.02.2013

Все микроконтроллеры выполнены по гарвардской архитектуре, поскольку:

1) в них не производится модификация программ

2)память данных должна быть энергонезависимой

Расширенная структурная схема с процессором фон-неймановской архитектуры показана на рисунке 2. Схема процессора содержит УУ, АЛУ и регистры: адреса, данных, команд, состояния, а так же аккумулятор, указатель команд, указатель стека.

Устройство управления вырабатывают управляющие сигналы для всех блоков МП и сигналы синхронизации, а так же управляет обменом информацией между МП, памятью и УВВ.

УУ реализует следующие функции:

1)Функция начальной установки МП -внешний сигнал начальной установки процессора reset формируется при включении источника питания МП или при нажатии кнопки reset. При появлении этого сигнала устройство управления обеспечивает загрузку 0-го значения в указатель команд, который инициирует выборку из памяти байта команды с 0-м адресом. В конце выборки содержимое указателя команд увеличивается на 1, и выбирается байт команды со следующим адресом. Таким образом выполняется вся записанная в памяти программа.

2)Функция синхронизации - в соответствии с внешними управляющими сигналами и сигналами синхронизации устройство управления синхронизирует работу всех блоков МП.

3)Функция прерываний - с поступлением сигнала прерывания, УУ инициирует выполнение подпрограммы обработки соответствующего прерывания. Потребность в реализации функции прерывания возникает тогда, когда во время выполнения основной программы надо перевести процессор на решение другой задачи, например, обработки аварийной ситуации или работы с УВВ.

4)Функция согласования быстродействия модулей МПС - во время обслуживания памяти и УВВ, быстродействие которых значительно меньше, чем у МП согласование быстродействия реализуется генерацией тактов ожидания МП. Во время обслуживания устройства с большим быстродействием, чем у МП, используется режим прямого доступа к памяти.

АЛУ - арифметико-логическое устройство представляет собой комбинационную схему на основе сумматора, которая сигналами с выходов УУ настраивается на выполнение определенной арифметической или логической операции: сложение, вычитание, логическое И, логическое ИЛИ, логическое НЕ, исключающее ИЛИ, сдвиг, сравнение, десятичная коррекция. Таким образом АЛУ выполняет арифметические и логические операции над операндами(объект в виде значения данных, содержимого регистров или содержимого ячейки памяти, с которым оперирует команда), которые пересылаются из памяти (И/ИЛИ) регистров МП.

Регистры предназначены для хранения n-разрядного двоичного слова. Они представляют собой n-триггеров со схемами управления чтения/записи и выборки. Регистры создают внутреннюю память МП и используются для хранения промежуточных результатов вычислений.

Аккумулятор - регистр, в котором хранится 1 из операндов. После выполнения команды в аккумуляторе вместо операнда размещается результат операции.

06.02.2013

Указатель команд(программный счетчик) - предназначен для хранения адреса ячейки памяти, которая содержит код следующей команды. Программа действий МП записана в памяти в виде последовательности кодов команд. Для перехода к следующей команде содержимое счетчика увеличивается на 1 в момент выбора команды из памяти. Таким образом в конце выполнения команды в счетчике команд хранится адрес следующей команды.

Указатель стека - регистр, который хранит адрес последней занятой ячейки стека. Стеком(стековой памятью) называется область памяти, которая организована по принципу "Последний пришел, первый вышел".

Регистр команд - хранит код команды на протяжении всего времени выполнения команды.

Регистр адреса и регистр данных - предназначены для хранения адресов и данных, используемых во время выполнения текущей команды в МП.

Регистр состояния(регистр флагов) - предназначен для хранения информации, результате операций в АЛУ, и представляет собой несколько триггеров.

В зависимости от порядка и набора команд процессоры разделяются на 2 класса:

1)CISC(complete instruction set computer) - они имеют классическую архитектуру с большим набором команд различного формата. Процессору требуется в среднем 10 тактов для выполнения 1 команды.

2)Для повышения производительности была разработана архитектура RISC - она характеризуется сокращенным набором быстро исполняемых команд. Они могут выполнять по 1 команде в каждом такте. В сокращенный набор входят только наиболее часто используемые команды. сложные операции выполняются последовательностями коротких команд RISC.

Основные показатели процессоров

Показатели процессоров служат для показательной оценки их функциональных возможностей, качества выполняемых функций и аппаратной реализации.

1)Тактовая частота - по значению тактовой частоты можно судить о быстродействии процессора, так как длительность 1 процессорного такта  определяет минимальное время, отводимое процессору на выполнение операции.

определяет минимальное время, отводимое процессору на выполнение операции.

2)Показатели степени интеграции - количество транзисторов в 1 кристалле микросхемы.

3)Размеры или площадь кристалла - более 300мм2.

4)Минимальное расстояние между компонентами БИС

5)Энергетические показатели - напряжение питания, потребляемый ток, потребляемая мощность.

6)Производительность процессора - используется для оценки быстродействия процессора. Тактовая частота дает косвенное представление о быстродействии, так как команда может включать в себя выполнение нескольких микроопераций. Критерием для оценки быстродействия может служить количество команд, выполняемых за 1 процессорный такт. В первых процессорах на выполнение 1 команды уходило в среднем 12 тактов. Современные процессоры благодаря использованию новых архитектур и технологий способны выполнять несколько команд за 1 такт.

Для сравнения процессоров с различной архитектурой и разными тактовыми частотами была разработана система тестов iCOM 2.0 - индекс сравнительной эффективности микропроцессоров Intel. Уровень индекса определяется выполнение процессора программных тестовых смесей.

Раздел 2

Универсальные микропроцессоры

Универсальные МП предназначены для применения в компьютерной технике (ПЭВМ)

Структурная схема микропроцессора Intel 8086

В МП Intel 8086 применена конвейерная архитектура, которая позволяет совмещать во времени циклы исполнения и выборки из памяти кодов последующих команд. Это достигается параллельной работой 2 независимых устройств - операционного устройства и шинного интерфейса. ОУ выполняет команды, а ШИ осуществляет взаимодействие с внешней шиной - выставляет адреса, считывает коды команд и операнды. Записывает результаты вычислений в память или УВВ. ОУ состоит из регистров общего управления, предназначенных для хранения промежуточных результатов вычислений; АЛУ с буферными регистрами; регистры флагов; схем управления и синхронизации, которая дешифрует коды команд и генерирует управляющий сигнал для всех блоков управления.

ШИ состоит из 6-байтной регистровой памяти, которая называется очередью команд, 4-сегментных регистров CS, DS, ES, SS, указателя команд IP, сумматора, а так же вспомогательных регистров связи и буферных схем шин адреса/данных. Очередь команд работает по принципу FIFO(первый зашел, первый вышел) и сохраняет на выходе порядок поступления команд. Длина очереди 6 байт, если ОУ заняты выполнением команды, ШИ самостоятельно инициирует опережающую выборку кодов команды из памяти в очередь команд. выборку из памяти очередного командного слова осуществляется, когда в очереди обнаруживается 2 свободных байта. Очередь увеличивает быстродействие процессора в случае последовательного выполнения команд. При выборке команд переходов и возвращений из подпрограмм, обработки запросов прерываний очередь команд сбрасывается и выборка начинается с нового места программной памяти. Кроме того шинный интерфейс формирует физический 20-разрядный адрес из двух 16-разрядных слов. Первым словом является содержимое одного из сегментных регистров: первое из CS, DS, ES, SS, а второе зависит от типа адресации операнда или кода команды. Суммирование 16-разрядных слов происходит со смещение на четыре разряда и осуществляется с помощью сумматора, который входит в состав ШИ.

Назначение контактов БИС зависит от режима работы МП. Восемь контактов имеют двойное назначение. Условно все сигналы можно разделить на 9 групп:

1)Сигналы адреса данных - сначала передаются 16 бит адреса с А15-А0, а затем данные Д15-Д0

2)Старшие разряды адреса А19-А16

3)  - сигнал разрешения старшего байта. Служит для подключения банков памяти к шине данных. Инверсия показывает, что активным уровнем сигнала является низкий.

- сигнал разрешения старшего байта. Служит для подключения банков памяти к шине данных. Инверсия показывает, что активным уровнем сигнала является низкий.

4)STB - строб адреса предназначен для загрузки адреса из МП во внешний регистр адреса. Сначала фиксируются адреса, а потом передаются данные.

5)Сигналы управления шиной - предназначены для управления шиной. Показывают, в каком направлении идет передача данных (в МП или из МП) и с каким устройством идет обмен данными(с ЗУ или ВУ). Все эти сигналы 3-стабильные(могут быть в 3 состояниях). #RD - считывание данных из памяти в МП. #WR - запись данных из МП в ЗУ или ВУ. M/#IO(память/ВУ) - показывает с каким устройством идет взаимодействием МП.

6)Сигналы управления запросом:

HOLD (запрос/захват шины) - входной сигнал, поступающий от контроллера прямого доступа к памяти(КПДП), если УВВ требует обмена в режиме ПДП.

HLDA (подтверждение запроса) - этим сигналом МП подтверждает, что он перешел в режим захвата. При этом МП приостанавливает выполнение команд и переводит ША и ШД, а так же некоторые управляющие сигналы в 3-е состояние. После этого системной шиной управляет КПДП.

| А15 |

8)Сигналы управления прерываниями

Входные:

NMI — запрос немаскируемого прерывания. Распознается всегда по положительному фронту после завершения текущей команды независимо от того, разрешены или запрещены прерывания.

INTR — запрос маскируемого прерывания. МП реагирует на этот сигнал, если прерывания разрешены. Сигнал INTR запрещается с помощью внутреннего триггера прерывания IF.

Прерывания по INTR запрещены, если IF сброшен в ноль. Программный сброс IF производится командой CLI. Прерывания разрешаются командой STI.

Замечание. При подаче сигнала INTR триггер IF сбрасывается в 0.

#INTA — подтверждение прерывания. Показывает, что МП перешел в режим работы по прерыванию;

9) сигналы для управления работой МП.

RDY — готовность. При RDY=0 приостанавливается действие МП на время чтения или записи данных на неопределенное число тактов Tw, появляющихся после такта ТЗ машинного цикла. Сигнал RDY позволяет организовать интерфейс МП с медленно действующими ЗУ и ВУ, у которых время обращения Тобр>Т=200 нс

Замечание. В простейших МПС с небольшим объемом памяти целесообразно использовать быстродействующие статические ЗУ. Тогда RDY=1.

10) #TEST — проверка. Используется вместе с командой WAIT. Выполняя ее, МП проверяет значение сигнала #TEST. Если #TEST=0, то МП переходит к выполнению следующей команды. Если #TEST=1, то вводятся холостые такты Т порядка пяти тактов и снова повторяется команда WAIT. Значение #TEST задается извне и является входным сигналом.

CLR (RESET) — сброс. С помощью сигнала CLR МП переходит в начальное состояние. При первом сбросе длительность должна быть 50 мкс. При повторном сбросе длительность должна быть больше четырех тактов (800 не). При подаче CLR=1 все выходные линии МП переходят в третье состояние. После снятия этого сигнала все выходные линии активны. По сигналу CLR внутренние регистры МП устанавливаются следующим образом:

DS, SS, ES, IP=0000;IF=0 (прерывания запрещены); CS=FFFF.

Значения остальных регистров не определены. На ША выставляется физический адрес (ФА):

ФA=CS×24+IP=FFFF0h.

Поэтому первую команду программы размещают по адресу FFFF0.

CLK — синхронизация. На этот вход подаются сигналы синхронизации от внешнего генератора К1810ГФ84 с частотой F=5 МГц.

MN/#MX — минимальный/максимальный режим. Определяет режим работы МП:

MN/#MX=0 — максимальный;

MN/#MX=1 — минимальный.

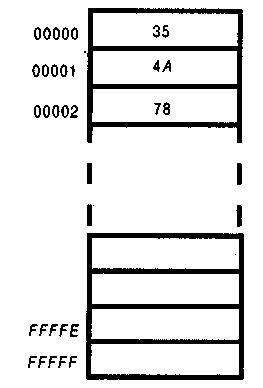

Организация памяти. Память представляет собой массив емкостью 1 Мбайт, т. е. 220 8-разрядных ячеек (рис. 2.4).

Рис. 2.4. Программная модель памяти

В памяти хранятся как байты, так и 16-разрядные слова. Слова располагаются в двух соседних ячейках памяти: старший байт хранится в ячейке со старшим адресом, младший — в ячейке с младшим адресом. Адресом слова считается адрес его младшего байта. Начальные (00000Н—003FFH) и конечные адреса (FFFF0H—FFFFFH) зарезервированы для системы прерываний и начальной установки соответственно.

Для формирования 20-разрядного адреса в 16-р процессоре используют информацию двух 16-р регистров. В МП i8086 20-разрядный адрес формируется из двух 16-р адресов, которые называют логическими.

Первый логический адрес, дополненный справа четырьмя нулями, представляет собой начальный адрес сегмента емкостью 64 Кбайт. Второй логический адрес определяет смещение в сегменте, т. е. определяет расстояние от начала сегмента до адресованной ячейке. Таким образом, логическое адресное пространство разделено на блоки соседних адресов емкостью 64 Кбайт, т. е. сегменты.

Такой подход к организации памяти удобен также потому, что память обычно логически делится на области кода (программной памяти), данных и стека.

Физический 20-разрядный адрес ячейки памяти формируется из двух 16-разрядных адресов — адреса сегмента Seg и исполнительного адреса ЕА (Executive Address), которые суммируются со смещением на четыре разряда.

Рис. 2.5. Формирование физического адреса

Смещение адреса сегмента на 4 разряда влево эквивалентно его умножению на 24. Следовательно, физический адрес равняется 16 × Seg + ЕА.

В качестве первого логического адреса Seg используется содержимое одного из четырех сегментных регистров: CS (Code Segment — сегмент кодов), DS (Data Segment — сегмент данных), ES (Extended Segment — дополнительный сегмент данных), SS (Stack Segment — сегмент стека). Второй логический адрес ЕА, или смещение, зависит от сегмента. Так, в сегменте кодов ЕА используется содержимое указателя команд IP, в сегментах данных значение ЕА зависит от средства адресации операнда, в сегменте стека для указания второго логического адреса используются регистры SP или ВР.

Емкость памяти 1 Мбайт, начиная с нулевого адреса, разбивается на параграфы по 16 байт. Сегмент может начинаться только на границе параграфа, т. е. в адресе сегмента младшие четыре бита — нулевые. Размещение сегментов в памяти произвольное: сегменты могут частично или полностью перекрываться либо не иметь общих областей. Изменяя значения первого и второго логических адресов, можно адресовать любую ячейку из общей памяти емкостью 1 Мбайт.

Начальные адреса сегментов определяются содержимым 16-разрядных сегментных регистров, которые дополнены справа четырьмя нулевыми битами. Смещение в сегменте кодов определяется содержимым регистра IP, смещение в сегменте данных и дополнительном сегменте данных — эффективным адресом ЕА, который указывается в команде, смещение в сегменте стека — содержимым регистра SP.

В сегментах кодов расположены коды команд, т. е. программа в машинных кодах; в остальных сегментах — данные. Изменяя содержимое сегментных регистров, можно передвигать сегменты в границах всей памяти 1 Мбайт. Сегменты кодов, данных, стека и дополнительного сегмента могут частично перекрываться.

Программная модель. Программная модель МП i8086 состоит из РОН, сегментных регистров, указателя команд и регистра флагов. Регистры общего назначения делятся на регистры данных и регистры-указатели. К регистрам данных относятся четыре 16-разрядных регистра: АХ, ВХ, СХ, DX. Любой из этих регистров состоит из двух 8-разрядных регистров, которые можно независимо адресовать символическими именами АН, ВН, СН, DH (старшие байты — High) и AL, BL, CL, DL (младшие байты — Low). Регистры-указатели SP (Stack Pointer, указатель стека), ВР (Base Pointer, базовый регистр, SI (Source Index, индекс источника), DI (Destination Index, индекс назначения) являются 16-разрядными и предназначены, как правило, для хранения адресов операндов при косвенной адресации.

Все РОН можно использовать для хранения данных, но в некоторых командах допускает использование определенного регистра по умолчанию: АХ — при умножении, делении, вводе и выводе слов; AL — при умножении, делении, вводе и выводе байтов, десятичной коррекции, преобразовании байтов (команда XLAT); АН — при умножении и делении байтов; ВХ — при трансляции; СХ — как счетчик циклов и указатель длины строк в строчных командах; CL — для хранения числа сдвигов в командах; DX — при умножении и делении слов, вводе и выводе с косвенной адресацией; SP — при операциях со стеком; SI, DI — при строковых операциях. В регистре SP хранится смещение последней занятой ячейки стека относительно начала сегмента стека, а полный адрес стека определяется как SS:SP. Сегментные регистры CS, DS, ES, SS определяют начальные адреса четырех сегментов памяти. Использование сегментных регистров определяется типом обращения к памяти (выборка команд, стековые операции…).

Для некоторых типов обращений допускается замена сегментного регистра по умолчанию на альтернативный, что осуществляется использованием префиксов CS:, DS:, SS:, ES:. Регистр флагов хранит признаки результатов выполнения арифметических и логических операций и управляющие признаки. Последние можно установить или сбросить программно.

19.02.2013

Регистр флага - хранит признаки результатов выполнения арифметических и логических операций и управляющие признаки. Последнее может установить или сбросить программно.

CF (CARRY FLAG) – флаг переноса (заёма ) старшего разряда в арифметических операциях.

PF (PARITY FLAG) – флаг паритета, устанавливается при чётном числе единиц в результате.

AF (AUXILIERY FLAG) – флаг дополнительного переноса (заёма) в тетраде для десятичной арифметики.

ZF (ZERO FLAG) – флаг нулевого результата.

SF (SIGN FLAG) – флаг знака. Указывает на единичное значение старшего бита результата – признак отрицательного числа.

TF (TRAP FLAG) – флаг трассировки (пошагового режима). При его установке после выполнения каждой команды вызывается внутреннее прерывание 1 (INT1).

IF (INTERRUPT FLAG) – флаг управления прерыванием. При единичном его значении разрешается выполнение маскируемых аппаратных прерываний.

DF (DIRECTION) – флаг управления направлением в строковых операциях, автоматически декрементируется(уменьшается_ на установленное количество байт операнда, при нулевом – инкрементируется(увеличивается).

OF (OVERFLOW FLAG) – флаг переполнения Устанавливается если результат арифметической операции не помещается в операнде назначения.

Рис. 2.6.Программная модель МП 18086

Особую роль играют 16-р регистры указатели сегментов CS, DS, SS, ES.они Эти могут модифицироваться только непосредственно – командами их загрузки.

|

из

5.00

|

Обсуждение в статье: Архитектура процессора |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы