|

Главная |

Комбинационные логические схемы

|

из

5.00

|

Рисунок 1. Функциональная схема цифрового комбинационного устройства

Комбинационная логическая схема – это преобразователь совокупности входных логических уровней (входного слова или входного кода) в выходное слово (выходной код) без запоминания. При изменении входных сигналов практически мгновенно изменяется код на выходе устройства. Небольшая временная задержка, вносимая комбинационной схемой, обусловливается в основном инерционностью транзисторов. Наиболее часто встречающимися комбинационными логическими схемами являются шифраторы, дешифраторы, мультиплексоры.

Дешифратор

Дешифратор- это логическая схема, которая каждую комбинацию сигналов на ее входе, в результате логической обработки, выдает в виде сигнала на одном из ее выходов (при нулевых сигналах на всех остальных выходах). Такая операция широко используется при автоматическом управлении. Дешифраторы также используются при переходе из одной системы исчисления в другую. В качестве отдельных микросхем сейчас дешифраторы практически не применяются. В настоящее время двоичные дешифраторы вместе с мультиплексорами используются в составе микросхем памяти (ОЗУ и ПЗУ) для обращения к конкретной ячейке памяти.

Шифратор

В дополнение к дешифраторам в вычислительной технике используется шифратор- цифровое устройство, выполняющее логические операции, обратные функциям дешифратора. Шифратор преобразует одну или несколько логических единиц, поступивших на входы в двоичный код на выходе. Шифраторы используются, например, в устройствах ввода цифровой информации для преобразования десятичных чисел в двоичный код.

Мультиплексор

Мультиплексор — устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передавать сигнал с одного из входов на выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов.

Числовые коды

Числовым кодом называют форму представления числа, удобную для различных дискретных устройств.

Каждый числовой код состоит из отдельных элементов или сигналов.

Рассмотрим следующие типы кодов: Двоично-десятичный код 8421, Код с избытком 3, Код Грея.

Двоично-десятичный код 8421

Наиболее естественным и популярным считается упоминавшийся код прямого замещения, в котором каждая цифра десятичного числа заменяется соответствующим четырехразрядным двоичным числом. Его другое название код 8421 отражает значение весовых множителей, приписываемых соответствующим битам в кодирующей группе, в связи с чем называется также взвешенным кодом. Удобства этого кода проявляются при машинном переводе из десятичной системы в двоичную и обратно, а также при суммировании на обычных двоичных сумматорах благодаря его аддитивности (сумма кодов двух цифр представляет код суммы).

Двоично-десятичный код (англ. binary-coded decimal), BCD, 8421-BCD — форма записи рациональных чисел, когда каждый десятичный разряд числа записывается в виде его четырёхбитного двоичного кода. Этот код широко применяется в цифровых системах.

Пример: 926 ► 1001 0010 0110

Код с избытком 3

Код с избытком 3 – самодополняющийся код. Реализация: прибавляем число 3 к каждой цифре десятичного числа и затем заменяем полученные цифры соответствующими четырёхзначными двоичными числами. Для предотвращения потерь информации в канале были придуманы избыточные коды (коды с избыточностью). Преимущество избыточного кода в том, что при приеме его с искажением (количество искаженных символов зависит от степени избыточности и структуры кода) информация может быть восстановлена на приемнике.

Код Грея

Среди невзвешенных двоичных кодов специальные применения находят такие, у которых переход к соседнему числу сопровождается изменениями только в одном разряде (коды с обменной единицей). Так, в технике аналого-цифрового преобразования и пересчетных устройствах широко используется код Грея, называемый также циклическим или рефлексно-двоичным кодом.

Код Грея — система счисления, в которой два соседних значения различаются только в одном разряде. Важной особенностью кода Грея является то, что при переходе к следующему, ниже расположенному числу достаточно в предыдущем числе изменить только одну цифру. Он позволяет существенно сократить время преобразования, упростить кодирующую логику, а также повысить эффективность защиты от нежелательных сбоев при переходах выходного кода. Недостатком кода Грея является то, что в нем затруднено выполнение арифметических операций и цифроаналоговое преобразование. Поэтому при необходимости код Грея преобразуется в обычный двоичный код. Этот код применяется во входных и выходных устройствах цифровых систем.

Преобразователи кодов

Преобразователем кода называется комбинационное устройство, предназначенное для изменения вида кодирования информации. Для реализации комбинационных схем используются логические элементы, выпускаемые в виде интегральных схем. В этот класс входят интегральные схемы дешифраторов, шифраторов, мультиплексоров, демультиплексоров и сумматоров.

Дешифраторы

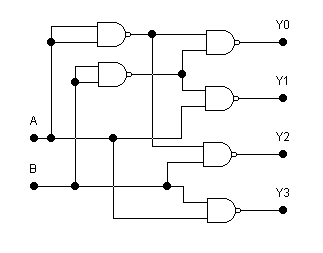

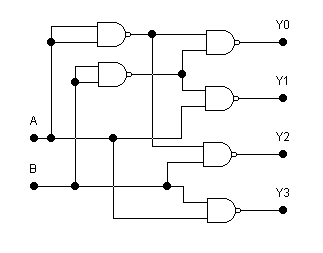

Дешифратором (декодером) называется логическая комбинационная схема, которая имеет n информационных входов и 2n выходов. Каждой комбинации логических уровней на входах будет соответствовать активный уровень на одном из 2n выходов. Для интегральных микросхем n обычно равно 2, 3 или 4 и соответственно число выходов 4, 8 или 16. Если требуется большее число выходов, дешифраторы наращиваются в систему (каскадируются). На рис. 3.1 изображен дешифратор с n = 2, реализованный на схемах 2И-НЕ.

Рисунок 3.1 — Схема дешифратора на элементах 2И-НЕ

Таблица истинности дешифратора приведена в таблице 3.1

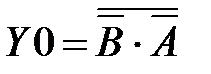

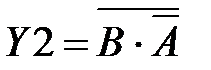

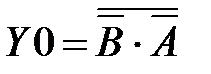

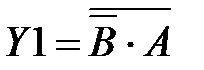

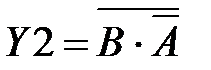

В соответствии с таблицей истинности для каждого выхода дешифратора, приведённого на рисунке 3.1 можно записать следующие логические выражения:

,

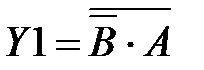

,

,

,

,

,

.

.

Таблица 3.1 — Таблица истинности дешифратора

| Входы | Выходы | ||||

| B | A | Y3 | Y2 | Y1 | Y0 |

| 0 | 0 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 |

Помимо информационных входов А, В дешифраторы могут иметь дополнительные входы управления G. Сигналы на этих входах либо разрешают функционирование дешифратора, либо переводят его в пассивное состояние, при котором, независимо от состояния информационных входов, на всех выходах устанавливается уровень логической единицы. Управляющий вход дешифратора может быть прямым или инверсным.

У дешифратора с несколькими входами управления функция разрешения, как правило, представляет собой логическое произведение всех разрешающих сигналов управления.

Обычно входы управления используются для каскадирования (увеличения разрядности) дешифраторов или при параллельной работе нескольких дешифраторов на общие выходные линии.

Дешифратор может быть использован в качестве демультиплексора - логического коммутатора, подключающего входной сигнал к одному из выходов. В этом случае функцию информационного входа выполняет один из входов разрешения, а состояние входов В и А задает номер выхода, на который передается сигнал со входа разрешения.

Шифраторы (кодеры)

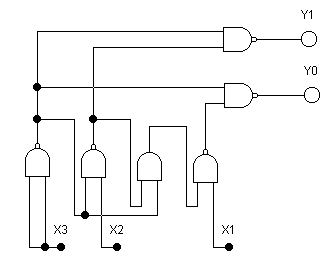

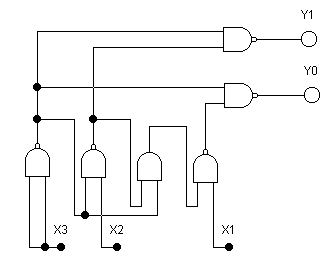

Двоичные шифраторы преобразуют код «1 из N» в двоичный код. Если дешифратор реализует логическую функцию преобразования двоичного кода в единичный, то шифратор реализует обратную функцию, то есть преобразует единичный код в двоичный. Наиболее часто используются шифраторы с приоритетом, на выходах которого формируется двоичное число, соответствующее наивысшему из входов, на который подана логическая единица. Такие шифраторы чаще всего используются в аналого-цифровых преобразователях. Одно из основных применений шифраторов – это ввод данных с клавиатуры, при котором нажатие клавиши с десятичной цифрой должно приводить к передаче в устройство двоичного кода данной цифры. На рисунке 3.2 приведена схема двухразрядного приоритетного шифратора. Таблица истинности приоритетного шифратора приведена в таблице 3.2

Таблица 3.2 — Таблица истинности приоритетного кодера

| Входы | Выходы | |||

| X3 | X2 | X1 | Y1 | Y0 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | × | 1 | 0 |

| 1 | × | × | 1 | 1 |

Примечание: Знаком × обозначается произвольное значение (либо 0, либо 1)

Рисунок 3.2 — Двухразрядный приоритетный шифратор на элементах 2И-НЕ

Мультиплексоры

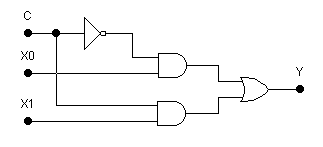

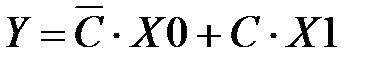

Мультиплексором называется комбинационная логическая схема, представляющая собой управляемый переключатель. Назначение мультиплексоров (от английского multiplex — многократный) — коммутировать в заданном порядке сигналы, поступающие с нескольких входных шин на одну выходную. В качестве примера рассмотрим мультиплексор, у которого 16 входов и 1 выход. Это означает, что если к этим входам присоединены 16 источников цифровых сигналов — генераторов последовательных цифровых слов, то байты от любого из них можно передавать на единственный выход. Для выбора любого из 16 каналов необходимо иметь 4 управляющих входа (24 = 16), на которые подается двоичный адрес канала. Кроме информационных и управляющих входов, схемы мультиплексоров содержат вход разрешения, при подаче на который активного уровня мультиплексор переходит в активное состояние. При подаче на вход разрешения пассивного уровня мультиплексор переходит в пассивное состояние, в котором его выходной сигнал остаётся постоянным независимо от состояний информационных и управляющих входов.

Мультиплексоры применяются в микропроцессорах (МП) для выдачи на одни и те же выводы МП адреса и данных, что позволяет существенно сократить общее количество выводов микросхемы. В микропроцессорных системах управления мультиплексоры применяются для передачи информации по одной линии от нескольких датчиков.

Схема двухканального мультиплексора на элементах 2И, 2ИЛИ и инверторе приведена на рисунке 3.3.

Рисунок 3.3 — Схема двухканального мультиплексора

Схема двухканального мультиплексора реализует функцию:

.

.

Демультиплексоры

Иногда возникает задача распределения одного входного сигнала по нескольким различным адресам. С помощью демультиплексоров сигналы с одного информационного входа распределяются в требуемой последовательности по нескольким выходам. Выбор нужной выходной шины, как и в мультиплексоре, обеспечивается установкой соответствующего кода на адресных управляющих входах. При n адресных входах демультиплексор может иметь до 2n выходов. Промышленностью демультиплексоры не выпускаются, потому что они могут быть реализованы на основе дешифраторов. На рисунке 3.4 приведена схема демультиплексора, реализованная на двух логических элементах 2И и инверторе.

Рисунок 3.4 — схема демультиплексора

Демультиплексор реализует следующие логические функции:

,

,

.

.

Сумматоры - это цифровые функциональные устройства, предназначенные для выполнения операции сложения чисел, представленных в различных кодах.

По характеру действия сумматоры подразделяются на комбинационные, не имеющие элементов памяти, и накапливающие – запоминающие результаты вычислений при снятии входных сигналов.

В дальнейшем будут рассматриваться только комбинационные сумматоры, на основе которых выполняется большинство суммирующих ИС.

Сумматор по модулю два - Это устройство с двумя входами (а и b), на выходе у которого сигнал "1" появляется только в том случае, когда на входах действуют противоположные сигналы, т. е. "0" и "1". Сумматор не обладает памятью.

Eго таблица истинности и логическое уравнение имеют вид:

Название “по модулю два” этот сумматор получил потому, что y соответствует значению младшего разряда при суммировании одноразрядных двоичных чисел A и B. Построим в базисе И–НЕ схему сумматора по модулю два (рис. 21)

Рис. 21. Реализация сумматора по модулю два:

а – принципиальная схема; б – функциональная схема

Полусумматор - Обеспечивает операцию сложения двух одноразрядных двоичных чисел a и b. Так как при a = 1 и b = 1 получается перенос единицы в следующий разряд, полусумматор должен иметь два выхода: с одного снимается сигнал суммы по модулю два, а с другого - сигнал переноса.

Таблица истинности полусумматора и его логические уравнения имеют вид:

P' = ab

Реализация полусумматора в базисе И–НЕ представлена на рис. 22

а б

Рис. 22. Схема полусумматора:

а – реализация в базисе И–НЕ; б – условное обозначение

Условное обозначение полусумматора на схемах – HS (halfsum – полусумма), а полного сумматора – SM.

Полный сумматор - Это устройство для сложения трех одноразрядных двоичных чисел a, b, c, где c - сигнал переноса из предыдущего младшего разряда. Имеет два выхода S (сумма) и Р (перенос).

Полный сумматор можно построить из двух полусумматоров (рис. 23), отсюда и название – полусумматор, используя следующие логические уравнения

Рис. 23. Полный сумматор

На основе полного сумматора можно построить суммирующие устройства параллельного или последовательного действия для сложения многоразрядных двоичных чисел.

Дешифратор

Дешифратором (декодером) называется логическая комбинационная схема, которая имеет n информационных входов и 2n выходов. Каждой комбинации логических уровней на входах будет соответствовать активный уровень на одном из 2n выходов. Для интегральных микросхем n обычно равно 2, 3 или 4 и соответственно число выходов 4, 8 или 16. Если требуется большее число выходов, дешифраторы наращиваются в систему (каскадируются). На рис. 3.1 изображен дешифратор с n = 2, реализованный на схемах 2И-НЕ.

Рисунок 3.1 — Схема дешифратора на элементах 2И-НЕ

Таблица истинности дешифратора приведена в таблице 3.1

В соответствии с таблицей истинности для каждого выхода дешифратора, приведённого на рисунке 3.1 можно записать следующие логические выражения:

,

,

,

,

,

,

.

.

Таблица 3.1 — Таблица истинности дешифратора

| Входы | Выходы | ||||

| B | A | Y3 | Y2 | Y1 | Y0 |

| 0 | 0 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 |

Помимо информационных входов А, В дешифраторы могут иметь дополнительные входы управления G. Сигналы на этих входах либо разрешают функционирование дешифратора, либо переводят его в пассивное состояние, при котором, независимо от состояния информационных входов, на всех выходах устанавливается уровень логической единицы. Управляющий вход дешифратора может быть прямым или инверсным.

У дешифратора с несколькими входами управления функция разрешения, как правило, представляет собой логическое произведение всех разрешающих сигналов управления.

Обычно входы управления используются для каскадирования (увеличения разрядности) дешифраторов или при параллельной работе нескольких дешифраторов на общие выходные линии.

Дешифратор может быть использован в качестве демультиплексора - логического коммутатора, подключающего входной сигнал к одному из выходов. В этом случае функцию информационного входа выполняет один из входов разрешения, а состояние входов В и А задает номер выхода, на который передается сигнал со входа разрешения.

Шифратор

Шифратор преобразует единичный код в двоичный. Наиболее часто используются шифраторы с приоритетом, на выходах которого формируется двоичное число, соответствующее наивысшему из входов, на который подана логическая единица. Такие шифраторы чаще всего используются в аналого-цифровых преобразователях. Одно из основных применений шифраторов – это ввод данных с клавиатуры, при котором нажатие клавиши с десятичной цифрой должно приводить к передаче в устройство двоичного кода данной цифры. На рисунке 3.2 приведена схема двухразрядного приоритетного шифратора. Таблица истинности приоритетного шифратора приведена в таблице 3.2

Таблица 3.2 — Таблица истинности приоритетного кодера

| Входы | Выходы | |||

| X3 | X2 | X1 | Y1 | Y0 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | × | 1 | 0 |

| 1 | × | × | 1 | 1 |

Примечание: Знаком × обозначается произвольное значение (либо 0, либо 1)

Рисунок 3.2 — Двухразрядный приоритетный шифратор на элементах 2И

|

из

5.00

|

Обсуждение в статье: Комбинационные логические схемы |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы