|

Главная |

Логические элементы на МДП-транзисторах

|

из

5.00

|

В настоящее время в логических схемах используются МДП-транзисторы с диэлектриком SiO2 (МОП-транзисторы).

Анализ МОП-транзисторных логических элементов достаточно прост, т.к. из-за отсутствия входных токов их можно рассматривать отдельно от других элементов даже при работе в цепочке.

Рис.13.15.

Схема и передаточная характеристика логического элемента «НЕ» (комплементарного ключа)приведена на рис. 13.15.

Чтобы высокий и низкий уровни  и

и  инвертора максимально приближались к напряжениям

инвертора максимально приближались к напряжениям  и 0 В, необходимо выполнить следующее условие как для n-канального, так и p-канального транзистора: сопротивление канала

и 0 В, необходимо выполнить следующее условие как для n-канального, так и p-канального транзистора: сопротивление канала  <<

<<  . Это условие выполняют для специально конструируемых мощных инверторов КМОП, работающих на выходах микросхем. Напомним, что малое сопротивление канала

. Это условие выполняют для специально конструируемых мощных инверторов КМОП, работающих на выходах микросхем. Напомним, что малое сопротивление канала  равноценно повышенной крутизне усиления S полевого транзистора. Пределы

равноценно повышенной крутизне усиления S полевого транзистора. Пределы  и

и  для оконечных буферных инверторов обычно оговариваются. Если их превысить, структура может разрушиться. Оконечные транзисторы с большой крутизной занимают значительную часть площади кристалла микросхемы.

для оконечных буферных инверторов обычно оговариваются. Если их превысить, структура может разрушиться. Оконечные транзисторы с большой крутизной занимают значительную часть площади кристалла микросхемы.

Достоинства КМОП логики, как и у комплементарных ключей, является то, что она практически не потребляет мощности как в закрытом, так и в открытом состоянии.

Время переключения можно свести к минимальному, применив транзисторы в комплементарной паре с одинаковым пороговым напряжением. Технологическими способами для этого является равенство сопротивлений каналов обоих транзисторов  и

и  , что позволит уменьшить выходные фронты ЛЭ t0,1 и t1,0 и приблизить к идеальной форму передаточной характеристики.

, что позволит уменьшить выходные фронты ЛЭ t0,1 и t1,0 и приблизить к идеальной форму передаточной характеристики.

На рис. 13.16 показаны два варианта построения логических элементов на МОП-транзисторах с n-каналами.

Рис. 13.16. Логические элементы на МОП-транзисторах: а) – элемент ИЛИ-НЕ, б) – элемент И-НЕ

Транзисторы Т3 выполняют роль нагрузки. Логические уровни в обеих схемах не зависят от нагрузки и соответствуют выходным напряжениям открытого и закрытого ключа:  Соответственно, логический перепад составляет:

Соответственно, логический перепад составляет:

.

.

Напряжение питания Ec МОП-логики выбирают в 3…4 раза больше порогового напряжения Uo открывания транзисторов.

Более высоким быстродействием и низким энергопотреблением характеризуется логика на комплементарных транзисторах- КМОП-логика.

На базе МОП-транзисторов с индуцированным n-каналом строятся ячейки динамических запоминающих устройств. Электрическая схема такого элемента памяти и его структура приведены на рис. 13.17, а, б соответственно.

Адресной шиной является область “3”затвора, разрядная шина “РШ” – это область истока, к которой подведен слой металлизации“1”, область стока со слоем “4” из поликристаллического кремния образует емкость относительно подложки “  ” запоминающего элемента. Область “2”– изоляционный слой окисла кремния.

” запоминающего элемента. Область “2”– изоляционный слой окисла кремния.

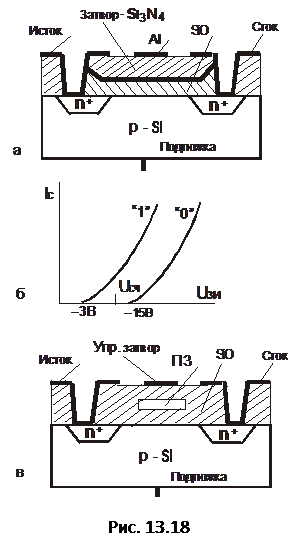

Функции элементов памяти могут также выполнять транзисторы со структурой МНОП (Металл Al — Нитрид кремния SiN4 — Окисел кремния Si02—Полупроводник Si) или транзисторы со структурой ЛИЗМОП (Металл – Окисел кремния – Полупроводник с Лавинной Инжекцией Заряда).

На их основе строятся микросхемы РПЗУ (Репрограммируемых Запоминающих Устройств). Их подразделяют на две группы: стираемые электрическим сигналом (ЭСППЗУ) и стираемые УФ-излучением (СППЗУ). Микросхемы ЭСППЗУ содержат элементы памяти типа МНОП или ЛИЗМОП с двойным затвором.

Рис. 13.17

В микросхемах СППЗУ применяется также ЛИЗМОП-элемент памяти (ЭП) с двойным затвором, отличающийся от аналогичных ЭП в микросхемах ЭСППЗУ тем, что требует для стирания УФ-излучение. Элемент памяти со структурой МНОП представляет собой МОП-транзистор с индуцированным каналом n – или р-типа, имеющий двуслойный диэлектрик под затвором. Верхний слой сформирован из нитрида кремния, нижний – из окисла кремния, причем нижний слой значительно тоньше верхнего.

Если к затвору относительно подложки приложить импульс напряжения положительной полярности с амплитудой 30...40 В, то под действием сильного электрического поля между затвором и подложкой электроны получат достаточную энергию, чтобы преодолеть тонкий диэлектрический слой и попасть на границу раздела двух диэлектриков.

Поскольку верхний слой имеет значительную толщину, то электроны не могут его пройти и накапливаются внутри подзатворного слоя. Накопленный под затвором заряд электронов снижает пороговое напряжение МНОП-транзистора и тем самым смещает передаточную характеристику влево (рис. 2.20, а, б).

Состояние ЭП с зарядом под затвором соответствует лог. 1. Состояние ЭП без заряда под затвором соответствует лог. 0. В этом состоянии передаточная характеристика МНОП-транзистора занимает положение с более высоким порогом отпирания. Процесс программирования микросхем ЭСППЗУ происходит в два этапа. На первом этапе стирают информацию во всех МНОП-элементах памяти.

Для этого импульсом напряжения отрицательной полярности, прикладываемым на затвор относительно подложки амплитудой 30…40 В, электроны вытесняются из подзатворного диэлектрика в подложку. Следовательно, при стирании информации элемент памяти получает состояние лог. 0. На втором этапе производят выборочную запись в нужные ЭП лог. 1 импульсом напряжения положительной полярности, подаваемым на затвор относительно подложки.

На практике режимы стирания и записи осуществляют напряжением одной полярности: отрицательной для р-МНОП-элементов и положительной для n-МНОП-элементов памяти.

На практике режимы стирания и записи осуществляют напряжением одной полярности: отрицательной для р-МНОП-элементов и положительной для n-МНОП-элементов памяти.

Эта возможность основана на использовании явления лавинной инжекции электронов под затвор, которая происходит при соединении затвора с подложкой и подаче на сток и исток импульса напряжения относительно подложки и затвора такой полярности, чтобы переходы между подложкой и стоком (истоком) оказались под обратным смещением. Амплитуда импульса должна быть достаточной для возникновения в переходах электрического пробоя.

Типичные значения напряжения программирования лежат в пределах 20…30 В. В результате электрического пробоя переходов в них происходит лавинное размножение носителей заряда и инжекция части этих носителей, обладающих достаточной кинетической энергией, на границу между слоями подзатворного диэлектрика.

При считывании на затвор подают напряжение  , значение которого лежит между двумя пороговыми уровнями. Если в МНОП-транзистор записана единица, то он откроется, а при нуле останется в закрытом состоянии. Микросхемы на n-МНОП-транзисторах обладают втрое большим быстродействием, чем на р-МНОП, сниженным до 21…25 В напряжением программирования и работают от одного источника питания.

, значение которого лежит между двумя пороговыми уровнями. Если в МНОП-транзистор записана единица, то он откроется, а при нуле останется в закрытом состоянии. Микросхемы на n-МНОП-транзисторах обладают втрое большим быстродействием, чем на р-МНОП, сниженным до 21…25 В напряжением программирования и работают от одного источника питания.

Интегральные триггеры

Триггер - это устройство, имеющее два устойчивых состояния и способное под действием управляющих сигналов скачкообразно переходить из одного состояния в другое.

Можно выделить две основные области их применения: формирование импульсов и работу в качестве элементарных автоматов цифровых устройств.

Как формирователи, триггеры позволяют получать стандартные по амплитуде прямоугольные импульсы с малой длительностью фронта и среза, практически не зависящей от скорости изменения управляющего сигнала. В роли цифровых автоматов с двумя внутренними состояниями различные типы триггеров выполняют функции ячеек памяти, каскадов задержки, пересеченных ячеек и т. д.

Триггер, как элементарный конечный автомат, характеризуется следующими свойствами:

- число внутренних состояний – два (единица и нуль), что соответствует одной внутренней переменной, обозначаемой для триггеров буквой Q;

- число выходных переменных y – одно, значение переменной y совпадает со значением Q;

- число входных переменных x зависит от типа триггера.

Наряду с выходом Q, называемым прямым, триггер имеет и инверсный выход  . Состояние триггера определяется значением его прямого выхода.

. Состояние триггера определяется значением его прямого выхода.

Все известные на сегодняшний день триггеры по функциональному признаку можно разделить на четыре основных типа:

- RS-триггеры – триггеры с двумя установочными входами;

- D-триггеры – триггеры задержки с одним входом;

- Т-триггеры с одним счетным входом;

- универсальные триггеры с несколькими входами.

Как и любые цифровые автоматы, триггеры могут быть асинхронными и синхронными.

Различают также триггеры со статическими и динамическими входами. Входы, управляемые потенциальными (уровнями напряжений), называются статическими (включая и сигнал синхронизации).

Причем, если триггер переключается сигналами логической единицы, то его называют триггером с прямым управлением, в противном случае – триггером с инверсным управлением.

Входы же управляемые перепадами потенциалов называют динамическими.

Триггеры с динамическим управлением в зависимости от схемы исполнения реагируют на перепад напряжения от нуля к единице, либо от единицы к нулю. Таким образом, сигналы, поступающие на динамический вход, воспринимаются только в те моменты времени, когда их состояние изменяется определенным образом.

Двухступенчатые триггеры содержат первую ступень для промежуточной записи входной информации и вторую – для последующего запоминания и хранения. У двухступенчатых триггеров формирование нового состояния происходит за два такта, поэтому их иногда называют двухтактными.

Рассмотрим основные типы триггеров.

Асинхронный RS-триггер является одним из простейших типов триггеров. В простейшем исполнении триггер это симметричная структура из двух логических элементов ИЛИ–НЕ либо И–НЕ, охваченных перекрестной положительной обратной связью. Схема триггера на элементах ИЛИ–НЕ и его условное обозначение приведены на рис. 13.19

Рис. 13.19 Асинхронный RS-триггер на элементах ИЛИ–НЕ:а – логическая структура; б – условное обозначение

Этот триггер (бистабильная ячейка) обладает двумя устойчивыми состояниями, которые обеспечиваются за счет связи выхода каждого элемента с одним из входов другого. Свободные входы служат для управления и называются информационными или логическими. Одному из выходов присвоено наименование прямого, его обозначают буквой Q, а другому – наименование инверсного и обозначают  .

.

Вход, по которому триггер устанавливается в единичное состояние (Q = 1,  = 0), называют входом S (от английского Set – установка), а в нулевое (Q = 0,

= 0), называют входом S (от английского Set – установка), а в нулевое (Q = 0,  = 1) – входом R (reset – возврат).

= 1) – входом R (reset – возврат).

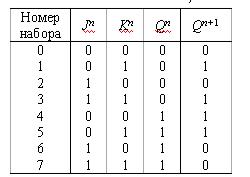

Работа триггера характеризуется таблицей переходов состояний (табл. 6), из которой следует, что на двух наборах переменных его состояние не определено. Карта Карно для нахождения логической функции переходов RS-триггера приведена в таблице 6.

Доопределив ее единицами на запрещенных наборах и применив правила минимизации получим

.

.

Возможны следующие состояния триггера, в зависимости от комбинации входных сигналов:

- Rn, Rn = 0, сигнал на выходе может быть Qn+1 = 1 или Qn+1 = 0, что соответствует нейтральному состоянию (режим хранения информации);

- Sn = 1, Rn = 0, Qn+1 = 1 – установка триггера в единичное состояние;

- Sn = 0, Rn = 1, Qn+1 = 0 – установка в нулевое состояние;

- Sn = 1, Rn = 1 – состояние не определено. Если затем входная комбинация станет Sn = 0, Rn = 0, то триггер с равной вероятностью может установиться или в нулевое, или в единичное состояние, поэтому входная комбинация Sn = 1, Rn = 1 недопустима.

Таблица 6

| Такт tn | Такт tn+1 | ||

| Rn | Sn | Qn | Qn+1 |

| 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 | 0 0 0 0 1 1 1 1 | 0 1 0 – 1 1 0 – |

Минимизированная таблица состояний RS-триггера и его временная диаграмма имеют вид (рис. 13.20):

Рис. 13.20

При синтезе устройств на триггерах возникает задача определения требуемых входных комбинаций для перехода триггера из одного (заданного) состояния Qn в другое (требуемое) Qn+1.

Эту задачу удобно решать с помощью таблицы, называемой матрицей переходов RS-триггера (табл. 7), показывающую сочетания входных сигналов, которые обеспечивают требуемое состояние триггера при его переходе из такта n в такт (n + 1). Если RS-триггер выполнить на элементах И–НЕ, то получим схему, приведенную на рис.13.21.

Такой вариант триггера называют  -триггером или RS-триггером с инверсным управлением.

-триггером или RS-триггером с инверсным управлением.

Рис. 13.21

Синхронный RS-триггер. Известно, что из-за задержек переключения логических элементов могут возникнуть ложные состояния. Устранить это помогает временное стробирование. Временное стробирование обеспечивается синхронизирующими (тактовыми) импульсами, поэтому синхронный RS-триггер кроме информационных входов R и S имеется вход C, на который подается синхронизирующий сигнал (рис. 13.22).

Такой триггер функционирует как RS-триггер только при условии наличия синхронизирующих импульсов. В противном случае, т.е. при отсутствии синхронизирующих импульсов, состояние его сохраняется неизменным Qn+1 = Qn , какие бы сигналы ни подавались на информационные входы, причем возможна подача сочетания R = S = 1 (или R = S = 0 для триггера с инверсными входами).

Рис.13.22 Синхронный RS-триггер с прямыми статическими входами на элементах И-НЕ и его условное обозначение

Специфика синхронных триггеров со статическим управлением по входу синхронизации такова, что в течение времени действия тактового импульса смена сигналов на информационных входах вызывает новые срабатывания. Следовательно, синхронные триггеры со статическим управлением при активном состоянии тактового входа ведут себя подобно асинхронным. Во многих случаях это свойство является недостатком, так как может оказаться причиной сбоев в цифровых устройствах.

От этого свободны триггеры с динамическим и двух ступенчатым управлением.

Функциональные свойства всей триггерной системы определяются первой ступенью, вторая ступень обычно представляет собой синхронный RS-триггер со статическим управлением.

D - триггер имеет 1 информационный вход (D-вход). Бывают только синхронные D-триггеры. Состояние информационного входа передаётся на выход под действием синхроимпульса (вход С).

Рис.13.22 - Схема D-триггера на основе синхронного RS-триггера

Таблица 13.2 - Таблица переходов D-триггера

| C | D | Q(t) | Q(t+1) | Пояснения |

| 0 | * | 0 | 0 | Режим хранения информации |

| 0 | * | 1 | 1 | |

| 1 | 0 | * | 0 | Режим записи информации |

| 1 | 1 | * | 1 |

Если на входе D - "1", то по приходу синхроимпульса Q = 1.

Если на D "0", то Q =0.

Триггер Т -типа, или счетный триггер, имеет один информационный Т-вход. Смена его состояний происходит всякий раз, когда входной сигнал меняет свое значение в определенном направлении. В зависимости от того, какой перепад напряжения используется для управления (от нуля к единице или от единицы к нулю), различают Т-триггеры с прямым или инверсным динамическим управлением (  -триггер).

-триггер).

По способу ввода входной информации Т-триггеры могут быть асинхронными и синхронными.

Таблица 13.3 - Таблица переходов Т триггера

| T | Q(t) | Q(t+1) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Счетные триггеры как самостоятельные микроэлектронные изделия не выпускаются промышленно, так как их легко получить из других типов триггеров, например из D-триггеров.

Особенностью Т-триггера является в два раза меньшая часто-та выходных сигналов по срав-нению с частотой сигналов на входе. Это позволяет использовать его в качестве делителя частоты последовательности импульсов на два, а также при создании двоичных счетчиков.

Рис. 13.23.Схема T-триггера на основе двухступенчатого D-триггера

Счетные триггеры со статическим управлением во время действия входного импульса проявляют склонность к генерации, и практической реализации не нашли.

JK-триггер

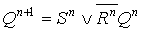

Функциональная особенность JK-триггеров состоит в том, что при всех входных комбинациях, кроме одной  , они действуют подобно RS-триггеру, причем вход J играет роль входа S, а K-вход соответствует R-входу. При входной комбинации

, они действуют подобно RS-триггеру, причем вход J играет роль входа S, а K-вход соответствует R-входу. При входной комбинации  в каждом такте выходной сигнал меняет свое значение на противоположное. JK-триггеры не имеют неопределенных состояний. Таблица переходов состояний триггера имеет вид (табл. 11).

в каждом такте выходной сигнал меняет свое значение на противоположное. JK-триггеры не имеют неопределенных состояний. Таблица переходов состояний триггера имеет вид (табл. 11).

В схемном отношении JK-триггер отличается от триггеров RS-типа наличием обратных связей. Логическая структура простейшего JK-триггера показана на рис. 13.24.

Элементы временной задержки в данной схеме играют роль стабилизаторов состояний триггера, и непосредственно на его функциональные свойства не влияют.

Рис. 13.24

В интегральной схемотехнике применяются только синхронные JK-триггеры в силу жестких требований к длительности входных сигналов для асинхронного варианта.

JK-триггеры относятся к универсальным устройствам. Их универсальность имеет двойственный характер. Во-первых, эти триггеры с равным успехом могут быть использованы в счетчиках, регистрах, делителях частоты и других электронных узлах, во-вторых, путем определенного соединения выводов они легко обращаются в триггеры других типов.

Для получения T-триггера достаточно объединить вход J и K и подавать на них входные импульсы. Это будет вариант синхронного T-триггера. В асинхронном варианте T-триггера на входы J и K подают сигнал логической единицы, а входные импульсы поступают на вход синхронизации (рис.13.25).

а б в

Рис.13.25. Использование JK-триггера в качестве: а – D-триггера; б – асинхронного T-триггера; в – синхронного T-триггера

Рассмотренные JK-триггеры являются одноступенчатыми.

Однако более устойчивыми в работе являются двухступенчатые триггеры, поскольку обе ступени тактируются поочередно, что предупреждает паразитную генерацию в схеме.

|

из

5.00

|

Обсуждение в статье: Логические элементы на МДП-транзисторах |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы