|

Главная |

Программируемое устройство прямого доступа к памяти (КР580ВТ57).

|

из

5.00

|

Устройство представляет собой четырехканальный программируемый контроллер, используемый в микропроцессорных системах, построенных на основе МП БИС КР580ИК80.

Устройство позволяет осуществлять двунаправленный обмен массивами данных емкостью до 16К байт между ЗУ и любым из четырех ВУ без участия МП БИС.

При одновременном поступлении запросов от ВУ программируемая логика схемы позволяет выбирать наивысший по приоритету канал прямого доступа к памяти (КПДП).

Начало режима обмена по КПДП инициируется с помощью подачи сигнала З.ЗХ на вход МП БИС. После получения подтверждения

режима захвата с выхода П.ЗХ МП БИС устройство берет на себя

функцию управления МА и МУ микроЭВМ.

Направления обмена данными, а также режим работы устройства задаются с помощью программы ее начальной установки.

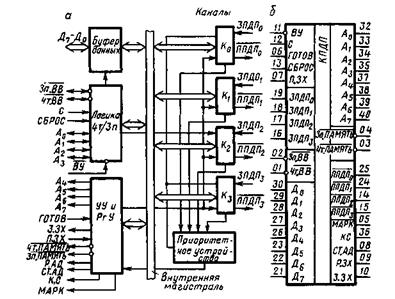

Упрощенная структура микросхемы КР580ВТ57 приведена на рис.

2.3.6, а, а ее условное обозначение — на рис. 2.3.6, б.

Схема содержит четыре одинаковых канала, обеспечивающих ПДП (К0 — К3). Каждый канал включает в себя по два 16-разрядных регистра адреса ПДП и конца счета.

В процессе выполнения программы начальной установки в регистр адреса должен быть записан начальный адрес памяти, к которому будет обращаться ВУ по КПДП.

В младшие 14 разрядов регистра конца счета записывается число, на единицу меньшее длины передаваемого массива.

Старшие два разряда регистра конца счета используются для задания режима работы канала. После передачи очередного данного по КПДП содержание регистра адреса автоматически увеличивается, а содержание регистра конца счета

уменьшается на единицу. Таким образом, если N — длина передаваемого массива, то при передаче N — 1 данных по КПДП в регистре конца счета будет записан «0». Старшие два разряда этого регистра в процессе обмена данными не меняются .

Рисунок 2.3.6 - Упрощенная структура микросхемы КР580ВТ57 (а), ее условное обозначение (б)

Содержание этих разрядов изменяется с помощью программы начальной установки, записываемой в схему между циклами обмена данными по КПДП.

Каждый канал ПДП имеет свой вход запроса (ЗПДП0 —

ЗПДП3). Внешнее устройство информирует о готовности к обмену данными подачей единичного сигнала на этот вход.

ППДП0 — ППДП3 — выходы, задействованные для информирования ВУ о его выборе для обмена данными по КПДП.

Д7 — Д0 — двунаправленная МД, по которой происходит обмен

информацией между МП БИС и схемой при записи программы начальной установки, выводе содержания внутренних программнодоступных регистров. По ней также выводятся старшие восемь разрядов адреса при работе КПДП.

Отметим, что в обмене данными между ВУ и ЗУ двунаправленная МД не участвует.

А3— А0 — младшие разряды двунаправленной МА При записи в схему программы начальной установки, а также чтения содержания регистров используются как входы для выбора регистра, с которым будет происходить обмен информацией. При работе в цикле ПДП по ним выводятся младшие четыре разряда кода адреса.

А7 — А4 — однонаправленные МА с тремя состояниями, по которым выводятся соответственно разряды А7 — А4 кода адреса.

Зп.ВВ (запись ввод-вывод) — двунаправленный управляющий

вход-выход, используемый как вход для получения сигнала на запись

данных во внутренние регистры схемы при ее начальной установке.

При работе в цикле ПДП на его выходе формируется сигнал, разрешающий запись данных из памяти во ВУ.

Чт.ВВ (чтение ввод-вывод) — двунаправленный управляющий

вход-выход, работает как вход для получения сигнала Чт.ВВ от МУ

микроЭВМ при чтении содержания внутренних регистров схемы.

При работе в цикле ПДП служит для выдачи сигнала, разрешающего считывание данных из ВУ в память.

Таким образом, выводы Чт ВВ, Зп.ВВ схемы подключаются к ВУ

и определяют для них направление и интервалы времени, отведенные

для записи или считывания данных. Сигналы, определяющие эти же

интервалы времени для памяти, формируются на выходных зажимах Чт.ПАМЯТЬ и Зп.ПАМЯТЬ.

Чт.ПАМЯТЬ (чтение память) — выход для чтения данных из памяти

Зп.ПАМЯТЬ (запись память) — выход для записи данных в память.

МАРК (маркер 128-го цикла) — выход, на котором появляется

единичный сигнал, указывающий, что текущий цикл ПДП является

по счету 128-м циклом при передаче массива данных.

ГОТОВ (готовность) — управляющий вход, используемый при

работе с медленными устройствами, у которых время записи информации больше, чем длительность такта работы микроЭВМ. Подача нулевого уровня сигнала на этот вход переводит схему в состояние ожидания. Это состояние аналогично состоянию ожидания для МП БИС.

ЗПДП0 — ЗПДП3 (запрос ПДП) — входы, на которые ВУ подают сигналы запросов на получение цикла ПДП.

ППДП0 — ППДП3 (подтверждение ПДП) — выход схемы, используемый для информирования ВУ о его выборе для обмена информацией в цикле ПДП.

КС (конец счета) — выход, единичный импульс, на котором указывает ВУ, что текущий цикл обмена по КПДП является последним при передаче массива данных. Единичный импульс на выходе КС будет формироваться на интервале времени, когда в 14 младших разрядах регистра конца счета будет записан «0». При наличии «1» в разряде Д6 регистра управления по окончании последнего цикла

обмена по КПДП этот канал будет автоматически отключен.

Р.АД (разрешение адреса) — выход, сигнал на котором отключает все магистрали микроЭВМ от МП БИС, также используется для записи старших восьми разрядов кода адреса в буферный регистр адреса и отключения схем выборки ВУ. При работе в режиме ПДП выборка ВУ для обмена данными осуществляется с помощью выходных сигналов на ППДП0 — ППДП3.

СТ.АД (строб адреса) — выход, на котором формируется сигнал,

записывающий старшие восемь разрядов кода адреса в буферном

регистре.

ВУ (выбор устройства) — вход выбора данной схемы. Нулевой

сигнал ВУ должен формироваться дешифратором адреса по сигналам с разрядов А4 — А15 МА микроЭВМ. Вход автоматически отключается при работе схемы в цикле ПДП.

СБРОС — вход начальной установки схемы. Подача единичного

сигнала обнуляет содержание всех программно-доступных регистров

схемы, что в свою очередь отключает все каналы К0—К3.

С (синхронизация) — вход синхросигнала Ф2.

З.ЗХ (запрос захвата) — сигнал с этого выхода схемы подается

на вход З.ЗХ МП БИС.

П.ЗХ (подтверждение захвата) — вход, на который подается

выходной сигнал П.ЗХ от МП БИС. Этот сигнал подтверждает, что

все магистрали переведены в состояние высокого сопротивления.

При работе с МП БИС блок логики Чт/Зп дешифрирует младшие

разряды А3 — А0 кода адреса и в зависимости от сигналов Зп.ВВ,

Чт.ВВ организует запись или чтение программно-доступных регистров схемы. При работе в цикле ПДП логические цепи формируют пары сигналов Чт.ВВ, Зп ПАМЯТЬ или Зт.ВВ, Чт ПАМЯТЬ на выходах схемы, обеспечивающие временное тактирование процесса обмена данными между ВУ и памятью

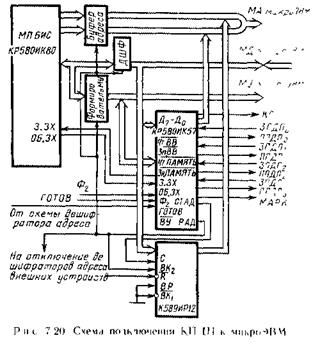

Ввиду того, что старшие восемь разрядов адреса (A0 - A7) должны быть записаны в буферном регистре, схема КР580ВТ57 подключается к микроЭВМ совместно с каким-либо буферным регистром.

В качестве такого регистра может быть использован МБР К589ИР12,

его схема подключения приведена на рис 2.3.7.

Рисунок 2.3.7 – Схема подключения

Организация временных интервалов в микроЭВМ.

Для организации временных интервалов при работе микроЭВМ может быть использован любой счетчик сигнала, работающий на сложение или

вычитание. В качестве входных импульсов на счетчик подают либо

синхросигнал тактового генератора МП БИС, либо сигнал от отдельного задающего генератора.

Для организации временных интервалов

в микропроцессорных системах, построенных на MПK серии К580,

применяется специальная микросхема интервального таймера

КР580ВИ53.

|

из

5.00

|

Обсуждение в статье: Программируемое устройство прямого доступа к памяти (КР580ВТ57). |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы