|

Главная |

Система проектирования

|

из

5.00

|

MAX + Plus II

Название системы MAX+PLUS II является аббревиатурой от Multiple Array MatriX Programmable Logic User System. Что переводится как, пользовательская система программирования логики упорядоченных структур. Система MAX+PLUS II имеет средства удобного ввода проекта, компиляции и отладки, а также непосредственного программирования устройств.

Процедуру разработки нового проекта от концепции до завершения можно упрощённо представить следующим образом:

1. Задание имени файла – проекта верхнего уровня (Top of hierarchy) в качестве имени проекта (Project name);

2. Создание нового файла (design file) проекта или иерархической структуры нескольких файлов проекта с помощью любого сочетания редакторов в системе MAX+PLUS II, то есть графического, текстового и сигнального редакторов;

3. Назначение семейства ПЛИС для проекта. Это может быть произведено вручную или автоматически;

4. Открытие окна компилятора Compiler и выбор кнопки Start для начала компиляции проекта. По желанию пользователя можно подключить модуль извлечения временных параметров проекта Timing SNF Extractor для создания файла, используемого при временном моделировании;

5. В случае успешной компиляции возможен временной анализ, для чего следует выполнить следующее:

─ для проведения временного анализа задержек открыть окно Timing Analyzer, выбрать режим анализа и нажать кнопку Start;

для проведения симуляции нужно сначала создать тестовый вектор в файле канала тестирования (.scf), пользуясь сигнальным редактором, или в файле вектора (.vec), пользуясь текстовым редактором. Затем открыть окно отладчика Simulator и нажать кнопку Start;

6. Открытие окна программатора Programmer с последующим выбором одного из двух способов: использование программатора MPU (Master Programming Unit)

или подключение загрузочных устройств BitBlaster, Byte-Blaster или FLEX Download Cable к устройству, программируемому в системе;

7. Выбор кнопки Program для программирования устройств с памятью типа EPROM или EEPROM либо выбор кнопки Configure для конфигурации устройства с памятью типа SRAM (FLEX).

При запуске системы MAX+PLUS II автоматически открывается её Главное окно, меню которого охватывают все приложения системы MAX+PLUS II.

|

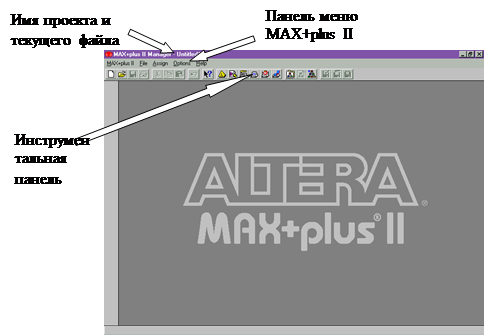

На рисунке 2.1 представлено Главное окно пакета MAX+PLUS II:

Рисунок 2.1 – Главное окно системы MAX+PLUS II

В верхней части окна отображается имя проекта и текущего файла проекта. Затем следует строка меню, под ней панель основных инструментов системы, обеспечивающая быстрый вызов её компонентов. В нижней части окна располагается строка подсказки.

ПО системы MAX+PLUS II содержит 11 приложений и главную управляющую программу. Различные приложения, обеспечивающие создание проекта, могут быть активизированы мгновенно, что позволяет пользователю переключаться между ними щелчком мыши или с помощью команд меню. В это же время может работать одно из фоновых приложений, например, компилятор, симулятор, анализатор синхронизации и программатор. Одни и те же команды разных приложений работают одинаково, что облегчает задачу разработки логического дизайна проекта.

Окно любого приложения можно свернуть до пиктограммы, не закрывая приложения, а затем снова развернуть его. Это позволяет работать эффективно, не загромождая рабочий экран.

|

Вызов компонентов системы удобно производить через окно меню MAX+PLUS II, представленное на рисунке 2.2

Рисунок 2.2 – Окно меню MAX+PLUS II

В таблице 2.1 приведено описание приложений.

Таблица 2.1 – Описание приложений САПР MAX+PLUS II

| Приложение | Выполняемая функция |

| 1 | 2 |

Hierarchy Display Hierarchy Display

| Обзор иерархии – отображает текущую иерархическую структуру файлов в виде дерева с ветвями, представляющими собой подпроекты |

Graphic Editor Graphic Editor

| Графический редактор – позволяет разрабатывать схемный логический проект в формате реального отображения на экране WYSIWYG |

продолжение таблицы 2.1

| 1 | 2 |

Symbol Editor Symbol Editor

| Символьный редактор – позволяет редактировать существующие символы и создавать новые |

Text Editor Text Editor

| Текстовый редактор – позволяет создавать и редактировать текстовые файлы логического дизайна, написанные на языках AHDL, VHDL, Verilog HDL |

Waveform Editor Waveform Editor

| Сигнальный редактор – выполняет двойную функцию: инструмент для рахработки дизайна и инструмент для ввода тестовых векторов и наблюдения результатов тестирования |

Floorplan Editor Floorplan Editor

| Поуровневый планировщик – позволяет графическими средствами делать назначения контактам устройства и ресурсов логических элементов |

Compiler Compiler

| Компилятор – обрабатывает графические проекты |

Simulator Simulator

| Симулятор – позволяет тестировать логические операции и внутреннюю синхронизацию проектируемой логической цепи |

Timing Analyzer Timing Analyzer

| Временной анализатор – анализирует работу проектируемой логической цепи после того, как она была синтезирована и оптимизирована компилятором |

Programmer Programmer

| Программатор – позволяет программировать, конфигурировать, проводить верификацию и тестировать ПЛИС фирмы ALTERA |

продолжение таблицы 2.1

Message Processor Message Processor

| Генератор сообщений – выдает на экран сообщения об ошибках, предупреждающие и информационные сообщения |

Перед тем как начать работать в системе MAX+PLUS II, следует понять разницу между файлами проекта, вспомогательными файлами и проектами.

Файл проекта — это графический, текстовый или сигнальный файл, созданный с помощью графического или сигнального редакторов системы MAX+PLUS II или в любом другом, использующем промышленные стандарты, схемном или текстовом редакторе либо при помощи программы netlist writer, имеющейся в пакетах, поддерживающих EDIF, VHDL и Verilog HDL. Этот файл содержит логику для проекта MAX+PLUS II и обрабатывается компилятором. Компилятор может автоматически обрабатывать следующие файлы проекта:

─ графические файлы проекта (.gdf);

─ текстовые файлы проекта на языке AHDL (.tdf);

─ сигнальные файлы проекта (.wdf);

─ файлы проекта на языке VHDL (.vhd);

─ файлы проекта на языке Verilog (.v);

─ схемные файлы OrCAD (.sch);

─ входные файлы EDIF (edf);

─ файлы формата Xilinx Netlist (.xnf);

─ файлы проекта Altera (.adf);

─ файлы цифрового автомата (.smf).

Вспомогательные файлы – это файлы, связанные с проектом MAX+PLUS II, но не являющиеся частью его иерархического дерева. Большинство таких файлов не содержит логики проекта. Некоторые из них создаются автоматически приложением системы MAX+PLUS II, другие – пользователем. Примерами вспомогательных файлов являются файлы назначений и конфигурации (.acf), символьные файлы (.sym), файлы отчета (.rpt) и файлы тестовых векторов (.vec).

Проект состоит из всех файлов иерархической структуры проекта, в том числе вспомогательных и выходных файлов. Именем проекта является имя файла проекта верхнего уровня без расширения. Система MAX+PLUS II выполняет компиляцию,

тестирование, анализ синхронизации и программирование сразу целого проекта, хотя пользователь может в это время редактировать файлы этого проекта в рамках другого

|

проекта.

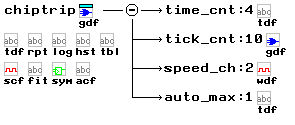

Рисунок 2.3 – Иерархия проекта в MAX+Plus II

В иерархической структуре проекта на любом уровне допускается смешанное использование файлов с расширениями “.gdf .tdf .vhd .v .edf .sch”. Однако файлы с расширением “.wdf .xnf .adf .smf ” должны быть либо на самом нижнем иерархическом уровне проекта, либо быть единственными.

Для каждого проекта желательно создавать отдельный подкаталог в рабочем каталоге системы MAX+PLUS II.

В системе MAX+PLUS II легко доступны все инструменты для создания проекта. Разработка проекта ускоряется за счёт имеющихся стандартных функций, в том числе примитивов, мегафункций, библиотеки параметризованных модулей (LPM) и макрофункций устаревшего типа микросхем 74 серии.

В системе MAX+PLUS II есть три редактора для разработки проекта: графический, текстовый и сигнальный, а также два вспомогательных редактора: поуровневый планировщик и символьный редактор. Схемные файлы проекта создаются в графическом редакторе MAX+PLUS II. Можно также открыть, редактировать и сохранять схемы, созданные схемным редактором OrCAD.

Проекты на языках AHDL, VHDL и Verilog HDL создаются в текстовом редакторе MAX+PLUS II или любом другом текстовом редакторе.

Сигнальные проекты создаются в сигнальном редакторе MAX+PLUS II.

Файлы формата EDIF и Xilinx, разработанные другими стандартными инструментами системы EDA, могут быть импортированы в среду MAX+PLUS II.

Схемные и тестовые файлы, созданные в системе MAX+PLUS II (под ДОС) и программных пакетах фирмы Altera A+PLUS и SAM+PLUS могут быть интегрированы в среде MAX+PLUS II.

Назначения физических ресурсов для любого узла или контакта в текущем проекте могут быть введены в графическую среду с помощью поуровневого планировщика.

|

Во всех приложениях MAX+PLUS II есть возможность с помощью команд из меню Assign (Назначить) вводить, редактировать и удалять типы назначений ресурсов, устройств и параметров, которые управляют компиляцией проекта. На рисунке 2.4 представлены команды меню Assign.

Рисунок 2.4 – Меню назначений проекта Assign

Пользователь может делать назначения для текущего проекта независимо от того, открыт ли какой-нибудь файл проекта или окно приложений. Система MAX+PLUS II сохраняет информацию для проекта в файле с расширением .acf. Изменения назначений, сделанные в окне поуровневого планировщика, также сохраняются в файле ACF.

Следующие функции являются общими для всех приложений MAX+PLUS II: назначение устройств, ресурсов и зондов; сохранение предыдущей версии; глобальные опции устройства в проекте; глобальные параметры проекта; глобальные требования к временным параметрам проекта; глобальный логический синтез проекта.

Ресурс является частью устройства, как, например контакт или логический элемент, который выполняет конкретное, определённое пользователем задание. Управление

компиляцией проекта и его временными параметрами осуществляется с помощью различных назначений (Assign).Доступны следующие типы назначений:

Clique assignment (Назначение клики) задаёт, какие логические функции должны оставаться вместе в одном и том же блоке логической структуры LAB, блоке ячеек памяти EAB, в одном ряду или устройстве.

Chip assignment (Назначение кристалла) задаёт, какие логические функции должны быть реализованы в одном и том же устройстве в случае разделения проекта на несколько устройств.

Pin assignment (Назначение контакта) назначает вход или выход одной логической функции конкретному контакту или нескольким контактам чипа.

Location assignment (Назначение ячейки) назначает единственную логическую функцию конкретной ячейке чипа.

Probe assignment (Назначение зонда) присваивает уникальное имя входу или выходу логической функции.

Connected pin assignment (Назначение соединенных контактов) задаёт внешнее соединение двух или более контактов на схеме пользователя.

Local routing assignment (Назначение местной разводки) присваивает коэффициент разветвления по выходу узла логическому элементу, находящемуся в том же блоке LAB, что и узел, или в соседнем LAB, прилежащем к узлу, с использованием общих местных разводок.

Device assignment (Назначение устройства) назначает тип ПЛИС, на которой реализуется проект.

Logic option assignment (Назначение логической опции) управляет логическим синтезом отдельных логических функций во время компиляции с применением стиля логического синтеза.

Timing assignment (Назначение временных параметров) управляет логическим синтезом и подгонкой отдельных логических функций для получения требуемых характеристик для времени задержки tPD (вход – неподрегистренный выход), tCO (синхросигнал – выход), tSU (синхросигнал – время установки), fMAX (частота синхросигнала).

Можно определить глобальные опции устройства для компилятора, чтобы он использовал их для всех устройств при обработке проекта. Для резервирования дополнительных возможностей на будущее можно задать процентное соотношение контактов и логических элементов, которые должны оставаться неиспользованными во время текущей компиляции.

С использованием команды Global Project Parameters можно задать имена и глобальные установки, которые будут использованы компилятором для параметров всех параметризованных функций в проекте.

При помощи команды Global Project Timing Requirements можно ввести глобальные требования по синхронизации для проекта, задавая общие характеристики для времени задержки tPD (вход – нерегистрируемый выход), tCO (синхросигнал – выход), tSU (синхросигнал – время установки), fMAX (частота синхросигнала).

Команда Global Project Logic Synthesis позволяет сделать глобальные установки для компилятора в части логического синтеза проекта.

Все пять редакторов MAX PLUS II и три редактора создания дизайна (графический, текстовый и сигнальный) имеют общие функции, такие как, например, создание, сохранение и открытие файла. Кроме того, приложения редактора MAX PLUS II имеют следующие общие функции:

─ создание файлов символов и файлов с прототипами функций (Include-файлы), (symbol and include file generator);

─ поиск узлов (node location);

─ траверз иерархического дерева (hierarchy traversal);

─ всплывающие окна меню, зависящего от контекста (contextsensitive menu commands);

─ временной анализ (Timing Analysis);

─ поиск и замена фрагментов текста (Find and Replace Text);

─ отмена последнего шага редактирования, его возвращения, вырезка, копирование, вставка и удаление выбранных фрагментов, обмен фрагментами между приложениями MAX PLUS II или приложениями Windows (Undo, Cut, Copy, Paste & Delete);

─ печать (print).

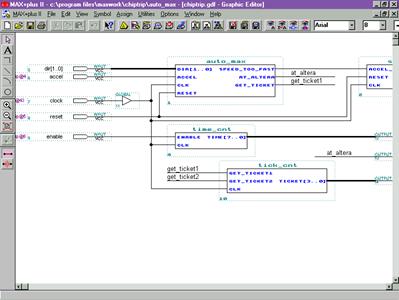

Графический редактор (Graphic Editor) обеспечивает проектирование в реальном формате изображения (WYSIWIG). Графические файлы проекта (.gdf) или схемные файлы OrCAD (.sch), созданные в данном графическом редакторе, могут включать любую комбинацию символов примитивов, мегафункций и макрофункций. Символы могут представлять собой любой тип файла проекта (.gdf .sch .tdf .vhd .v .wdf .edf .xnf .adf .smf).

|

Рисунок 2.5 – Окно графического редактора

Инструмент выбора (“стрелка”) облегчает разработку дизайна. Он позволяет двигать и копировать объекты, а также вводить новые символы. Если переместить его на контакт или конец линии, он автоматически преобразуется в инструмент рисования ортогональных линий. Если им щелкнуть на тексте, он автоматически преобразуется в инструмент редактирования текста.

Символы соединяются сигнальными линиями или линиями шин (bus), которые представляют собой несколько логически сгруппированных узлов. Узлом называется именованный вход или выход логического примитива, макро- или мегафункции. Если присвоить узлу имя, то его можно соединить с другими узлами или символами только по имени. Шины соединяются по имени, но возможно и их графическое соединение.

Пользователь может переопределить порты, используемые в каждом отдельном примере символа мега- или макрофункции, а также инвертировать их. При этом, для указания инвертированного порта появляется кружок, обозначающий инверсию.

Можно выбрать несколько объектов. В прямоугольной области и редактировать их вместе или по отдельности. При перемещении выбранной области сигнальные связи сохраняются.

Для каждого символа можно просматривать назначения зондов, выводов, расположения, чипов, клик, временных параметров, местную трассировку, логические опции и назначения параметров. Для облегчения тестирования можно также создать назначения

групп выводов, которые будут определять соединения внешнего устройства между выводами.

Поставляемые фирмой Altera примитивы, мега- и макрофункции сокращают время разработки дизайна. Пользователь может также создавать свои собственные библиотеки функций. При редактировании символа или восстановлении его по умолчанию можно автоматически создавать выбранные примеры или все примеры этого символа в файле в графическом редакторе.

Графический редактор обеспечивает ряд других возможностей. Например, можно увеличивать или уменьшать масштаб отображения на экране и увидеть дизайн целиком или какую-либо его деталь. Можно выбирать гарнитуру и размер шрифта, задавать стили линий, устанавливать и отображать направляющие. Можно копировать, вырезать, вставлять и удалять выбранные фрагменты; получать зеркальное отображение (вертикальное или горизонтальное); поворачивать выделенные фрагменты на 90, 180 или 270 градусов; задавать размер и ориентацию текущего листа схемы по вертикали и горизонтали.

|

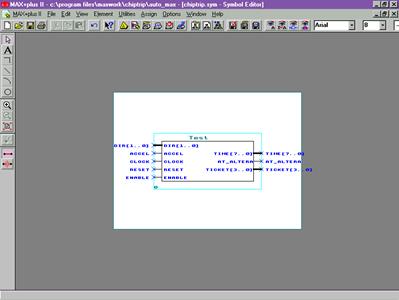

Символьный редактор (Symbol Editor) позволяет просматривать, создавать и редактировать символ. Символьный файл имеет то же имя, что и проект, и расширение “.sym”. Команда Create Default Symbol меню File, которая есть в графическом, текстовом и сигнальном редакторах, создает символ для любого файла проекта.

Рисунок 2.6 – Окно символьного редактора

Символьный редактор обладает следующими характеристиками:

─ можно переопределить символ, представляющий файл проекта;

─ создавать и редактировать выводы и их имена, используя входные, выходные и двунаправленные выводы, а также задавать варианты ввода символа в файл графического редактора: с отображением на экране имён выводов или без отображения, с отображением полного или сокращённого имени. Таким образом, полное имя порта и имя, отображаемое в файле в окне графического редактора, могут быть разными;

─ имена выводов автоматически дублируются за границу символа. Редактированию подлежат только имена внутри границы символа. Имена снаружи нельзя менять, они просто иллюстрируют соединение выводов;

─ задать значения параметров и их значения по умолчанию;

─ сетка и направляющие помогают выполнить точное выравнивание объектов;

─ в символе можно вводить комментарии, которые также появятся при вводе символа в файл в графическом редакторе.

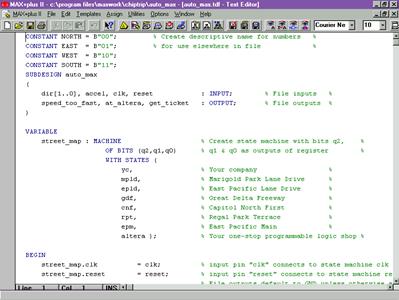

Текстовый редактор (Text Editor) является инструментом для создания текстовых файлов проекта на языках описания аппаратуры: AHDL (.tdf), VHDL (.vhd), Verilog HDL (.v). В этом текстовом редакторе можно работать также с произвольным файлом формата ASCII. Все перечисленные файлы проекта можно создавать в любом текстовом редакторе, однако данный редактор имеет встроенные возможности ввода файлов проекта, их компиляции и отладки с выдачей сообщений об ошибках и их локализацией в исходном тексте или в тексте вспомогательных файлов; кроме того, существуют шаблоны языковых конструкций для AHDL, VHDL и Verilog HDL, выполнено окрашивание синтаксических конструкций. В данном редакторе можно вручную редактировать файлы назначений и конфигурации (.acf), а также делать установки конфигурации для компилятора, симулятора и временного анализатора.

Пользуясь данным текстовым редактором, можно создавать тестовые векторы (.vec), используемые для тестирования, отладки функций и при вводе сигнального проекта. Можно также создавать командные файлы (.cmd — для симулятора и .edc — для EDIF), а также макробиблиотеки (.lmf).

|

Рисунок 2.7 – Окно текстового редактора

В текстовом редакторе MAX PLUS II обеспечивается контекстная справка.

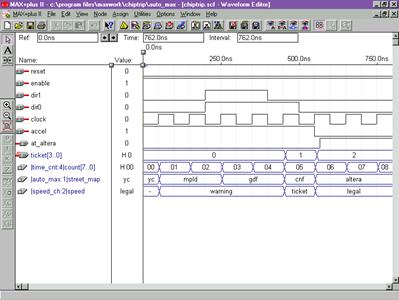

Сигнальный редактор (Waveform Editor) служит инструментом создания описания проекта, ввода тестовых векторов и просмотра результатов тестирования. Пользователь может создавать сигнальные файлы проекта (.wdf), которые содержат временные диаграммы, описывающие логику работы проекта, а также файлы каналов тестирования (.scf), которые содержат входные вектора для тестирования и функциональной отладки. Разработка описания проекта в сигнальном редакторе является альтернативой его созданию в графическом или текстовом редакторах. Здесь можно графическим способом задавать комбинации входных логических уровней и требуемых выходов. Созданный таким образом файл WDF может содержать как логические входы, так и входы цифрового автомата, а также выходы комбинаторной логики, счётчиков и цифровых автоматов. Способ разработки дизайна в сигнальном редакторе лучше подходит для цепей с чётко определёнными последовательными входами и выходами, то есть для цифровых автоматов, счётчиков и регистров.

С помощью сигнального редактора можно легко преобразовывать временные диаграммы сигналов целиком или частично, создавая и редактируя узлы и группы. Простыми командами можно создавать файл таблицы ASCII-символов (.tbl) или импортировать файл тестовых векторов в формате ASCII (.vec) для создания файлов тестируемых каналов SCF и сигнального дизайна WDF. Можно также сохранить файл WDF как SCF для проведения

тестирования или преобразовать SCF в WDF для использования его в качестве файла проекта.

|

Рисунок 2.8 – Окно сигнального редактора

Сигнальный редактор имеет следующие отличительные черты:

─ можно создать или отредактировать узел для получения типа I/O (вход/выход), который представляет собой входной или выходной контакт или “замурованную” логику;

─ при разработке WDF можно задать тип логики, которая делает каждый узел контактом, причём входным, регистровым, комбинаторным или цифровым автоматом;

─ задать значения по умолчанию в логическом узле для активного логического уровня: высокий (1), неопределённый (X) или с высоким импедансом (Z), а также имя состояния по умолчанию в узле типа цифрового автомата;

─ для упрощения создания тестового вектора можно легко добавить в файл тестируемых каналов SCF несколько узлов или все из информационного файла симулятора (.snf), существующего для полностью откомпилированного и оптимизированного проекта;

─ можно объединять от 2 до 256 узлов для создания новой группы (шины) или разгруппировывать объединённые ранее в группу узлы. Можно также объединять группы с другими группами. Значение группы может быть отображено в двоичной, десятичной, шестнадцатеричной или восьмеричной системе счисления с преобразованием (или без) в код Грэя;

─ можно копировать, вставлять, перемещать или удалять выбранную часть (“интервал”) сигнала, а также весь узел или группу (то есть имя узла или группы плюс форму сигнала). Одной операцией можно отредактировать несколько интервалов, целые формы сигналов, а также целые узлы и группы. Копии целых узлов и групп связаны, так что редакционные правки одной копии отражаются во всех копиях. Можно также инвертировать, вставлять, переписывать, повторять, расширять или сжимать интервал формы сигнала любой длины с любым логическим уровнем, тактовым сигналом, последовательностью счёта или именем состояния;

─ задать и, по желанию, отображать на экране сетку для выравнивания переходов между логическими уровнями либо до их создания, либо после;

─ в любом месте файла можно вводить комментарии между формами сигнала;

─ менять масштаб отображения;

─ для облегчения тестирования можно сделать наложение любых выходов в текущем файле или наложить второй файл сигнального редактора для сравнения сигналов его узлов и групп с соответствующими сигналами текущего файла.

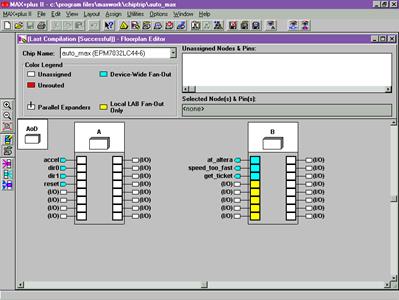

Поуровневый планировщик (Floorplan Editor) предназначен для назначения ресурсов физических устройств и просмотра результатов разводки, сделанных компилятором. В окне поуровневого планировщика могут быть представлены два типа изображения:

─ Device View (Вид устройства) показывает все контакты устройства и их функции;

─ LAB View (Вид логического структурного блока) показывает внутреннюю часть устройства, в том числе все логические структурные блоки (LAB) и отдельные логические элементы.

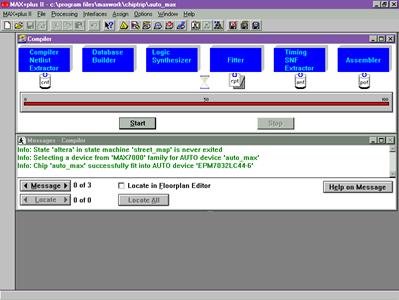

После выполнения всех назначений и задания проекта приступают к его компиляции. Сначала компилятор извлекает информацию об иерархических связях между файлами проекта и проверяет проект на простые ошибки ввода описания проекта. Он создаёт организационную карту проекта и затем, комбинируя все файлы проекта, превращает их в базу данных без иерархии, которую может эффективно обрабатывать.

|

Рисунок 2.9 – Окно поуровневого планировщика (LAB View)

Компилятор применяет разнообразные способы увеличения эффективности проекта и минимизации использования ресурсов устройства. Если проект слишком большой, чтобы быть реализованным в одном устройстве, компилятор может автоматически разбить его на части для реализации в нескольких устройствах того же самого семейства ПЛИС, при этом число соединений между устройствами минимизируется. В файле отчёта (.rpt) затем будет отражено, как проект будет реализован в одном или нескольких устройствах.

Кроме того, компилятор создает файлы программирования или загрузки, используемые программатором системы MAX+PLUS II или другим, для программирования одного или нескольких устройств.

Несмотря на то, что компилятор может автоматически компилировать проект, существует возможность задать обработку проекта в соответствии с точными указаниями разработчика. Например, можно задать стиль логического синтеза проекта по умолчанию и другие параметры логического синтеза в рамках всего проекта, что позволит провести логический синтез в соответствии с частными потребностями. Кроме того, можно ввести требования по синхронизации в рамках всего проекта, точно задать разбиение большого проекта на части для реализации в нескольких устройствах и выбрать варианты параметров устройств, которые будут применены для всего проекта в целом. Можно также выбрать, сколько выводов и логических элементов должно быть оставлено

неиспользованными во время текущей компиляции, чтобы зарезервировать их для последующих модификаций проекта.

|

Рисунок 2.10 – Окно компилятора с редактором сообщений

Компилятор автоматически обрабатывает все входные файлы текущего проекта. Процесс компиляции можно наблюдать в окне компилятора в следующем виде:

─ опустошаются и переворачиваются песочные часы, что указывает на активность компилятора;

─ высвечиваются прямоугольники модулей компилятора по очереди, по мере того как компилятор завершает каждый этап обработки;

─ под прямоугольником модуля компилятора появляется пиктограмма выходного файла, сгенерированного данным модулем. Для открытия соответствующего файла следует дважды щёлкнуть левой кнопкой мыши по пиктограмме;

─ процент завершения компиляции постепенно увеличивается (до 100%), что отражается также растущим прямоугольником “градусник”;

─ во время разбиения и монтажа кнопка компилятора Stop превращается в кнопку Stop/Show Status (Стоп/Показать состояние), которую можно выбрать для открытия диалогового окна, в котором отражается текущее состояние разбиения и монтажа проекта;

─ при обнаружении в процессе компиляции каких-либо ошибок или возможных проблем автоматически открывается окно обработчика сообщений (Message

Processor), в котором отображается список сообщений об ошибке, предупреждающих и информационных сообщений, а также сразу даётся справка по исправлению ошибки. Кроме того, возможно определить источники сообщений в файлах проекта или в его поуровневом плане назначений.

─ Компилятор системы MAX+PLUS II обрабатывает проект, используя следующие модули и утилиты:

─ экстрактор списка цепей (Compiler Netlist Extractor), включающий встроенные программы чтения форматов EDIF, VHDL, Verilog и XNF;

─ построитель базы данных (Database Builder);

─ логический синтезатор (Logic Synthesizer);

─ разделитель (Partitioner);

─ трассировщик (Fitter);

─ экстрактор для функционального тестирования (Functional SNF Extractor);

─ экстрактор для тестирования временных параметров (Timing SNF Extractor);

─ экстрактор для тестирования компоновки (Linked SNF Extractor);

─ программа записи выходного файла в формат EDIF (EDIF Netlist Writer);

─ программа записи выходного файла в формат Verilog (Verilog Netlist Writer);

─ программа записи выходного файла в формат VHDL (VHDL Netlist Writer);

─ модуль ассемблера (Assembler);

─ утилита диагностики проекта (Design Doctor Utility).

Модуль экстрактора форматов (Compiler Netlist Extractor) преобразует каждый файл проекта в один или несколько двоичных файлов с расширением .cnf (compiler netlist file). Поскольку компилятор подставляет значения всех параметров, используемых в параметризованных функциях, содержимое файла CNF может меняться последовательной компиляции, если значения параметров меняются. Данный модуль создаёт также файл иерархических взаимосвязей (.hif) (hierarchy interconnect file), в котором документируются иерархические связи между файлами проекта, а также содержится информация, необходимая для показа иерархического дерева проекта в окне “Hierarchy Display”. Кроме того, данный модуль создаёт файл базы данных узлов (.ndb) (node database), в котором содержатся имена узлов проекта для базы данных назначений ресурсов.

Модуль построителя базы данных (Database Builder) использует файл иерархических связей HIF для компоновки созданных компилятором файлов CNF, в которых содержится описание проекта. На основании данных об иерархической структуре проекта

данный модуль копирует каждый файл CNF в одну базу данных без иерархической структуры. Таким образом, эта база данных сохраняет электрическую связность проекта.

Модуль логического синтезатора (Logic Synthesizer) применяет ряд алгоритмов, которые уменьшает использование ресурсов и убирают дублированную логику, обеспечивая тем самым максимально эффективное использование структуры логического элемента для архитектуры целевого семейства устройств. Данный модуль компилятора применяет также способы логического синтеза для требований пользователя по временным параметрам и др. Кроме того, логический синтезатор ищет логику для несоединённых узлов. Если он находит неприсоединённый узел, он убирает все примитивы, относящиеся к этому узлу.

Если проект не помещается при монтаже в одно устройство, модуль Partitioner (разделитель) разделяет базу данных на несколько ПЛИС одного и того же семейства, стараясь при этом разделить проект на минимально возможное число устройств. Разбиение проекта происходит по границам логических элементов, а число выводов, используемое для сообщения между устройствами, минимизируется.

Используя базу данных, обновлённую модулем разбиения, модуль трассировки (Fitter) приводит в соответствие требования проекта с известными ресурсами одного или нескольких устройств. Он назначает каждой логической функции расположение реализующего её логического элемента и выбирает соответствующие пути взаимных соединений и назначений выводов. Данный модуль пытается согласовать назначения ресурсов, то есть выводов, логических элементов, элементов ввода/вывода, ячеек памяти, чипов, клик, устройств, местной трассировки, временных параметров и назначения соединения выводов из файла назначений и конфигурации (.acf) (Assignment & Configuration File), с имеющимися ресурсами. Модуль имеет параметры, позволяющие определить способы трассировки, например автоматическое введение логических элементов или ограничение коэффициента объединения по входу. Если трассировка не может быть выполнена, то выдаётся сообщение, предлагающее выбор, игнорировать некоторые или все назначения либо прекратить компиляцию. Независимо от того, завершена ли полная трассировка проекта, данный модуль генерирует файл отчёта (.rpt) (report file), в котором документируется информация о разбиении проекта, именах входных и выходных контактов, временных параметрах проекта и неиспользованных ресурсах для каждого устройства в проекте. Возможно включить в файл отчёта разделы, показывающие назначения пользователя, файловую иерархию, взаимные соединения логических элементов и уравнения, реализованные в логических элементах.

Компилятор также автоматически создаёт файл трассировки (.fit), в котором документируются назначения ресурсов и устройств для всего проекта, а также информация о трассировке. Существует возможность дать указание модулю трассировщика сгенерировать выходные текстовые файлы проекта на языке AHDL (.tdo).

Экстрактор для функционального тестирования (Functional SNF Extractor) создаёт файл для функционального тестирования (.snf) Компилятор генерирует этот файл перед синтезом проекта, поэтому он содержит все узлы, присутствующие в первоначальных файлах проекта. Этот функциональный файл SNF не содержит информации о временных параметрах. Его генерация возможна только в случае, если компиляция проекта произошла без ошибок.

Экстрактор для тестирования временных параметров (Timing SNF Extractor) создаёт файл для тестирования временных параметров (,snf), который содержит данные о временных параметрах проекта.

Экстрактор для тестирования компоновки (Linked SNF Extractor) создаёт файл (.snf) для тестирования компоновки нескольких проектов. Такой файл SNF комбинирует информацию из файлов SNF двух типов: для тестирования временных параметров и функционального тестирования, которые были сгенерированы для этих нескольких проектов по отдельности. Скомпонованные проекты могут использовать устройства, принадлежащие разным семействам.

Программа записи в формат EDIF (EDIF Netlist Writer). Компилятор MAX+PLUS II может взаимодействовать с большинством стандартных программных средств САПР, которые могут читать файлы стандартного формата EDIF 200 или 300. Данный модуль компилятора, содержащий программу записи в формат EDIF, создаёт один или несколько выходных файлов в формате EDIF (.edo), содержащих информацию о функциях и временных параметров, полученную после проведения синтеза.

Программа записи в формат Verilog (Verilog Netlist Wtiter). Необязательный модуль, программа записи в формат Verilog. Генерирует выходные файлы с расширением .vo, содержащие информацию о функциях и временных параметрах, полученную после проведения синтеза.

Программа записи в формат VHDL (VHDL Netlist Writer). Необязательный модуль компилятора с программой записи в формат VHDL генерирует один или несколько выходных файлов (.vho) на языке VHDL с синтаксисом 1987 или 1993, содержащих информацию о функциях и временных параметрах, полученную после проведения синтеза.

Выходные файлы на языках описания аппаратуры можно использовать при верификации проекта с использованием внешнего симулятора.

Модуль ассемблера (Assembler). Модуль ассемблера преобразует назначения логических элементов, выводов и устройств, сделанные модулем трассировки Fitter, в программный образ для устройства в виде одного или нескольких двоичных объектных файлов для программатора (.pof), для некоторых устройств компилятор также генерирует ASCII-файлы JEDEC (.jed), содержащие информацию для программатора, конфигурационные ASCII-файлы (.ttf) и ASCII-файлы формата Intel (.hex).

Утилита диагностики проекта (Design Doctor Utility). Необяза

|

из

5.00

|

Обсуждение в статье: Система проектирования |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы