|

Главная |

Описание полей байта состояния

|

из

5.00

|

| Бит | Поле | Описание |

| 7:2 | RSVD | Зарезервированы, установлены в 0 |

| 1 | TXRDY | 1: Данные поставлены в очередь для передачи |

| 0 | RXRDY | 1: Буфер готов к приему данных |

Если данные поставлены в очередь для передачи, и получатель указал о готовности к приему (RXRDY во входящем байте состояния установлен в 1), следующий переданный байт будет является длиной данных. Если у JN513x или у отдаленного процессора нет никаких данных для передачи, то длина данных должна быть установлена в нуль. Передача может быть закончена отдаленным процессором после посылки ему байта состояния, если невозможно отправить данные ни в одном из направлений. Это может быть причиной того, что ни у какой стороны нет данных для передачи или получатель не имеет буфера в наличии. Если длина данных является ненулевой, данные из буфера передачи JN513x передаются, начиная с начала буфера. В то же самое время, приемный буфер JN513x заполняется входящими данными с его начала.

Отдаленный процессор, действуя как ведущий, должен определить большую из его приходящих или уходящих передач данных и деактивизировать IP_SEL, когда все передаваемые и получаемые данные переданы. Данные передаются в или из буферов, начиная с самого младшего адреса в буфере; каждое слово транслируется, начиная с MSB на последовательных линиях данных (рис 22).

Рис. 22. Временные диаграммы работы IP.

11.2. Передача по инициативе JN513x

Отправляемые JN513x данные записываются или в 0, или в 1 буфер интеллектуальной области внешней памяти. Затем вызовом функции bAHI_IpSendData () записывается буферное число вместе с длиной данных. Если вызов успешен, активизируется линия прерывания IP_INT, сообщая отдаленному процессору о наличии сообщения, готовом к отправке от JN513x. Когда отдаленный процессор начинает передачу в JN513x активизацией IP_SEL, линия IP_INT деактивизируется. Если передача неудачна и данные не переданы, тогда IP_INT снова активизируется для указания того, что данные все еще ожидают отправки.

Интерфейс может быть сконфигурирован на выработку внутреннего прерывания всякий раз, когда транзакция завершается (например, IP_SEL деактивизируется после начала передачи). Можно замаскировать это прерывание. О конце передачи может сообщить прерывание, или опрос интерфейса функцией bAHI_IpTxDone ()

Для получения данных интерфейс должен сначала быть инициализирован функцией vAHI_IpEnable (). После этого разряд RXRDY, посланный в байте состояния от блока IP, покажет, что данные могут быть получены JN513x. Успешное получение данных может быть обозначено прерыванием, или опросом интерфейса, используя bAHI_IpRxDataAvailable (). Потом данные восстанавливаются, используя bAHI_IpReadData ().

Чтобы одновременно послать и получать данные, приемный и передающий буферы должны быть разными.

11.3. Передача по инициативе удаленного процессора

Отдаленный процессор может инициализировать передачу для отправки данных на JN513x, активизируя подчиненный штырек выбора IP_SEL и генерируя свой байт состояния на линию IP_DI установкой бита TXRDY=1. После получения байта состояния от JN513x он проверяет наличие у JN513x буфера, готового к приему, считывая бит RXRDY. Если бит RXRDY=0, значит JN513x не может принять данные, удаленный процессор должен закончить передачу деактивизацией IP_SEL. Если бит RXRDY =1 - JN513x может принять данные; процессор должен в течение 8 тактов IP_CLK передать длину его сообщения по IP_DI. Процессор должен продолжить синхронизировать интерфейс, пока не сгенерирует достаточное количество синхроимпульсов для передачи всех данных, определенных в поле длины для JN513x. Затем процессор должен деактивизировать IP_SEL, чтобы показать, что передача закончена.

Данные можно послать в обоих направлениях сразу, но процессор должен гарантировать завершение обеих передач прежде, чем деативизирует IP_SEL.

12. Таймеры

12.1. Периферийный таймер / счетчик

Два таймера / счетных модуля общего назначения могут быть независимо конфигурированы для работы в одном из пяти режимов. Таймеры обладают следующими особенностями:

· 16-разрядный делитель частоты с программируемым коэффициентом деления;

· Синхронизируются от системного генератора;

· 16-разрядный счетчик, 16-разрядные регистры фронта и спада;

Режимы:

· Таймера: позволяет генерировать прерывания по достижении счетчиком значений регистров фронта и спада. Работа может быть разрешена внешним сигналом;

· Счетчика: подсчитывает перепады входного сигнала. Может подсчитывать фронты, спады или оба перепада;

· Модуляции длительности импульса: позволяет задавать временные параметры импульсов и выводить их в единичном или множественном количестве;

· Сбора данных: измерение временных параметров приложенного цифрового сигнала;

· Дельта-сигмы: режимы с возвращением к нулю (RTZ) и без возвращения к нулю (NRZ);

Блок-схема таймера изображена на рис. 23.

Рис. 23. Блок-схема таймера.

Синхроимпульсы для модуля таймера подаются от генератора на 16 МГц. Они поступают на 16-разрядный делитель частоты, который уменьшает их частоту в 2 в степени предмасштаба раз. Например, если значение предмасштаба равно 2, то частота выходного сигнала делителя составляет 4 МГц. Значение предмасштаба устанавливается функцией vAHI_TimerEnable ().

Работа счетчика может быть разрешена сигналом TIMxCK_GT. Когда эта возможность задействована (используя vAHI_TimerClockSelect ()), счетчик будет остановлен, если на входе лог. «1».

Если функцией vAHI_TimerEnable () разрешены прерывания, они будут генерироваться всякий раз, когда значение счетчика равно значению, сохраненному в регистрах фронта (Rise) или спада (Fall).

Внутренний сигнал разрешения (OE) включает или отключает выход таймера.

Сигналы таймера 0 CK_GT, CAP и OUT являются мультиплексными с DIO8, 9 и 10 соответственно; сигналы таймера 1 CK_GT, CAP и OUT тоже являются мультиплексными с DIO11, 12 и 13. Выбор функциональных возможностей этих штырьков между DIO и таймерами задается программно, но в любом случае таймеры будут функционировать внутренне.

12.1.1. Режим модуляции длительности импульса

Режим (PWM) Модуляции Длительности Импульса позволяет пользователю задавать период и длительность импульса. Импульс может быть сгенерирован однократно или как цепочка импульсов с нормой повторения, равной периоду.

В данном режиме период импульса и длительность его нулевого состояния заносятся в два независимых 16-разрядных регистра (спада и фронта). Содержимое счетчика возрастает и сравнивается с 16-разрядными регистрами фронта и спада. Когда значение счетчика равно значению регистра фронта, на выходе PWM происходит положительный перепад напряжения; когда счетчик достигает значения регистра спада, на выходе происходит отрицательный перепад и схема возвращается к исходному состоянию. В непрерывном режиме при достижении счетчиком значения регистра спада произойдет сброс счетчика и повторение цикла. В зависимости от режима работы значения заносятся в регистры фронта и спада через функцию vAHI_TimerStartRepeat () или vAHI_TimerStartSingleShot (). Выходной сигнал PWM выдается на TIMxOUT, если это разрешено функцией vAHI_TimerEnable ().

Рис. 24.

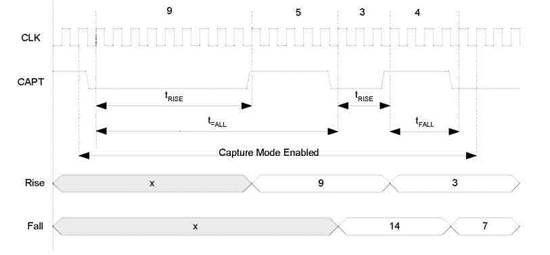

12.1.2. Режим сбора данных

Режим сбора данных может использоваться для измерения периода времени между перепадами сигнала на входе сбора данных (TIMxCAP). Переход в этот режим происходит посредством вызова функции vAHI_TimerStartCapture (), при этом запускается счетчик. При положительном перепаде входного сигнала содержимое счетчика заносится в регистр фронта, при отрицательном перепаде значение счетчика заносится в регистр спада. Длительность импульса - разница содержимого этих двух регистров, умноженная на период импульса синхронизации (во всех случаях частота синхронизации должна составлять 16 МГц, т.е. значение предмасштаба делителя равно 0). Функция vAHI_TimerReadCapture () останавливает счетчик, считывает содержимое регистров. Содержимое регистров фронта и спада будет обновлено всякий раз при обнаружении перепада импульса на входе сбора данных, поэтому при поступлении нескольких импульсов на TIMxCAP до остановки счетчика, будет сохранена только длительность последнего импульса.

Рис. 25. Режим сбора данных.

12.1.3. Режим счетчика / таймера

Счетчик/таймер может использоваться для синхронизации или генерации прерываний счета, используемых программным обеспечением. В режиме таймера источником импульсов является системный тактовый генератор, частота которого при желании может быть уменьшена делителем. Период таймера программируется в регистр спада, разрешается прерывание соответствия регистра спада. Таймер запускается или как однократный или как повторяющийся таймер (vAHI_TimerStartSingleShot () или vAHI_TimerStartRepeat ()) и генерирует прерывание при достижении счетчиком значения регистра спада.

Режим счетчика может быть использован для подсчета внешних событий. В качестве источника импульсов в этом случае используется входной штырек TIMxCK_GT, число событий программируется в регистр спада. Когда запрограммированное число фронтов сигнала зафиксировано на входном штырьке, генерируется прерывание.

12.1.4. Режим дельта-сигма

Доступен особый режим дельта-сигмы, позволяющий реализовать низкоскоростной ЦАП дельта-сигмы с разрешающей способностью до 16-бит. Это режим требует внешней RC-цепочки, подключенной между выходом DIO и общей шиной. Сгенерированный цифровой поток импульсов интегрируется RC-цепочкой в аналоговое напряжение. Время преобразования определено условием количества тактовых циклов. Длительность сгенерированных импульсов является периодом тактового цикла. Количество выводимых импульсов вместе с параметрами RC интегратора определяют итоговое аналоговое напряжение. Например, генерация приблизительно половины числа импульсов, составляющих законченный период преобразования, создаст напряжение на выходе RC, равное VDD1/2, если RC константа времени выбрана правильно. Во время преобразования импульсы будут псевдослучайно рассредоточены по всему циклу для создания устойчивого напряжения на выходе RC-цепи.

Выходной сигнал утверждается числом тактов, определенных в Высоком наборе регистров, задается vAHI_TimerStartDeltaSigma (), с полным периодом, составляющим 216 циклов.

Выход преобразователя дельта-сигмы может работать в режимах с возвратом к нулю (RTZ) или без возврата к нулю (NRZ). Режим NRZ позволяет выводить несколько импульсов друг рядом с другом. Режим RTZ гарантирует, что каждый следующий импульс будет отделен от предыдущего по крайней мере одним периодом. Это улучшает линейность, если активный и неактивный периоды импульса различны.

12.1.5. Пример применения таймера / счетчика

Рис. 26 показывает пример применения таймеров JN513x для управления скоростью вращения замкнутой системы. Таймер 0 конфигурирован в режиме PWM; длительность импульса задает средний ток через полевой транзистор и управляет мощностью двигателя.

Таймер 1 конфигурирован на подсчет фронтов импульсов на штырьке clk/gate за постоянный период. Он преобразует поток импульсов от Тахо-датчика в число, пропорциональное скорости мотора. Это число используется прикладным программным обеспечением, выполняющим алгоритм управления скоростью вращения.

Рис. 26. Схема контроля скорости вращения двигателя.

12.2. Таймер тактов

JN513x содержит аппаратный таймер, который может использоваться для выработки прерываний, используемых программным обеспечением. Прерывания этого таймера могут использоваться для обработки регулярных событий, таких как обновление часов операционной системы, поскольку интервал их следования считается эталонным. Также могут быть использованы для реализации пауз. Особенности этого таймера:

· 32-разрядный счетчик;

· 28-битовое значение соответствия;

· Маскируемое прерывание таймера;

· Одиночный, перезапускаемый или непрерывный режимы работы.

Таймер тактов синхронизирован от генератора центрального процессора (16 или 32 МГц), сигнал с которого подается на 32-разрядный сбрасываемый счетчик прямого действия через логический вентиль, управляемый сигналом блока режима (рис. 27). Регистр соответствия сравнивает содержимое счетчика с запрограммированным значением. Это значение может быть запрограммировано, используя vAHI_TickTimerInterval () в диапазоне от 0 до 0x0FFFFFFF. Выход регистра сравнения используется для управления счетчиком в различных режимах, может быть использован для генерации прерываний, если те разрешены. Режим таймера задается через функцию vAHI_TickTimerConfigure (), которая при вызове сбрасывает счетчик в нуль.

Рис. 27. Блок-схема таймера тактов.

Прерывания разрешаются через vAHI_TickTimerIntEnable (). Состояние прерывания определяется bAHI_TickTimerIntStatus () , и, если прерывание сгенерировано, состояние может быть сброшено vAHI_TickTimerIntPndClr ().

В одиночном режиме счетчик начинает отсчет с нуля до тех пор, пока его содержимое не станет равным запрограммированному значению. Затем сгенерируется сигнал соответствия, который вызывает прерывание, если оно разрешено, и счетчик прекращает счет. Счетчик может быть перезапущен при перепрограммировании режима, используя vAHI_TickTimerConfigure ().

В перезапускаемом режиме при совпадении значения счетчика с запрограммированным, счетчик сбрасывается и начинает счет с нуля. Если прерывания таймера разрешены, они будут генерироваться при сбросе счетчика.

Непрерывный режим подобен перезапускаемому за исключением того, что при достижении соответствующего значения счетчик не сбрасывается, а продолжает счет. Прерывание генерируется, если оно разрешено, когда значение счетчика совпадает с запрограммированным.

12.3. Таймеры пробуждения

JN513x содержит два 32-разрядных таймера пробуждения, тактируемых от внутреннего генератора на 32 кГц. Они могут работать во время периода бездействия, когда большая часть устройства выключена, могут быть использованы для выдержки времени, требуемой приложениями. Таймеры пробуждения не работают во время глубокого спящего режима. могут быть заблокированы в спящем режиме через программное управление. По истечении времени таймера пробуждения, как правило, генерируется прерывание, выводящее устройство из спящего режима. Особенности таймеров:

· 32-разрядный счетчик обратного действия;

· Произвольная работа во время периодов бездействия;

· Синхронизация от RC генератора на 32 кГц.

Таймер пробуждения состоит из 32-разрядного обратного счетчика, работающего от внутреннего генератора на 32 кГц. Когда содержимое счетчика достигает нуля, может быть сгенерировано прерывание или произойти пробуждение устройства. При достижении нуля счетчик продолжает обратный отсчет до тех пор, пока его не остановят. Если требуется случай прерывания или пробуждения, прерывания по таймеру должны быть разрешены, используя vAHI_WakeTimerEnable() перед загрузкой содержимого счетчика. Значение счета загружается через vAHI_WakeTimerStart () и запускает обратный счет; счетчик может быть остановлен в любое время, используя vAHI_WakeTimerStop (). Содержимое счетчика останется таким же, каким оно было при остановке таймера, прерывание при этом сгенерировано не будет. Состояние таймеров может быть опрошено функцией u8AHI_WakeTimerStatus (), которая показывает, работают ли таймеры. Факт истечения времени таймера может быть выяснен вызовом функции u8AHI_WakeTimerFiredStatus (), которая полезна при замаскированных прерываниях таймера.

12.3.1. Калибровка RC-генератора

RC генератор используется в спящем режиме, потребляет очень малую мощность, является модульным, не требует никаких внешних компонентов синхронизации, что отражается более низкой стоимостью. Поскольку все элементы генератора реализованы в микросхеме, его абсолютная точность и температурный коэффициент частоты ниже, чем у кварцевого, но после калибровки его точность приближается к кварцевому. Период времени бездействия должен быть как можно точнее приближен к запрограммированному, чтобы устройство просыпалось как раз ко времени начала важного события, например передаче маяка в протоколе IEEE802.15.4. Если время бездействия точно, устройство может быть запрограммировано на время пробуждения, близкое к расчетному времени события, таким образом сохранить минимальное потребление энергии. Если время бездействия менее точно, необходимо пробудить JN513x раньше, чтобы успеть к моменту начала события наверняка. Если устройство проснется раньше, оно будет бодрствовать дольше, что приведет к уменьшению срока службы аккумулятора.

Чтобы как можно точнее приблизить длительность периода бездействия к запрограммированному, частота RC генератора должна быть близка к 32 кГц точнее начальной 30%-ой погрешности. Для вычисления истинного числа импульсов генератора на 32 кГц, необходимых для нахождения в спящем режиме используется коэффициент калибровки, получаемый сравнением опорного сигнала калибровки от кварцевого генератора с частотой RC генератора во время бодрствования JN513x. Операция следующая:

· Нулевой таймер пробуждения блокируется и программируется на несколько импульсов от генератора 32 кГц

· Запускается режим калибровки, обнуляется калибровочный счетчик. Затем оба счетчика начинают работать: значение счетчика таймера пробуждения уменьшается, а значение калибровочного счетчика увеличивается.

· Когда значение счетчика таймера достигает нуля, калибровочный счетчик останавливается, позволяя программному обеспечению считать из него число импульсов генератора на 16 МГц, принятых в течение нескольких импульсов сигнала 32 кГц, запрограммированных в таймере. Таким образом, истинный период генератора на 32 кГц может быть расчитан и использован при программировании таймера пробуждения для определения периода бездействия с наибольшей точностью.

Калибровка может быть выполнена вызовом функции u32AHI_WakeTimerCalibrate (), которая подсчитывает в течение двадцати импульсов генератора 32 кГц количество импульсов генератора на 16 МГц и возвращает это число. Для RC генератора, работающего точно частоте на 32 кГц возвращаемое значение должно быть равно 10000. Если частота генератора больше 32 кГц, то число будет меньше 10000, если частота меньше - значение будет больше. Например, если получено значение 9000, т.е. частота генератора примерно 35 кГц, то для программирования 2-х секундного периода, в счетчик таймера должно быть загружено число 71 112 ((10000/9000) * (32000*2)), а не 64000.

13. Последовательные передачи данных

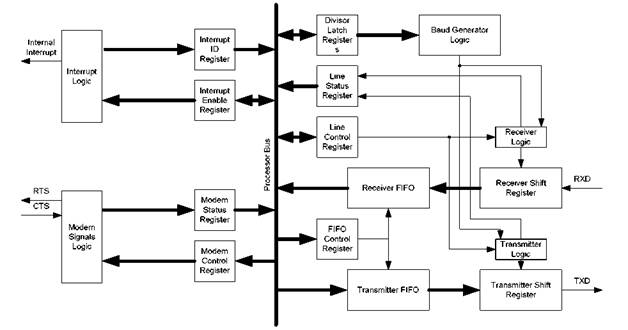

JN513x содержит два независимых универсальных асинхронных приемо-передающих (UART) последовательных коммуникационных интерфейса. Они реализуют операции, аналогичные промышленному стандарту 16550A устройства, работающего в режиме FIFO. Каждый интерфейс преобразует данные из параллельного формата в последовательный при передаче и из последовательного в параллельный при приеме. В обоих направлениях 16-байтовый FIFO буфер позволяет центральному процессору считывать и записывать символы на каждой транзакции. Это означает, что центральный процессор освобожден от познаковой обработки данных. Интерфейсы UART обладают следующими особенностями:

· Поддержка промышленных стандартов UART NS16450 и NS16550;

· 16 байтовые приемо-передающие FIFO буферы с прямым доступом к каждому уровню;

· Добавляет / удаляет биты начала, останова и контроля четности в / из последовательных данных;

· Независимо управляемый передают, получают, состояние и данные, посланные прерывания;

· Дополнительное модемное управление сигналами CTS и RTS;

· Полностью программируемые форматы данных: скорость в бодах, параметры начала, конца и четности;

· Обнаружение ложного бита начала;

· Внутренние диагностические возможности: локализация неисправности линии связи;

· Управление потоком данных программно или автоматически аппаратными средствами.

Блок-схема UART показана на рис. 28.

Рис. 28. Блок-схема UART.

Характеристики последовательного интерфейса программируются, используя вызов vAHI_UartSetControl (). Он определяет количество информационных разрядов (5, 6,7 или 8), четность, нечетность, обнаружение без четности и генерирует единичные или многократные стоповые биты.

Скорость передачи программируется между 4800, 9600, 19.2k, 38.4k, 76.8k и 115.2 kbaud через функцию vAHI_UartSetClockDivisor (). Для достижения более высоких или нестандартных скоростей передачи можно обращаться непосредственно к регистрам UART .

Предоставлены два аппаратных сигнала управления потоком данных: сброс передатчика (CRT) и запрос передачи (RTS). Сигнал CTS, посланный внешним устройством, сообщает о том, что внешнее устройство в UART готово получить данные. Сигнал RTS, посланный внешнему устройству, сообщает о готовности принять от него данные. Активный уровень обоих сигналов - низкий. Сигналом RTS управляют функцией vAHI_UartSetControl (), значение CRT может читаться u8AHI_UartReadModemStatus ().. Контроль и управление CRT и RTS – задача программы, обычно выполняемая как часть обработки прерывания. Сигналы не управляют частями аппаратных средств UART, а только указывают программному обеспечению состояние интерфейса UART. Альтернативно, программное обеспечение может установить режим автоматического контроля потока, где аппаратные средства управляют линией RTS , и передают данные при активном входящем сигнале CRT.

Символы читаются из приемного FIFO буфера с помощью u8AHI_UartReadData () (за один вызов считывается один байт), записываются в передающий FIFO буфер с помощью vAHI_UartWriteData (). Приемный и передающий FIFO буферы могут быть сброшены независимо друг от друга, используя vAHI_UartReset (). Состояние передатчика может быть проверено запросом u8AHI_UartReadLineStatus (), который указывает, пуст ли передающий FIFO буфер и если ли передаваемый символ. Состояние получателя также может быть проверено этим запросом, который может указать, зафиксированы ли случаи, такие как ошибка четности, ошибка синхронизации кадра, прерывание разрыва, ошибка переполнения (получен символ при заполненном принимающем буфере).

Сигналы UART 0 CTS, RTS, TXD и RXD – мультиплексные соответственно с DIO4, 5, 6 и 7, а сигналы UART 0 CTS, RTS, TXD и RXD – соответственно с DIO17, 18, 19 и 20. Если использование сигналов CRT и RTS не требуется для работы с внешними устройствами, то они могут быть заблокированы через программное управление, что позволяет использовать штырьки в качестве DIOx.

13.1. Прерывания

Управление прерываниями блока UART осуществляется функцией vAHI_UartSetInterrupt (). Выработка прерывания может произойти в следующих случаях:

· Полученные Данные Доступны: происходит, когда очередь данных в Rx FIFO достигает определенного уровня (уровень может быть задан как 1, 4, 8 или 14).

· Передающий FIFO пуст: генерируется при чтении последнего символа из TX FIFO и начале его передачи.

· Состояние Линии Получателя: установлен, когда выполняется одно из следующих условий: (1) Ошибка Четности - символ в заголовке приемного FIFO был получен с ошибкой четности, (2) Ошибка переполнения – FIFO заполнен и приемным сдвиговым регистром получен символ, (3) Ошибка кадровой синхронизации - у символа в заголовке приемного FIFO нет правильного стопового бита и (4), Прерывание Разрыва – происходит, если линия RXD находилась в низком состоянии на протяжении передачи всего символа. Источник прерывания определяется, используя u8AHI_UartReadLineStatus ().

· Модемное Состояние: генерируется при изменении состояния линии CRT.

13.2. Применение UART

Следующий пример иллюстрирует подключение UART посредством 9 штырькового соединителя с PC. Программный комплект разработчика использует такой интерфейс для отладки JN513x. Поскольку уровень напряжения на штырьках JN513x не соответствует уровню линии RS232, используется согласующее устройство (рис. 29).

Рис. 29. Соединение JN513х с COM-портом PC.

13.3. Пример программы

Следующий пример демонстрирует конфигурирование UART0 и вывод сообщения «Hello World»

Текст программы:

/* Выбор uart0 */

vAHI_UartEnable(E_AHI_UART_0);

/* установка скорости передачи */

vAHI_UartSetClockDivisor(0, E_AHI_UART_RATE_38400);

/* установка четности, стартового бита, количество битов данных */

vAHI_UartSetControl(E_AHI_UART_0,

E_AHI_UART_EVEN_PARITY,

E_AHI_UART_PARITY_DISABLE,

E_AHI_UART_WORD_LEN_8,

E_AHI_UART_1_STOP_BIT,

E_AHI_UART_RTS_HIGH);

/* вывод сообщения */

char acstring[] = “Hello World”;

char *pcstring = acstring;

while (*pcstring)

{

vAHI_UartWriteData(E_AHI_UART_0, *pcstring);

pcstring++;

}

14. Двухпроводной последовательный интерфейс

JN513x включает промышленный стандартный двухпроводный синхронный последовательный интерфейс (SIF), который обеспечивает простой и эффективный метод обмена данными между устройствами. Для выполнения двунаправленной передачи данных система использует последовательную линию данных (SIF_D) и последовательную линию синхронизации (SIF_CLK) и обладает следующими особенностями:

· Совместимый с I2C и SMbus внешними устройствами;

· Программируемая частота синхронизации;

· Задержка синхроимпульсов медленными устройствами;

· Бит подтверждения;

· Обнаружение занятости шины;

· Поддержка 7 и 10 битовой адресации;

Регистр предмасштаба, установленный функцией vAHI_SiConfigure () , позволяет конфигурировать скорость интерфейса до 400kbit/s. Тактовый генератор обнаруживает задержку синхроимпульсов, создаваемую некоторыми подчиненными устройствами (рис. 30).

Рис. 30. Блок-схема двухпроводного последовательного интерфейса.

Контроллер Байта Команды обрабатывает трафик на уровне байта. Он считывает данные из Регистра Команды и переводит их в последовательности, основанные на передаче одного байта. Установка служебных битов начала, остановки, чтения, записи и подтверждения в регистре команды, используя vAHI_SiSetCmdReg (), позволяет управлять передачей данных по шине.

Сдвиговый регистр ввода - вывода содержит данные, связанные с текущей передачей. Во время операции чтения данные сдвигаются в этом регистре с линии SIF_D. Когда чтение закончено, байт копируется в приемный регистр и может быть прочитан, используя функцию u8AHI_SiReadData8 ().

Во время операции записи содержимое передающего регистра копируется в сдвиговый регистр с последующей выдачей на линию SIF_D. К передающему регистру можно обратиться, используя vAHI_SiWriteData8 (). Можно настроить интерфейс на генерацию прерывания после завершения передачи или приема байта, используя функцию vAHI_SiConfigure (). Если это нежелательно, можно опросить состояние интерфейса с помощью функций bAHI_SiPollBusy () и bAHI_SiPollTransferInProgress ().

Первый байт данных, переданный контроллером после бита начала содержит адрес подчиненного устройства. JN513x поддерживает 7-битовые и 10-битовые адреса, генерируя их в одном или двух процессах передачи адреса. Только устройство с соответствующим адресом ответит возвращением бита подтверждения. Используемый подчиненный адрес указывается в функции vAHI_SiWriteSlaveAddr ().

14.1. Подключение устройств

Линии синхронизации и данных SIF_D и SIF_CLK мультиплексны и линиями DIO 14 и 15 соответственно (рис. 31). Эти линии выполняют функции последовательного интерфейса при активизации его вызовом vAHI_SiConfigure (). Обе линии двунаправлены, соединены с источником питания с помощью внутренних резисторов номиналом 45КΩ. Использование внутренних резисторов задается программно. Однако рекомендуется использовать внешние резисторы номиналом 4.7 kΩ для надежности операций на высоких шинных скоростях, как показано на рисунке. Когда шина свободна, на обеих линиях лог «1». Выходные каскады подключенных к шине устройств должны быть с открытым стоком или открытым коллектором, чтобы выполнить функцию защитного-И. Количество соединяемых с шиной устройств ограничивается исключительно шинным пределом емкости 400pF.

Рис. 31. Подключение устройств к интерфейсу SIF.

14.2. Задержка синхроимпульсов

Ведомые устройства создавать задержку синхроимпульсов для замедления скорости передачи битов информации. После установки контроллером SIF_CLK в нулевое состояние, устройство может перехватить этот сигнал самостоятельной установкой SIF_CLK в нуль в течение необходимого периода и затем отпустить его. Если период перехвата SIF_CLK устройством больше периода установки SIF_CLK самим контроллером в нулевое состояние, получающийся на разнице двух периодов интервал времени и образует задержку синхроимпульсов. В течение этого интервала контроллер находится в состоянии ожидания: ждет отпускания SIF_CLK устройством и возвращения линии в единичное состояние. Иллюстрация процесса показана на рис. 32.

Рис. 32. Временные диаграммы задержки синхроимпульсов.

14.3. Пример программы

Двухпроводный протокол последовательного интерфейса реализован комбинацией аппаратных средств и программного обеспечения. Как правило, стандартный цикл коммуникации состоит из четырех частей:

· Выработка сигнала начала;

· Передача адреса подчиненного устройства;

· Передача данных;

· Выработка стопового сигнала.

Следующий пример кода показывает, как читать ряд значений от подчиненного устройства в буфер. Такой пример может найти реализацию при регистрации данных от датчика.

Заметим, что функция bAHI_SiPollTransferInProgress () используется для блокировки выполнения до полной передачи байта. Приложения более высокой производительности должны использовать прерывания для обнаружения конца передачи как фоновую задачу основной программы.

Формы сигналов иллюстрирующие работу функции bSIFRead (), показаны на рис. 33.

Рис. 33. Временные диаграммы работы SIF.

Текст программы:

PRIVATE bool_t bSIFRead(uint8 u8SlaveAddress, uint8 *pau8ReadBuffer, uint32

u32Length)

{

int i;

for (i=0; i<u32Length; i++)

{

/* указание адреса подчиненного устройства */

vAHI_SiWriteSlaveAddr(u8SlaveAddress, E_AHI_SI_SLAVE_RW_SET);

/* send read command */

vAHI_SiSetCmdReg(E_AHI_SI_START_BIT, E_AHI_SI_NO_STOP_BIT,

E_AHI_SI_NO_SLAVE_READ, E_AHI_SI_SLAVE_WRITE, E_AHI_SI_SEND_ACK, E_AHI_SI_NO_IRQ_ACK);

while(bAHI_SiPollTransferInProgress()); /* busy wait */

if (bAHI_SiPollArbitrationLost() | bAHI_SiPollRxNack())

{

/* release bus & abort */

vAHI_SiSetCmdReg(E_AHI_SI_NO_START_BIT, E_AHI_SI_STOP_BIT,

E_AHI_SI_NO_SLAVE_READ, E_AHI_SI_SLAVE_WRITE, E_AHI_SI_SEND_ACK, E_AHI_SI_NO_IRQ_ACK);

return FALSE;

}

if (i < u32Length - 1)

{

/* read and ack */

vAHI_SiSetCmdReg(E_AHI_SI_NO_START_BIT, E_AHI_SI_NO_STOP_BIT,

E_AHI_SI_SLAVE_READ, E_AHI_SI_NO_SLAVE_WRITE,

E_AHI_SI_SEND_ACK, E_AHI_SI_NO_IRQ_ACK);

}

else /* last byte */

{

/* read, stop, nack */

vAHI_SiSetCmdReg(E_AHI_SI_NO_START_BIT, E_AHI_SI_STOP_BIT,

E_AHI_SI_SLAVE_READ, E_AHI_SI_NO_SLAVE_WRITE, E_AHI_SI_SEND_NACK, E_AHI_SI_NO_IRQ_ACK);

}

while(bAHI_SiPollTransferInProgress()); /* busy wait */

if (bAHI_SiPollArbitrationLost())

{

/* release bus & abort */

vAHI_SiSetCmdReg(E_AHI_SI_NO_START_BIT, E_AHI_SI_STOP_BIT,

E_AHI_SI_NO_SLAVE_READ, E_AHI_SI_NO_SLAVE_WRITE, E_AHI_SI_SEND_ACK, E_AHI_SI_NO_IRQ_ACK);

return FALSE;

}

/* Store data read from device */

pau8ReadBuffer[i] = u8AHI_SiReadData8();

}

/* transfer complete */

vAHI_SiSetCmdReg(E_AHI_SI_NO_START_BIT, E_AHI_SI_STOP_BIT,

E_AHI_SI_NO_SLAVE_READ, E_AHI_SI_NO_SLAVE_WRITE, E_AHI_SI_SEND_ACK, E_AHI_SI_NO_IRQ_ACK);

return TRUE;

}

15. Аналоговая периферия

JN513x содержит группу аналоговых внешних устройств, позволяющих осуществить прямое подключение внешних датчиков, переключателей и исполнительных механизмов.

Имеются четыре входа АЦП, два ввода компаратора и два выхода ЦАП (рис. 34). К аналоговым штырькам ввода - вывода на JN513x могут быть приложены сигналы, не превышающие VDD1 более, чем на 0,3В.

Рис. 34.

Для обеспечения хорошей изоляции от цифрового искажения, аналоговые внешние устройства запитываются от отдельного стабилизатора, подключенного к аналоговой ветке питания VDD1 и аналоговой основе VSSA.

Аналоговым внешним устройствам необходим источник опорного напряжения для выполнения операций. Они могут использовать или внутренний источник, или внешний, подключаемый к штырьку VREF. Это напряжение задается относительно общей шины; эксплуатационные показатели аналоговых внешних устройств напрямую зависят от качества этого источника.

Опорное напряжение Vref для АЦП и ЦАП может быть выбрано vAHI_ApConfigure () между внутренним или внешним источником опорного напряжения.

При сбросе и в глубоком спящем режиме все аналоговые внешние устройства выключены, выводы ЦАП находятся в высокоимпедансном состоянии. В спящем режиме АЦП и ЦАП выключены, выводы ЦАП в высокоимпедансном состоянии, компаратор может использоваться для пробуждения.

15.1. Аналого-цифровой преобразователь

12-битовый АЦП (аналого-цифровой преобразователь) использует алгоритм последовательного приближения для выполнения преобразований с высокой точностью, что как правило требуется в беспроводных сенсорных сетях. У него есть шесть мультиплексных асимметричных входных каналов: четыре доступны внешне, один связан с внутренним температурным датчиком, и один связан с датчиком контроля напряжения питания схемы.

15.1.1. Операция

Входной диапазон АЦП может быть установлен или между 0V и опорным напряжением, или между 0V и двойным опорным напряжением. Может быть использован внутренний или внешний источник опорного напряжения VREF. Например, если VREF=1.2V, входной диапазон АЦП может быть установлен между 0V и 2.4V.

Таблица 4

Параметры АЦП

| Опорное напряжение | Указатель уровня | Предельное входное напряжение АЦП | Величина напряжения питания |

| 1.2V | 0 | 1.2V | 2.2V - 3.6V |

| 1.6V | 0 | 1.6V | 2.2V - 3.6V |

| 1.2V | 1 | 2.4V | 2.6V - 3.6V |

| 1.6V | 1 | 3.2V | 3.4V - 3.6V |

АЦП тактируется сигналом частотой 16 МГц, поделенной до 500 кГц. В процессе преобразования аналоговый вход коммутируется через мультиплексор на вход АЦП, но оцифровка происходит не сразу, а спустя промежуток времени – период отсчета. Период отсчета определен как количество тактов аналого-цифрового преобразователя и может быть запрограммирован как 2, 4, 6 или 8 тактов. Скорость преобразования составляет (2 x интервала выборки) + (14 тактов синхронизации), например если период отсчета установлен как 2 такта, а синхронизация происходит с частотой 500 кГц, то скорость преобразования будет составлять 2 x 2 + 14 = 18 тактов, 36μsecs или 27.7 кГц.

Если входное сопротивление источника аналогового сигнала составляет 1 КΩ и меньше, то период отсчета должен быть установлен в 2 такта. Вход аналого-цифрового преобразователя может быть представлен эквивалентной схемой 5 КΩ резистора цепей переключателя и конденсатора на 8pF. Период отсчета может быть вычислен, путем прибавления исходного сопротивления датчика к сопротивлению переключателя и умножения суммы на емкость - получения константы времени. Предполагая нормальную экспоненциальную RC зарядку, может быть вычислено количество констант времени, требуемое для получения допустимой погрешности. Так, 7 констант времени (значение константы умножено на 7) дают погрешность 0.1 %; таким образом для 12-битовой точности должно быть достаточно произведение константы на 10. Для источника с нулевым сопротивлением у<

|

из

5.00

|

Обсуждение в статье: Описание полей байта состояния |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы