|

Главная |

ПРИНЦИП РАБОТЫ ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

|

из

5.00

|

Рабочий цикл центрального процессора:

01. На буферный регистр адреса центрального процессора посылается содержимое счётчика адреса команд.

02. На буферный регистр адреса запоминающего устройства посылается содержимое буферного регистра адреса центрального процессора.

03. Из запоминающего устройства по адресу счётчика адреса команд происходит выборка адреса команды и передача на буферный регистр адреса запоминающего устройства.

04. На буферный регистр данных центрального процессора подаётся содержимое буфера регистра данных запоминающего устройства.

05. На регистр команд посылается команда с буферного регистра данных центрального процессора.

06. На буферный регистр адреса центрального процессора посылается первый адрес операнда команды.

07. На буферный регистр адреса запоминающего устройства посылается содержимое На буферный регистр адреса центрального процессора.

08. Из запоминающего устройства происход выборка данных по адресу первого операнда команды и передача его на буферный регистр адреса запоминающего устройства.

09. На буферный регистр данных центрального процессора подаётся содержимое буфера регистра данных запоминающего устройства.

10. На аккумулятор передаётся содержимое буферного регистра данных центрального процессора.

11. На буферный регистр адреса центрального процессора посылается содержимое посылается второй адрес операнда команды.

12. На буферный регистр адреса запоминающего устройства посылается содержимое буферного регистра адреса центрального процессора.

13. Из запоминающего устройства происходит выборка данных по адресу второго операнда команды и передача его на буферный регистр адреса запоминающего устройства.

14. На буферный регистр данных центрального процессора подаётся содержимое буфера регистра данных запоминающего устройства.

15. На арифметико-логическое устройство посылается содержимое буферного регистра данных центрального процессора.

16. Расшифровка кода операций и подача кода на схему выработки.

17. Выполнение операций в арифметико-логическом устройстве.

18. Результат арифметическо-логического устройства записывается в запоминающие устройство по второму адресу.

19. В запоминающие устройство по адресу второго операнда команды записывается содержимое буферного регистра данных запоминающего устройства.

20. На буферный регистр данных запоминающего устройства посылается содержимое буферного регистра данных центрального процессора.

21. На буферный регистр данных центрального процессора посылается содержимое арифметико-логического устройства.

22. Изменить счётчик адреса команд.

23. Возврат на первый шаг если не возникла команда "Конец работы".

Система команд процессора Intel 8086 насчитывает более 10 разнообразных форматов команд, отличающихся как длиной формата (машинная команда может занимать от 1 до 6 байт, не считая возможных предшествующих ей префиксов), так и распределением полей в отдельных байтах команды.

Используются 3 вида префиксов (префиксных байтов), которые предшествуют команде и определенным образом влияют на ее выполнение.

К префиксам относятся:

1) seg – префикс замены сегмента;

2) rep – префикс повторения;

3) lock – префикс блокировки шины.

1) Префикс замены сегмента используется для переназначения стандартных сегментов, используемых по умолчанию при обращении к памяти за операндом и (или) при записи результата.

Адрес переназначения сегмента занимает 2 средних бита в префиксном байте

2) Префикс повторения используется исключительно перед командами обработки строк и заставляет повторять ее выполнение многократно в целях поэлементной обработки всей строки.

Использование префикса rep позволяет организовывать цикл по последовательной обработке элементов строки на аппаратном, а не на программном уровне.

3) При выполнении команды с предшествующим ей префиксом lock на все время выполнения команды блокируется шина, связывающая процессор с памятью и портами ввода-вывода.

Действие любого префикса распространяется только на одну машинную команду, которая следует непосредственно за ним.

Форматы команд

1. Однобайтная безадресная команда:

ОрС

7 0

Рис. 2.1. Однобайтная одноадресная команда

Подобный формат используется либо командами с неявной адресацией, либо командами, не использующими операндов.

Примерами команд первого типа могут служить команды обработки строк, в которых строка–источник и строка-приемник неявно адресуются с использованием регистров SI и DI соответственно.

К ним относятся:

MOVS – пересылка строки,

LODS – загрузка строки,

STOS – запись в память строки,

CMPS – сравнение строк,

SCAS – сканирование строки.

2. Однобайтная одноадресная команда

ОрС W REG

7 4 3 2 0

Рис.2.2 . Однобайтная одноадресная команда

Эта команда задает прямой адрес регистрового операнда (поле reg). Бит w задает длину операнда (1 – слово, 0 – байт).

|

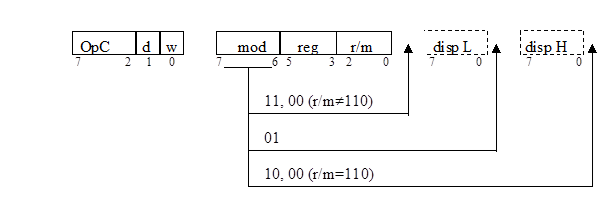

3. Двухадресная команда с постбайтом адресации

Рис.2.3. Двухадресная команда с постбайтом адресации

Бит d кода операции (direction - направление) определяет, по какому адресу записывается результат операции (при d = 1 – в регистр reg, при d = 0 – в регистр или память, адресуемые полем r/m).

Подобный формат широко используется для разнообразных арифметических и логических команд.

|

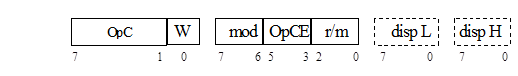

4. Одноадресная команда с постбайтом адресации

Рис.2.4. Одноадресная команда с постбайтом адресации

В отличие от предыдущего формата, среднее поле постбайта адресации является расширением кода операции (Е – Extended).

Подобный формат используется, во-первых, для однооперандных команд (например, INC, DEC, NEG – negative – изменение знака, NOT – инвертирование) и, во-вторых, для двухоперандных команд, в которых один из операндов адресуется неявно (например, MUL/IMUL – умножение, DIV/IDIV – деление, в которых один из операндов является аккумуляторным, а также команды сдвигов, в которых счетчик числа сдвигов адресуется неявно регистром CL).

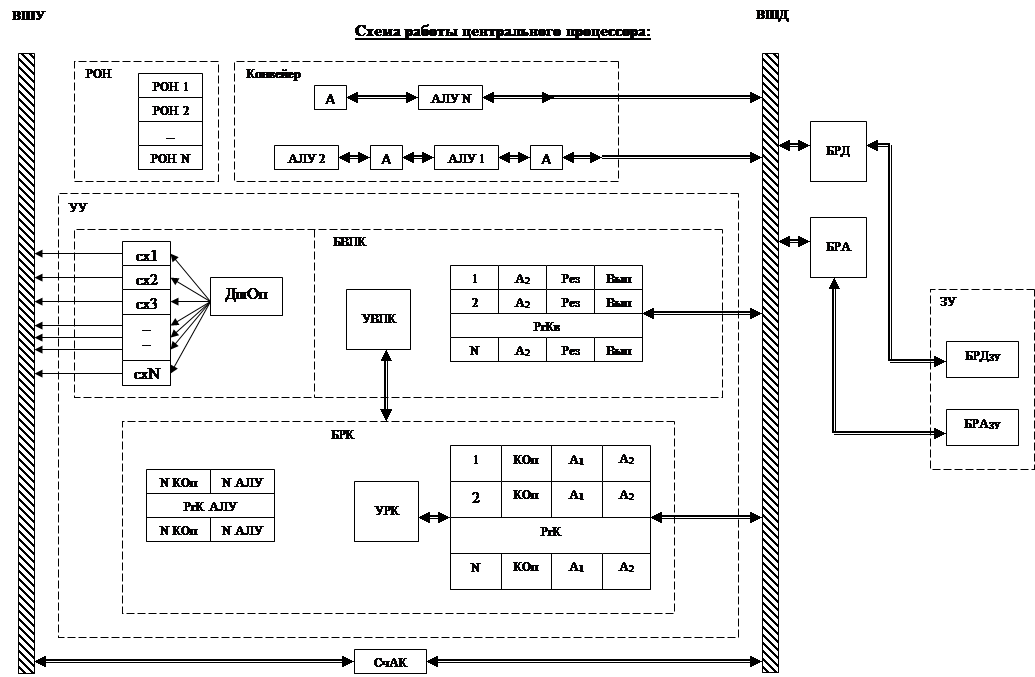

На рис. 2.2 приведена схема работы центрального процессора.

Где:

ВШУ, ВШД - внутренняя схема управления, данных;

РОН - регистр общего назначения;

АЛУ - арифметико-логическое устройство;

А - аккумулятор;

БВПК - блок восстановления последовательности команд;

сх1...схN (N=2n) - схемы выработки управляющего сигнала (не регистр);

ДшОп - Дешифратор операций;

УВПК - устройство восстановления последовательности команд;

А1, А2 - операнды;

Рез - Результат операции;

Вып - флажок выполнено/не выполнено;

РгКв - регистр команд (выход);

КОп - Код операции;

УУ - устройство управления;

РгК - регистр команд;

КОп - Код операции;

БРК - блок распределения команд;

УРК - устройство распределения команд;

СчАК - счетчик адреса команд (+δ - прибавляет по байту);

БРА, БРД - буферные регистры адреса, данных;

ЗУ - запоминающее устройство;

БРАЗУ, БРДЗУ - буферные регистры адреса, данных запоминающего устройства;

Согласно данной схеме Рабочий цикл Центрального процессора имеет следующий вид

Шаги 1-5: MOV(СчАК,РгК i);

Шаги 6-10: MOV(А1,РгК[А1] i);

Шаги 11-15: MOV(А2,РгК[А2]i);

Шаг 16: PARBEGIN

16.1: УРК(РгКi,РгКАЛУi);

16.2: ДшОп(РгКi-1);

16.3: выполнение Оп i-2;

16.4: УВПК(РгКвi-3);

PAREND;

Шаги 17-22: MOV(РгКв[Рез]i-4,[А2]);

Шаг 23: СчАК + δ;

Шаг 24: → Шаг 1.

Где:

Оп - операция;

MOV - "проход", введено для сокращения, каждый MOV означает 5 соответствующих шагов:

1. БРА := А1;

2. БРАЗУ := БРА;

3. БРДЗУ := [БРАЗУ];

4. БРД := БРДЗУ;

5. [А2] := БРД.

- то, что стоит в кв. скобках [] означает, что берется не А2, а значение по адресу А2;

- индексы i-1, i-2, i-3 и т.д. означают, что берется предыдущая команда; предпредыдущая и т.п. (которая уже прошла обработку на предыдущем блоке);

-шаги алгоритма 16.1, 16.2, 16.3 и 16.4 выполняются ПАРАЛЛЕЛЬНО

|

из

5.00

|

Обсуждение в статье: ПРИНЦИП РАБОТЫ ЦЕНТРАЛЬНОГО ПРОЦЕССОРА |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы