|

Главная |

Формирование устройства управления

|

из

5.00

|

Санкт-Петербургский Государственный Университет Телекоммуникаций

Им проф. М.А. Бонч-Бруевича

Кафедра «Программной инженерии и Вычислительной Техники»

Курсовой проект

По дисциплине «Вычислительная и микропроцессорная техника»

Тема: «Проектирование и программирование в кристалл FPGA микропроцессор, выполняющий команды, указанные в выданном варианте задания»

Выполнил: Напсоков Б.Р.

Группа ИКТВ-31

Факультет ИВО

Номер выполненного варианта 3

Проверила: __________Желтова Е.А

(Подпись)

Санкт-Петербург

Содержание

Содержание. 2

Задание. 3

Часть №1. 3

Часть №2. 6

Часть №3. 9

Часть №4. 11

Часть №5. 15

Задание:

Вариант 3

IN port, R1;

CMP R0, R1;

ASR R1;

ASR R1;

Программа предполагает ввод данных в регистр 1 с тумблеров, сравнение с «0» для получения флагов состояний и арифметический сдвиг содержимого регистра вправо на два разряда. (При арифметическом сдвиге освобождающиеся разряды заполняются знаком числа.) Содержимое регистра выводится на сегментные индикаторы, содержимое триггеров флагов – на светодиоды.

Часть №1

Формирование памяти инструкций.

Цель работы. Получение представления о формировании потока инструкций в RISC-процессоре. Ознакомление с программированием на VHDL.

Постановка задачи. Необходимо построить схему блока, содержащую память инструкций и программный счетчик. Блок памяти инструкций представлен в виде простейшего КЦУ, к выходу которого подключены два 8-разрядных регистра. Обращение к регистрам возможно при активном уровне «1» на разрешающем входе. На вход КЦУ поступают адреса от программного счетчика. Каждый адрес, таким образом, вызывает определенный программный код, который отображается в выходном буфере. Максимальный объем проектируемой памяти – восемь 16-разрядных ячеек, поэтому строим 4-разрядный счетчик, младший разряд которого формирует тактовую частоту для исполнительного блока, а три старших разряда – адреса на блок памяти.

Программа 1.1

library ieee;

use ieee.std_logic_1164.all;

entity raminst is

port(

adr_i: in bit_vector(3 downto 1);

data_out: out bit_vector(15 downto 0)

);

end raminst;

architecture BBB of raminst is

begin

p0: process (adr_i)

begin

case adr_i is

when "000"=>data_out<="0000000100000000";

when "001"=>data_out<="0100000100000000";

when "010"=>data_out<="1100000100000000";

when "011"=>data_out<="1100000100000000";

when others=>data_out<="0000000000000000";

end case;

end process;

end ;

Программа 1.2

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity cnt4 is

port(

clk: in std_logic;

ena : in std_logic;

res : in std_logic;

q: out std_logic_vector(3 downto 0)

);

end cnt4;

architecture arch of cnt4 is

signal cnt: std_logic_vector(3 downto 0);

begin

process (clk,res)

begin

if (res = '0') then cnt<=(others=>'0');

elsif(rising_edge(clk)) then

if(ena ='1') then

cnt <=cnt + "0001";

end if;

end if;

end process;

q <= cnt;

end arch;

Программа 1.3.

library ieee;

use ieee.std_logic_1164.all;

entity reg8 is

port(

data_i: in std_logic_vector(7 downto 0);

clk_i: in std_logic;

ena : in std_logic;

ctrl : in std_logic;

data_out: out std_logic_vector(7 downto 0)

);

end reg8;

architecture arch of reg8 is

signal regist: std_logic_vector(7 downto 0);

begin

process (clk_i)

begin

if(rising_edge(clk_i)) then

if(ena ='1') then

regist <= data_i;

end if;

end if;

end process;

data_out <= regist when ctrl = '1' else "ZZZZZZZZ";

end arch;

Схема устройства:

Временная диаграмма устройства:

Часть №2.

Формирование устройства управления.

Цель: получение представления о дешифрации потока инструкций в RISC-процессоре.

Постановка задачи. Необходимо построить устройство, посылающее сигналы управления на исполнительный блок. Из структуры кода команды следует, что такое устройство должно иметь основной дешифратор на 3 адресных входа, куда поступает код операции, и дешифраторы адресов источников и приемников. Эти дешифраторы будут иметь по два адресных входа и вход управления подключением, управляемый основным дешифратором. Так как команда пересылки MOV R(s), R(d) исполняется по принципу: R(d)<=R(s) + R(0), то для такой команды необходимы два источника: регистр нуля и регистр общего назначения. Кроме того, два источника могут понадобиться и для случая использования команды сложения двух операндов с занесением результата в третий регистр: ADD R(s1), R(s2), R(d). Поэтому договоримся, что два дешифратора определяют источники по разрядам кода Р11, Р10 и Р9,Р8; а один дешифратор определяет приемник по разрядам кода Р7,Р6. В случае, когда команда имеет только один операнд – источник, приемник определяется по разрядам Р9, Р8, т.е. с помощью дешифратора второго источника.

Основной дешифратор управляет также выводом операнда данных на внутреннюю шину данных, а для команд сложения и переноса с регистровой адресацией формирует сигнал активизации АЛУ (выход en_add).

Программа 2.1

library ieee;

use ieee.std_logic_1164.all;

entity dec is

port(

adr_i: in bit_vector(2 downto 0);

data_out: out bit_vector(7 downto 0)

);

end dec;

architecture BBB of dec is

begin

p0: process (adr_i)

begin

case adr_i is

when "000"=>data_out<="00000001";

when "001"=>data_out<="00000010";

when "010"=>data_out<="00000100";

when "011"=>data_out<="00001000";

when "100"=>data_out<="00010000";

when "101"=>data_out<="00100000";

when "110"=>data_out<="01000000";

when "111"=>data_out<="10000000";

end case;

end process;

end ;

Программа 2.2

library ieee;

use ieee.std_logic_1164.all;

entity dec1 is

port(

adr_i: in bit_vector(1 downto 0);

en: in bit;

data_out: out bit_vector(3 downto 0)

);

end dec1;

architecture BBB of dec1 is

begin

process (adr_i)

begin

if (en = '1') then

data_out(0)<=(not(adr_i(0)))and(not(adr_i(1)));

data_out(1)<=(adr_i(0))and(not(adr_i(1)));

data_out(2)<=(not(adr_i(0)))and(adr_i(1));

data_out(3)<=(adr_i(0))and(adr_i(1));

elsif (en ='0') then

data_out(3 downto 0)<="0000";

end if;

end process;

end ;

Схема устройства:

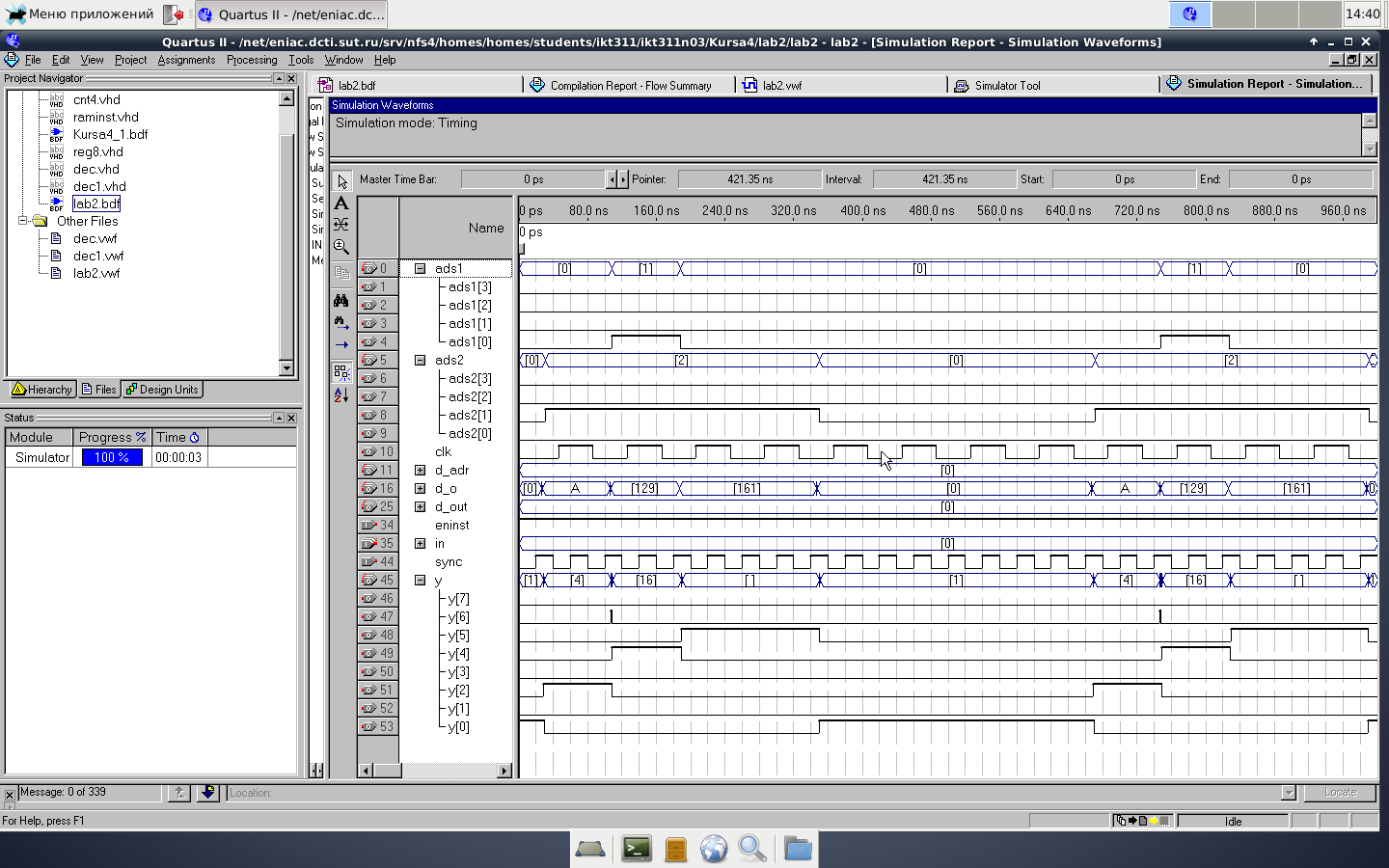

Временная диаграмма работы устройства:

Часть №3

|

из

5.00

|

Обсуждение в статье: Формирование устройства управления |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы