|

Главная |

Формирование блоков регистров

|

из

5.00

|

Цель: получение представления о временном хранении данных в RISC-процессоре.

Постановка задачи: исполнительное устройство нашего процессора содержит два блока: блок регистров, где операнды временно хранятся для производства операций над ними, и блок АЛУ, где собственно и производятся операции. Наша задача построить блок регистров, содержащий четыре 8-разрядных регистра. Один из этих регистров постоянно хранит «0», т.е. не может быть приемником информации, три других же предполагаются под общее назначение. На общую шину данных может поступать как значение непосредственного операнда источника, так и содержимое выхода сумматора АЛУ. Простейшей развязкой этих сигналов в нашем случае может служить блок элементов 2ИЛИ. У каждого регистра буфер записи может быть включен только в том случае, если этот регистр служит приемником операнда (позиции приемник или второй источник).

Программа 3.1

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity reg_sb is

port(

data_i: in std_logic_vector(7 downto 0);

clk_i: in std_logic;

ena : in std_logic;

ctrl : in std_logic;

sbst : in std_logic;

data_out: out std_logic_vector(7 downto 0)

);

end reg_sb;

architecture arch of reg_sb is

signal regist: std_logic_vector(7 downto 0);

begin

process (clk_i)

begin

if(rising_edge(clk_i)) then

if(ena ='1') then

regist <= data_i;

end if;

end if;

end process;

process (ctrl,sbst)

begin

if(ctrl='1') then

if(sbst ='0') then

data_out <= regist;

elsif(sbst ='1') then

data_out <=not(regist) + "00000001";

elsif(ctrl='0') then

data_out<="00000000";

end if;

end if;

end process;

end arch;

Регистр сдвига.

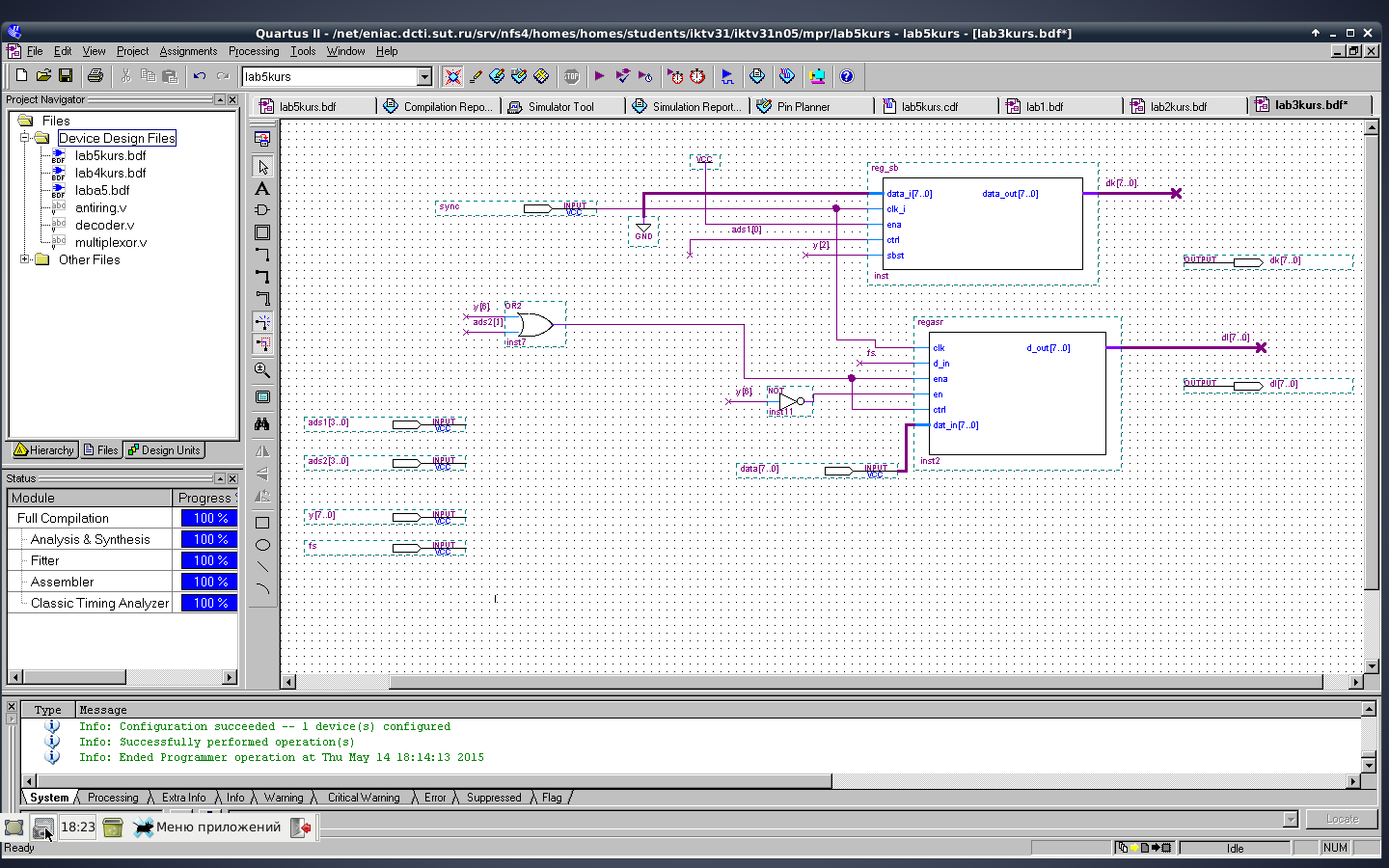

Схема устройства:

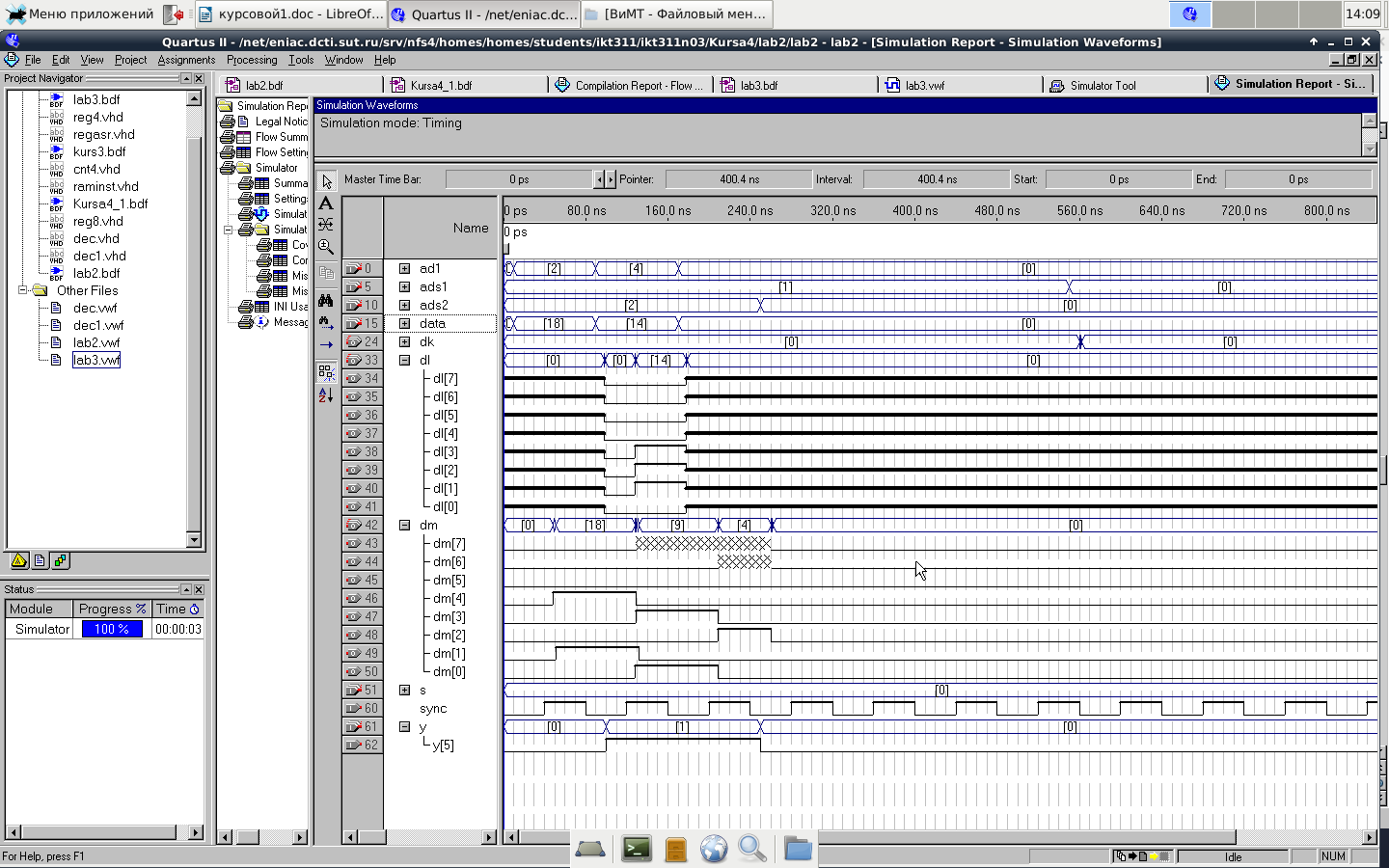

Временная диаграмма работы устройства:

Часть №4

Формирование блока арифметико-логического устройства (АЛУ).

Цель: получение представления о проведении арифметических операций в RISC-процессоре.

Постановка задачи: последний из синтезируемых блоков – АЛУ. В нашем случае АЛУ состоит только из 8-разрядного сумматора. Программа, описывающая такой сумматор – прогр.4.3. Она строится на основе прогр.4.1, описывающей одноразрядный сумматор без входа переноса для младшего разряда и прогр.4.2, описывающей одноразрядный сумматор, имеющий вход переноса для построения всех остальных разрядов. На входы сумматора могут поступать данные с выходов регистров соответствующего блока. Для выбора нужных операндов строим два блока из восьми мультиплексоров на четыре направления каждый. Для хранения бита переноса нужен триггер.

Программа 4.1

library ieee;

use ieee.std_logic_1164.all;

entity add1 is

port(a1,b1:in BIT;c1,s1:out BIT);

end add1;

architecture struct_1 of add1 is

begin

s1<= ((a1 and (not b1)) or ((not a1) and b1));

c1<= a1 and b1;

end struct_1;

Прогр.4.2

library ieee;

use ieee.std_logic_1164.all;

entity add11 is

port(a2,b2,c1:in BIT;c2,s2:out BIT);

end add11;

architecture struct_1 of add11 is

begin

s2<=(a2 xor b2) xor c1;

c2<= (a2 and b2) or ((a2 xor b2)and c1);

end struct_1;

Программа 4.3

library ieee;

use ieee.std_logic_1164.all;

port(a,b:in bit_vector(7 downto 0);

entity add8 is

s:out bit_vector(7 downto 0);

c : out bit);

end add8;

architecture structural of add8 is

component add1

port(a1,b1:in BIT;c1,s1:out BIT);

end component;

component add11

port (c1,a2,b2:in BIT; c2,s2:out BIT);

end component;

signal c_in: bit_vector(6 downto 0);

begin

p0: add1

port map(a1=>a(0),b1=>b(0),c1=>c_in(0),s1=>s(0));

p1: add11

port map(c1=>c_in(0),a2=>a(1),b2=>b(1),c2=>c_in(1),s2=>s(1));

p2: add11

port map(c1=>c_in(1),a2=>a(2),b2=>b(2),c2=>c_in(2),s2=>s(2));

p3: add11

port map(c1=>c_in(2),a2=>a(3),b2=>b(3),c2=>c_in(3),s2=>s(3));

p4: add11

port map(c1=>c_in(3),a2=>a(4),b2=>b(4),c2=>c_in(4),s2=>s(4));

p5: add11

port map(c1=>c_in(4),a2=>a(5),b2=>b(5),c2=>c_in(5),s2=>s(5));

p6: add11

port map(c1=>c_in(5),a2=>a(6),b2=>b(6),c2=>c_in(6),s2=>s(6));

p7: add11

port map(c1=>c_in(6),a2=>a(7),b2=>b(7),c2=>c,s2=>s(7));

end structural;

Программа 4.4.

library ieee;

use ieee.std_logic_1164.all;

entity ms4e is

port(

adr_i: in std_logic_vector(1 downto 0);

k_i: in std_logic_vector(7 downto 0);

l_i: in std_logic_vector(7 downto 0);

m_i: in std_logic_vector(7 downto 0);

n_i: in std_logic_vector(7 downto 0);

en: in std_logic;

data_out: out std_logic_vector(7 downto 0)

);

end ms4e;

architecture BBB of ms4e is

begin

process (adr_i)

begin

if (en=’0’) then data_out<=”00000000”;

elsif (en=’1’) then

case adr_i is

when “00”=>data_out<=k_i;

when “01”=>data_out<=l_i;

when “10”=>data_out<=m_i;

when “11”=>data_out<=n_i;

end case;

end if;

end process;

end;

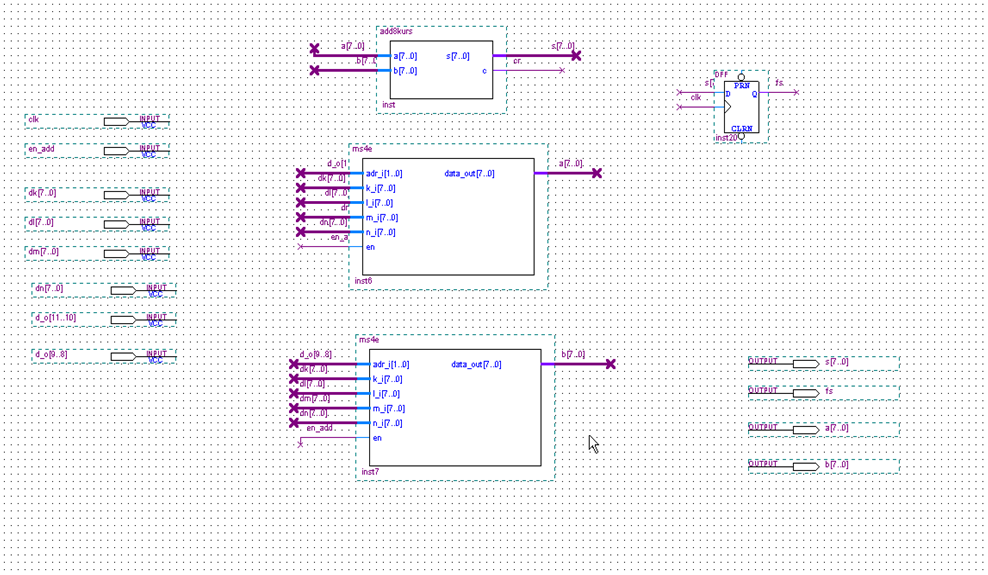

Схема устройства:

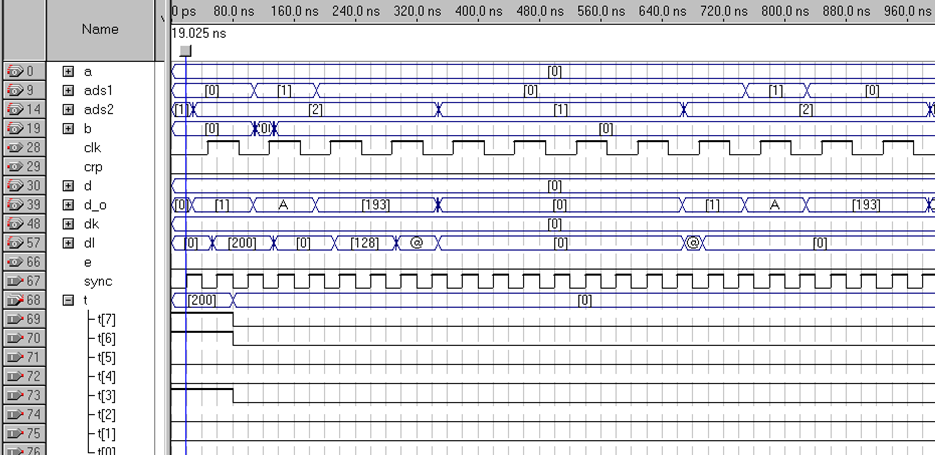

Временная диаграмма работы устройства:

Часть №5

|

из

5.00

|

Обсуждение в статье: Формирование блоков регистров |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы