|

Главная |

Последовательный интерфейс процессора

|

из

5.00

|

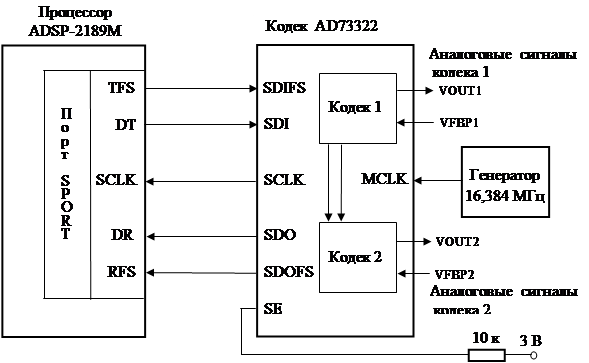

Рассмотрим пример подключения кодека к порту SPORT0. Во время приема и передачи информации последовательным кодом процессор может выполнять программу, не связанную с работой порта по приему и передаче каждого бита. В рассмотренном режиме работы на рис. 15 предполагается, что процессор должен не пропустить только те моменты времени, когда в регистр передатчика ТХ порта SPORT нужно записать передаваемое 32-разрядное слово и прочитать из регистра приемника RX принятое 32-разрядное слово. Преобразование параллельного кода в последовательный при передаче и последовательного кода в параллельный при приеме выполняет аппаратно встроенный порт SPORT.

К программно доступным регистрам RX0, TX0 порта SPORT0 и RX1, TX1 порта SPORT1 можно обратиться в любой момент времени. Для чтения принятого 16-разрядного слова RX0 и записи 16-разрядного слова в передатчик TX0 порта SPORT0 достаточно записать две команды

АХ0 = RX0;

TX0 = AY0.

Первая ассемблерная команда записывает в регистр АХ0 число, принятое последовательным портом из кодека, вторая – записывает в передатчик число из регистра AY0, которое будет передано портом SPORT0 в кодек. Так как последовательные порты управляются контроллером прерываний, то для обеспечения максимальной производительности процессора указанные ассемблерные команды должны выполняться в подпрограмме обработки прерываний. Использование контроллера прерываний позволяет вводить данные из АЦП в память процессора и выводить из памяти в ЦАП с постоянным шагом во времени TS.

Программирование последовательного порта можно разбить на две части. Первый программный блок задает режим работы порта и его параметры, выполняется обычно однократно в начале основной программы при инициализации устройств, подключенных к процессору (табл. 9). В некоторых случаях инициализация может проводиться повторно для изменения отдельных параметров. Вторая часть содержит подпрограмму обработки прерываний, выполняемую циклически с частотой дискретизации сигналов FS. Кроме выполнения команд ввода-вывода для обмена данными с кодеком она содержит программный код обработки поступающей информации в реальном времени. Например, расчет выходного сигнала цифрового фильтра низкой частоты n-го порядка.

Таблица 9. Регистры конфигурации портов SPORT

| Адрес | Назначение регистра |

| 0x3FFA | Приемник RX0 порта SPORT0 , биты 31-16 |

| 0x3FF9 | Приемник RX0 порта SPORT0 , биты 15-10 |

| 0x3FF8 | Передатчик TX0 порта SPORT0 , биты 31-16 |

| 0x3FF7 | Передатчик TX0 порта SPORT0 , биты 15-10 |

| 0x3FF6 | Регистр управления порта SPORT0: источник битовой синхронизации, кадровая синхронизация, компандирование, длина слова |

| 0x3FF5 | Делитель битовой частоты SCLKDIV порта SPORT0 |

| 0x3FF4 | Делитель кадровой частоты RFSDIV порта SPORT0 |

| 0x3FF3 | Регистр управления автобуферизацией порта SPORT0 |

| 0x3FF2 | Регистр управления порта SPORT1: выходной сигнал флага, источник битовой синхронизации, кадровая синхронизация, компандирование, длина слова |

| 0x3FF1 | Делитель битовой частоты SCLKDIV порта SPORT1 |

| 0x3FF0 | Делитель кадровой частоты RFSDIV порта SPORT1 |

| 0x3FEF | Регистр управления автобуферизацией порта SPORT1 |

На рис. 17 приведен формат регистра управления 0x3FF6 порта SPORT0.

Разряды 8 и 9 регистра зависят от схемы подключения кодека к процессору и выбранного источника синхронизации. В схеме на рис. 14 кадровую синхронизацию выполняет выходной сигнал кодека SDOFS, который сформирован делением частоты опорного внешнего генератора 16,384 МГц. Если в качестве источника синхронизации выбран внешний генератор 16,384 МГц, то сигнал RFS процессора должен быть входом, для чего в разряд 8 регистра управления 0x3FF6 необходимо записать ноль при инициализации порта SPORT0.

Рис. 17. Разряды регистров управления 0x3FF6 порта SPORT0 и 0x3FF2 порта SPORT1

Сигнал процессора TFS в рассмотренной схеме при установленной перемычке может быть только входом. Поэтому в разряд 9 регистра управления 0x3FF6 необходимо также записать ноль. Если в схеме перемычку между выводами RFS и TFS убрать (рис. 18), то TFS необходимо запрограммировать на вывод, записав единицу в разряд 9. В этом случае сигнал кадровой синхронизации ТFS должен сформировать последовательный порт процессора. Кадровая синхронизация кодека SDOFS тактирует только приемник порта SPORT. Начало приема и передачи могут не совпадать. Задержка между передачей и приемом зависит от количества команд подпрограммы обработки прерывания. Последний вариант синхронизации более удобен для смешанного режима работы, когда процессор вначале записывает управляющие слова для инициализации кодека, а затем переводит кодек в режим приема и передачи данных. При инициализации кодека передаваемые процессором данные не должны поступать на вход ЦАП, принимаемые данные не должны восприниматься процессором как информация от АЦП.

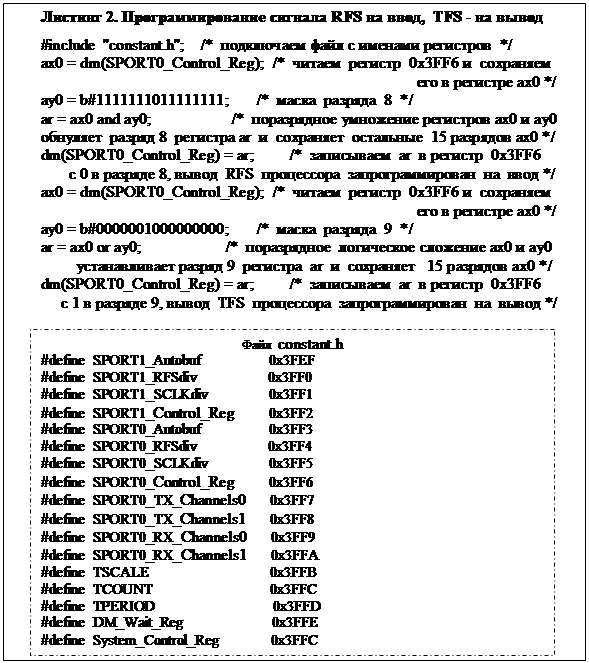

Пример программирования выводов процессора RFS и TFS при инициализации порта SPORT0 для смешанного режима работы кодека приведен в листинге 2.

|

Рис. 18. Внешняя синхронизация приемника порта SPORT

|

8.

При записи числа в регистр управления 0x3FF6 порта SPORT0 используется его имя SPORT0_Control_Reg, объявленное в файле constant.h. Инициализация последовательного порта SPORT0 в приведенной программе выполняется отдельной командой для каждого разряда. Если в выбранный разряд необходимо записать 0, то содержимое регистра умножается на константу с нулем в этом же разряде и единицами во всех остальных разрядах. Это позволяет обнулить только один из 16 разрядов, сохранив предыдущие значения в 15 разрядах, находившихся в регистре управления до умножения на константу (маску). Поразрядное умножение двух чисел с помощью команды ''and'' определяет результат умножения в каждом разряде 0 × Х = 0, 1 × Х = Х, где Х обозначает произвольное состояние бита (0 или 1). Аналогично для записи единицы в один из 16 разрядов с сохранением остальных 15 разрядов используется поразрядное логическое сложение. Поразрядное логическое сложение двух чисел с помощью команды ''or'' определяет результат умножения в каждом разряде 0 + Х = Х, 1 + Х = 1. Единица должна быть в том же разряде константы, в котором необходимо записать единицу в регистр. Остальные 15 разрядов константы равны нулю.

|

из

5.00

|

Обсуждение в статье: Последовательный интерфейс процессора |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы