|

Главная |

Архитектура процессора ADSP-2189M

|

из

5.00

|

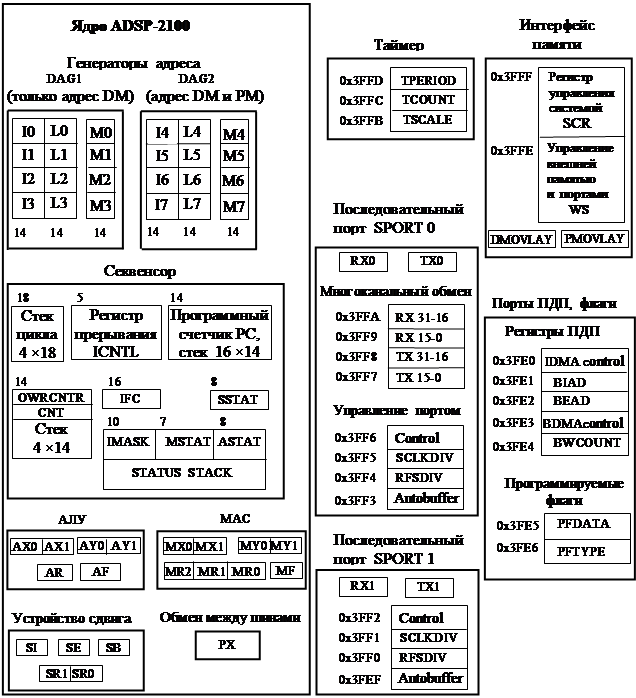

Однокристальный процессор ADSP-2189M в 100- или 144-выводном корпусе использует модифицированную гарвардскую архитектуру, которая предполагает раздельные адресные пространства памяти программы и памяти данных, позволяет хранить данные в памяти программы (рис. 6). Процессор содержит ядро 2100 (три вычислительных блока, генераторы адреса и программный секвенсор), два последовательных порта, 16-разрядный внутренний порт прямого доступа DMA, 8-разрядный порт DMA, порты ввода-вывода внешних сигналов, программируемый таймер, систему обработки прерываний, встроенную статическую память программ и данных.

Все устройства микропроцессора – 16-разрядные и оперируют с данными в формате с фиксированной запятой. Числа представляются либо как беззнаковые, либо в дополнительном коде. 14-разрядная шина адреса памяти программ позволяет получить прямой доступ к 16К слов (24-битовых) памяти программ. Шина данных памяти данных является 16-разрядной. На кристалле процессора расположено 32К слов памяти программ и 48К слов (16-битовых) памяти данных.

Рис. 6. Блок-схема ADSP-2189M

При тактовой частоте 75МГц производительность процессора составляет 75 миллионов команд в секунду (75 MIPS), время командного цикла – 13.3 нс.

За один цикл ADSP-2189M может сгенерировать адрес следующей команды программы, выбрать следующую команду, выполнить два обмена данных, обновить два указателя адреса, выполнить вычислительную операцию, передать или принять данные от двух последовательных портов и обновить регистр таймера. С точки зрения программиста сигнальный процессор представляет собор набор программно-доступных регистров (рис.7).

Адресные генераторы (DAG) вычисляют адреса при пересылке данных из памяти в регистры и обратно. Генератор DAG1 может выполнять адресацию только в памяти данных, DAG2 – в памяти данных и в памяти программ.

Секвенсор управляет ходом выполнения программы. Регистр команд

секвенсора хранит информацию о выполняемой в данный момент времени команде. Команды загружаются из памяти программ в регистр команд в одном цикле процессора и выполняются в следующем цикле, когда одновременно с

|

РM – память программ (program memory), DM – память данных (data memory)

Рис. 7. Программная модель процессора ADSP-2189M

выполнением выбирается следующая команда программы. Регистр команд образует одноуровневый конвейер в потоке выполняемых команд. Секвенсор позволяет организовать цикл в программе без использования команд условного перехода. Условие завершения цикла процессор выполняет автоматически, контролируя системный счетчик циклов программы.

Устройство также способно с минимальной задержкой реагировать на прерывания, поступающие от контроллера прерываний. Появление прерывания вызывает временную остановку основной программы и переход к ячейке памяти, где хранится подпрограмма обработки прерывания. Для этих целей в таблице векторов прерываний зарезервировано четыре ячейки памяти на одно прерывание. Прерывания могут вызываться внешними сигналами, поступающими на процессор, или циклически через равные интервалы времени, подсчитываемые таймером.

Арифметико-логическое устройство (АЛУ) поддерживает 32-разрядные арифметические действия. АЛУ обеспечивает стандартный набор арифметических и логических функций: сложение, вычитание, инкремент, декремент, получение абсолютного значения, смену арифметического знака, логическое И, ИЛИ, исключающее ИЛИ и инверсию. Поддерживаются примитивы деления.

Умножитель-накопитель МАС выполняет умножение со сложением или умножение с вычитанием за один цикл. Пример такой ассемблерной команды рассмотрен ранее. Для защиты от переполнения устройство содержит 40-битный аккумулятор. Дополнительные 8 разрядов допускают возникновение 256 переполнений, прежде чем произойдет потеря данных. Если после окончания выполнения программы установлен флаг MV, то это означает, что регистр результата содержит слово, длина которого больше 32 разрядов.

Устройство сдвига производит операции логического и арифметического сдвига, нормализации (преобразование из формата с фиксированной запятой в формат с плавающей запятой), денормализации (преобразование из формата с плавающей запятой в формат с фиксированной запятой), вычисления экспоненты.

Два последовательных порта SPORT0 и SPORT1 используются для обмена данными с последовательными устройствами. Обычно один из портов подключается через СОМ-порт к компьютеру, другой – с последовательным кодеком (АЦП и ЦАП в одной микросхеме). Оба порта поддерживают обмен данными в последовательном коде словами длиной от 3 до 16 бит и обеспечивают логарифмическое сжатие данных по А-закону или μ-закону в соответствии с рекомендацией G.711.

Программируемый таймер генерирует периодические прерывания с помощью 16-битного счетчика TCOUNT. Содержимое счетчика уменьшается на единицу в каждом цикле процессора. Когда счетчик обнуляется, генерируется прерывание и в него записывается начальное значение из 16-разрядного регистра TPERIOD.

Микропроцессор содержит внутренний порт прямого доступа к памяти (ПДП) и байтовый порт ПДП, которые обеспечивают быстрый обмен с памятью. Внутренний порт ПДП поддерживает обмен с памятью программ, байтовый порт позволяет записывать и читать как команды, так и данные. Порт интерфейса с хост-процессором обеспечивает подключение процессоров данного семейства или других микропроцессоров без дополнительных интерфейсных схем.

Напряжение питания ядра процессора 2.5В, напряжение на внешних выводах портов ввода-вывода должно быть равным 2.5В или 3.3В. Мощность, потребляемая от источника питания, достигает максимума 90мВТ при выполнении процессором программы из встроенной памяти и не превышает

1 мВТ в режиме пониженного энергопотребления. Переход в «спящий» режим может осуществляться аппаратно или программно.

Структура процессора ориентирована на выполнение наиболее часто встречающихся операций при цифровой обработке за один цикл. Типовой операцией различных алгоритмов ЦПОС является суммирование произведений. Для этого процессору необходимо извлечь из памяти два операнда (например, коэффициент фильтра и один отсчет массива данных), перемножить их и суммировать результат с предыдущим произведением.

При обращении к отдельному устройству в программах на языке ассемблера используется одна или несколько переменных, хранящихся в регистрах

процессора. Имя регистра определяет не только конкретное устройство, но и закрепленную за ним функцию. В генераторах адреса DAG1 и DAG2 четыре индексных регистра I содержат адреса ячеек памяти, регистры М – шаг увеличения адреса, L – длину циклического буфера.

Данные, поступающие на входы АЛУ и МАС для выполнения арифметических или логических операций, должны храниться в одном или нескольких регистрах АХ0, АХ1, МХ0, МХ1, АY0, АY1, МY0, МY1. Результат выполненной операции хранится в регистрах AR, AF, MR, MF. Признаки результата операции, выполненной АЛУ и МАС, процессор автоматически заносит в регистр ASTAT (рис. 8). Процессор установит бит AZ (AZ=1), если результат нулевой, и сбросит бит (AZ=0) в противном случае. Бит AN=1, если после выполнения текущей команды получено отрицательное число. Бит MV устанавливается в том случае, если произошло переполнение 40-разрядного числа МАС.

Таблица 2. Переменные регистра ASTAT

|

Регистр режима работы MSTAT содержит 4 бита управления переключением регистров вычислительных блоков, бит-реверсивной адресацией генератора DAG1 и насыщением АЛУ. Остальные 3 бита управляют размещением результата в блоке МАС, таймером и запуском процессора.

Стек счетчика COUNT содержит переменную CNTR для организации цикла без указания в программе условия его завершения. Необходимо лишь задать начальное значение счетчика CNTR, например, CNTR=10. Каждый цикл программы автоматически уменьшает содержимое счетчика на единицу. После 10 циклов, когда счетчик обнулится, процессор продолжит линейное выполнение программы.

В систему команд процессора входят многофункциональные команды, использующие параллельное выполнение действий различными блоками. Примером такого типа команд является следующая инструкция, которая выполняется за один цикл

MR=MR+MX0*MY0(SS), MX0=DM(I0,M0), MY0=PM(I4,M5);

Первая часть команды (до первой запятой) помещает в регистр результата

MR блока МАС сумму предыдущего значения регистра и произведение текущих значений входных регистров Х и Y (МХ0 и МY0), данные в которых воспринимаются процессором как числа со знаком SS, где S – первая буква слова sign (знак). Во второй и третьей части команды процессор читает из памяти два новых операнда и запоминает их в регистрах МХ0 и МY0. В регистр МХ0 заносится значение из ячейки памяти данных (DM) с номером I0, в регистр МY0 – из ячейки памяти программ (РМ) с номером I4. После записи

чисел в регистры значение переменной I0 увеличивается на М0, а I4 соответственно – на М5.

|

из

5.00

|

Обсуждение в статье: Архитектура процессора ADSP-2189M |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы