|

Главная |

Последовательный порт ввода-вывода UART

|

из

5.00

|

Порт UART входит в состав периферийных устройств микроконтроллеров типа 2313, 4433,8515, 8535, ml63 и m10

Порт UART содержит передатчик, приемник, тактовый генератор и аппаратуру управления передачей и приемом. Передатчик получает байт из шины данных микроконтроллера и формирует и выдает последовательность битов (кадр.), которая кроме битов, составляющих байт (DO, D1,. ., D7), содержит стартовый бит (start), имеющий нулевое значение, и столовый бит (stop), имеющий единичное значение. Между старшим битом байта (D7) п стоповым битом может помещаться дополнительный бит (СВ).

Приемник выделяет стартовый бит, принимает кадр, формат которого (число битов) задан, расформировывает принятый кадр и подготавливает байт для выдачи в шипу данных микроконтроллера.

Тактовый генератор формирует сигнал, определяющий скорость передачи и приема битов и позволяющий выделять биты при приеме кадра.

В состав порта входят регистр данных передатчика UDR (Т), регистр Данных приемника UDR (R), регистр управления UCR или UCSRB (№ $0А), регистр состояния USR пли UCSRA (№ $0В), регистр задания скорости передачи/приема UBRR (№ $09) и другие элементы. Регистры Данных передатчика и приемника имеют один номер - $0С. При обращении для записи выбирается регистр UDR (T), при обращении Для чтения - регистр UDR (R).

Передатчик готов к работе при установке в единичное состояние разряда TXEN регистра управления UCR. При этом выход передатчика TXD подключается к выводу определенного порта микроконтроллера. Передача кадра начинается при загрузке байта в регистр UDR (T). Загрузку можно выполнять при единичном состоянии разряда UDRE регистра состояния USR. При сбросе микроконтроллера в исходное состояние устанавливается UDRE = 1.

Загруженный байт передается в сдвигающий регистр передатчика TSR и происходит выдача кадра на выход микроконтроллера TXD.

При нулевом состоянии разряда CHR9 регистра UCR формируется кадр из десяти битов. При CHR9 = 1 кадр содержит одиннадцать битов. Значение дополнительного бита в этом случае должно быть указано в разряде ТХВ8 регистра UCR.

Первый байт при загрузке немедленно передается в регистр TSR и разряд UDRE регистра USR сохраняет единичное состояние, что позволяет сразу после загрузки первого байта загружать в регистр UDR (T) второй байт. Второй и последующие байты сохраняются в регистре UDR (Т) до завершения выдачи из регистра TSR предыдущего кадра. При этом разряд UDRE регистра USR находится в нулевом состоянии и загрузка очередного байта в регистр UDR (T) запрещена.

При завершении выдачи кадра из регистра TSR и отсутствии очередного байта в регистре UDR (T) устанавливается в единичное состояние разряд ТХС регистра USR и при единичном состоянии разряда TXCIE регистра UCR в блок прерываний поступает запрос прерывания UART ТХС.

Разряд ТХС регистра USR сбрасывается в нулевое состояние аппаратно при переходе микроконтроллера к выполнению соответствующей прерывающей программы или программно при выполнении команды установка бита в единичное состояние.

При единичном состоянии разряда UDRE регистра USR и единичном состоянии разряда UDRIE регистра UCR в блок прерываний поступает запрос прерывания UART DRE. Разряд UDRE сбрасывается в нулевое состояние при записи байта в регистр UDR (T). Прерывающая программа, выполняемая по запросу прерывания UART DRE, должна содержать команду записи в регистр UDR (T) для прекращения действия этого запроса прерывания.

Приемник готов к работе при установке в единичное состояние разряда RXEN регистра UCR. При этом вход приемника RXD подключается к выводу определенного порта микроконтроллера. При обнаружении на входе RXD отрицательного фронта сигнала, приемник определяет уровень сигнала в момент времени, отстоящий от фронта на половину интервала, отводимого на передачу бита при заданной скорости передачи. При обнаружении нулевого уровня принимается решение о приеме стартового бита и далее определяются уровни сигнала в моменты времени, отстоящие друг от друга на интервал, отводимый на передачу бита. Получаемая последовательность значений вводится в сдвигающий регистр приемника RSR. Если принимается кадр из одиннадцати битов (CHR9 = 1), дополнительный бит принимается в Разряд RXB8 регистра UCR. Если на месте ожидаемого стопового бита сигнал имеет пулевое значение, устанавливается в единичное состояние Разряд FE регистра USR (ошибка формата). Разряд FE сбрасывается в нулевое состояние при появлении единичного значения стопового бита.

Принятый байт из регистра RSR переписывается в регистр UDR (R). При этом устанавливается в единичное состояние разряд RXC регистра USR и при единичном состоянии разряда RXCIE регистра UCR в блок прерываний поступает запрос прерывания UART RXC.

Разряд RXC регистра USR сбрасывается в нулевое состояние при чтении регистра UDR (R). Прерывающая программа, выполняемая по запросу прерывания UART RXC, должна содержать команду чтения из Регистра UDR для прекращения действия этого запроса. Если при завершении приема кадра принятый ранее байт не считан из регистра UDR (R), устанавливается в единичное состояние разряд OR регистра USR (состояние переполнения). Разряд OR сбрасывается в нулевое состояние при передаче байта из регистра RSR в регистр UDR (R).

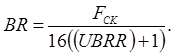

Тактовый генератор BRG формирует сигнал, определяющий скорость передачи н приема битов и дополнительный сигнал, обеспечивающий выделение битов при приеме кадра. Скорость передачи и приема BR, бит/с, зависит от частоты тактового сигнала микроконтроллера FCK и числа (UBRR), двоичный код которого записан в регистре UBRR, и определяется по формуле:

Для работы со стандартными скоростями приема-передачи (4800, 9600,14400, 19200, 28800, 38400, 57600, 76800 и 115200 бит/с) используются кварцевые резонаторы со специальными значениями резонансной частоты (3, 6864; 7,3728; 11,059 Мгц).

В порте UART микроконтроллеров типа 4433 и ml63 регистр управления вместо имени UCR имеет имя UCSRB, а регистр состояния вместо имени USR - имя UCSRA. Регистр UCSRA имеет дополнительный разряд МРСМ. При единичном состоянии разряда приемник принимает кадры, у которых дополнительный бит (СВ) имеет единичное значение и игнорирует кадры при СВ = 0. При нулевом состоянии разряда МРСМ принимаются кадры с любым значением дополнительного бита. Наличие разряда МРСМ позволяет организовать простейшую локальную сеть (мультипроцессорную систему), в которой имеется один ведущий контроллер и несколько ведомых. Каждому ведомому контроллеру присваивается определенный номер.

В исходном состоянии у всех ведомых контроллеров МРСМ = 1.

Ведущий контроллер передает кадр, в котором СВ = 1, а байт является номером ведомого котроллера, который должен принять данные из ведущего.

Все ведомые контроллеры принимают кадр. Контроллер, опознавший свой номер, сбрасывает разряд МРСМ в нулевое состояние. Далее ведущий контроллер передает кадры, в которых СВ = 0, а байты представляют собой данные для выбранного ведомого контроллера. Эти кадры принимаются только ведомым контроллером, у которого МРСМ = 0. При обнаружении кадра с СВ = 1 выбранный контроллер переводит разряд МРСМ в единичное состояние и переходит в исходное состояние.

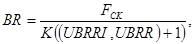

В микроконтроллере типа ml63, кроме того, регистр UCSRA имеет дополнительный разряд U2X, а для задания скорости передачи используются два регистра - регистр UBRR (№$09) для задания младших восьми разрядов кода числа и регистр UBRRHI (№$20) для задания старших четырех разрядов кода числа. Скорость передачи определяется по формуле

где К = 16 при U2X = 0, К = 8 при U2X = 1.

В табл.5. указаны выводы портов микроконтроллеров, используемые в качестве входа приемника (RXD) и выхода передатчика (TXD) у микроконтроллеров разных типов.

Таблица 5

| Вывод | Тип | мк | ||||

| порта UART | 2313 | 4433 | 8515 | 8535 | m163 | m10З |

| RXD TXD | PD0 PD1 | PD0 PD1 | PD0 PD1 | PD0 PD1 | PD0 PD1 | РЕО РЕ1 |

|

из

5.00

|

Обсуждение в статье: Последовательный порт ввода-вывода UART |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы