|

Главная |

Конфигурирование через интерфейс JTAG

|

из

5.00

|

Интерфейс JTAG был разработан группой специалистов по проблемам тестирования электронных компонентов (Joini Action Group). Oн был зарегистрирован в качестве промышленного стандарта IEEE Std 1149.1-1990 (IEEE Standard Test Access Port and Boundary-Scan Architecture). Он может быть использован для следующих целей:

· тестирования печатных плат

· конфигурирования (программирования) кристалла

· внутрисхемной отладки

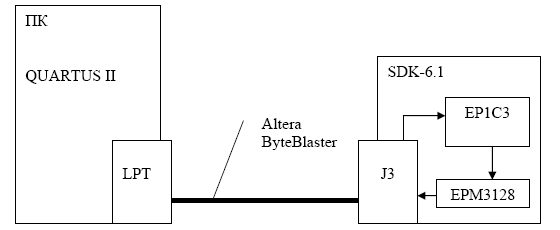

Применительно к лабораторному стенду режим конфигурирования через интерфейс граничного сканирования JTAG используется в процессе разработки и отладки учебных или прикладных проектов. Данный режим позволяет: конфигурировать вспомогательную ПЛИС EPM3128 (возможно только в режиме конфигурации через JTAG) и основную ПЛИС EP1C3, выполнять внутрисхемную отладку проекта, используя встроенные средства пакета проектирования Altera Quartus II. Конфигурационные файлы для основной ПЛИС EP1C3 при таком режиме работы не сохраняются в энергонезависимой памяти стенда и будут утеряны при отключении питания или рестарте системы. Еще одним недостатком данного способа конфигурирования ПЛИС можно считать потенциально опасное подключение стенда к ПК.

Рис. 32 Подключение SDK-6.1 к ПК по интерфейсу JTAG

Порядок конфигурирования ПЛИС с помощью JTAG:

1. Проверьте, что на инструментальном компьютере установлен и функционирует

драйвер адаптера интерфейса JTAG ByteBlaster. Для этого запустите программу его инициализации bblpt.exe /i из подкаталога C:\ Programm Files\altera\quartus41\drivers\i386\.

2. Если SDK-6.1 уже подключен к ПК, перейдите к п.4.

3. Отключите питание SDK-6.1: адаптер питания из розетки или разъем кабеля адаптера от стенда.

4. Подключите SDK-6.1 к параллельному порту LPT компьютера с помощью адаптера

ByteBlaster (рис. 30).

5. Подключите питание к SDK-6.1.

6. Создайте и скомпилируйте проект, предназначенный для основной ПЛИС EP1C3

стенда SDK-6.1, в инструментальной среде Altera Quartus II. В результате успешной компиляции должен быть создан конфигурационный файл с расширением .sof (SRAM Object File – файл для конфигурирования ПЛИС на базе статической памяти, к которым, в частности, относятся микросхемы семейства Cyclon).

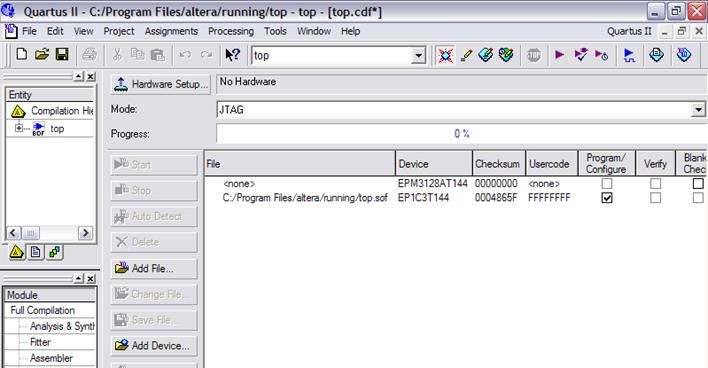

7. Запустите встроенный в Quartus II программатор для этого щелкните по пиктограмме программатора на горизонтальной панели инструментов или выберите пункт меню Tools-> Programmer (Рис.33).

Настройте цепочку JTAG устройств. Первым устройством обязательно должно быть указано устройство EPM3128AT100 (кнопка - Add Device – Добавить Устройство), вторым - EP1С3T144. Для основной ПЛИС EP1С3 укажите SOF файл для программирования, установите флажок в колонке Program/Configure.

Для вспомогательной ПЛИС EPM3128 программируемый файл не указывать (кроме случаев обновления системной конфигурации вспомогательной ПЛИС), не устанавливать флажки ни в одной из колонок (рис. 33).

Рис. 33 Окно диалога настройки цепочки JTAG устройств

8. Нажмите кнопку RESET на стенде. Должен загореться светодиод «CONFIG».

9. Для запуска процесса программирования нажмите кнопку «Start».

10. В случае успешного окончания программирования линейка «Progress» дойдет до 100%, после чего загруженная конфигурация активизируется и погаснет светодиод «CONFIG».

11. Если программирование невозможно, то процесс автоматически прервется и в окне системных сообщений Quartus II выведется надпись с описанием причины. Например, «Error: Can't access JTAG chain» означает, что адаптер ByteBlaster не подключен к ПК или стенду, или к стенду не подключено питание.

12. Перезагрузка конфигурации может быть выполнена выполнением только пп. 8 и 9,

без отключения питания и реинициализации системы.

В случае, если есть подозрения на неисправность стенда, можно попытаться локализовать неполадку при помощи встроенной программы тестирования. Ниже описываются функции этой тестовой программы.

ЛИТЕРАТУРА

1. Грушвицкий Р.И., Мурсаев А.X. Угрюмов Е.П. Проектирование систем на микросхемах программируемой логики. — СПб.: БХВ-Петербург, 2002.

2. Угрюмов Е.П. Цифровая схемотехника. – СПб.: БХВ, 2000.

ПРИЛОЖЕНИЕ

Таблица распайки выводов и сигналов ПЛИС EP1C3T144-8 и элементов управления стендa

Табл. 1

| Название | Вывод ( Pin ) |

| Генератор тактовых импульсов( clk ) | Pin_93 |

| Осциллограф | |

| Channel A | Pin_1 |

| Channel В | Pin_3 |

| Движковые переключатели | |

| sw0 | Pin_112 |

| sw1 | Pin_120 |

| sw2 | Pin_113 |

| sw3 | Pin_121 |

| sw4 | Pin_114 |

| sw5 | Pin_122 |

| sw6 | Pin_119 |

| sw7 | Pin_123 |

| Светодиоды | |

| led0 | Pin_104 |

| led1 | Pin_105 |

| led2 | Pin_106 |

| led3 | Pin_107 |

| led4 | Pin_108 |

| led5 | Pin_109 |

| led6 | Pin_110 |

| led7 | Pin_111 |

| Кнопка «Control» | Pin_133 |

Все каналы дискретного ввода-вывода, выведенные на переднюю панель лабораторного макета, представлены в таблице 2.

Табл. 2

| № | «EXTERNAL PIO» | КАНАЛЫ ДИСКРЕТНОГО ВВОДА-ВЫВОДА |

| 1 | 2 | 3 |

| 1 | EXT_GND | Общий |

| 2 | EXT_GND | Общий |

| 3 | ELVDS0N | Дискретный порт ввода-вывода, инвертирующий вход порта LVDS4 ПЛИС |

| 4 | ELVDS1N | Дискретный порт ввода-вывода, инвертирующий вход порта LVDS3 ПЛИС |

| 5 | EXT_OE_G0 | Разрешение гальванически изолированных портов нн. 3-6 |

| 6 | EXT_GND | Общий |

| 7 | ELVDS2P | Дискретный порт ввода-вывода, неинвертирующий вход порта LVDS2 ПЛИС |

| 8 | ELVDS2N | Дискретный порт ввода-вывода, инвертирующий вход порта LVDS2 ПЛИС |

| 9 | EVREF0B1 | Дискретный порт ввода-вывода,опорное напряжение банка выводов №1 |

| 10 | EDPCLK1 | Дискретный порт ввода-вывода |

| 11 | EXT_OE_G1 | Разрешение гальванически изолированных портов нн. 9-12 |

| 12 | EXT_GND | Общий |

| 13 | ELVPIO0 | Дискретный порт ввода-вывода |

| 14 | ELVPIO1 | Дискретный порт ввода-вывода |

| 15 | EPLL1_OUTP | Дискретный порт ввода-вывода, выход PLL1 |

| 16 | EPLL1_OUTN | Дискретный порт ввода-вывода, выход PLL1 |

| 17 | EXT_OE_G2 | Разрешение гальванически изолированных портов нн. 15-18 |

| 18 | EXT_GND | Общий |

| 19 | EVREF1B1 | Дискретный порт ввода-вывода, опорное напряжение банка выводов №1 |

| 20 | EDPCLK0 | Дискретный порт ввода-вывода |

| 21 | EVREF2B1 | Дискретный порт ввода-вывода, опорное напряжение банка выводов №1 |

| 22 | ELVPIO2 | Дискретный порт ввода-вывода |

| 23 | EXT_OE_G3 | Разрешение гальванически изолированных портов нн. 21-24 |

| 24 | EXT_GND | Общий |

| 25 | ELVDS3P | Дискретный порт ввода-вывода, неинвертирующий вход порта LVDS1 ПЛИС |

| 26 | ELVDS3N | Дискретный порт ввода-вывода, неинвертирующий вход порта LVDS1 ПЛИС |

| 27 | ELVDS4P | Дискретный порт ввода-вывода, неинвертирующий вход порта LVDS0 ПЛИС |

| 28 | ELVDS4N | Дискретный порт ввода-вывода, неинвертирующий вход порта LVDS0 ПЛИС |

| 29 | EXT_OE_G4 | Разрешение гальванически изолированных портов нн. 27-30 |

| 30 | EXT_GND | Общий |

| 31 | ELVDSCLK1P | Дискретный порт ввода-вывода |

| 32 | ELVDSCLK1N | Дискретный порт ввода-вывода |

| 33 | EXT_OE_G5 | Разрешение гальванически изолированных портов нн. 33, 34, 37, 38 |

| 34 | EXT_GND | Общий |

| 35 | ELVDS5P | Дискретный порт ввода-вывода |

| 36 | ELVDS5N | Дискретный порт ввода-вывода |

| 37 | EXT_GND | Общий |

| 38 | EXT_GND | Общий |

(На разъемы осциллографа - Channel A и Channel В – выведены сигналы ELVDS0Р и ELVDS1Р соответственно).

Тест стенда SDK-6.1

Тестирование стенда может помочь в обнаружении и локализации возникших неполадок.

Перед проведением теста переведите все 8 движковых переключателей в нижнее положение и установите на переключателях «PAGE» номер 0001 (куда записана программа тестирования по умолчанию), нажмите «Reset» – стенд перейдет в тестовый режим. На ЖКИ будет выведена надпись «I’m sdk 6.1! Select test…» (Я - sdk 6.1! Выберите тест…). После этого выберите нужный тест путем перевода соответствующего переключателя в верхнее положение, при этом на ЖКИ внизу отобразится название теста. Для запуска теста нажмите кнопку «Control».

| № переключателя | Тест |

| sw0 | тест интерфейса RS-232 |

| sw2 | тест каналов ввода-вывода |

| sw4 | тест движковых переключателей и светодиодов |

| sw5 | тест памяти EEPROM |

1. Тест интерфейса RS-232:

Подключите стенд SDK-6.1 к компьютеру при помощи интерфейсного кабеля RS-232. Переведите стенд в тестовый режим и передвиньте переключатель sw0 в верхнее положение. Нажмите кнопку «Control» и запустите на ПК программу-терминал (например, Hyper Terminal, на скорости 115200 Кбит/с) и вводите с клавиатуры символы. Стенд принимает символ, отображает его и эхом отправляет обратно на компьютер. Если каждый введенный символ будет появляться в начале нижней строки ЖКИ и на экране терминала, значит интерфейс RS-232.функционирует корректно.

Для выхода из теста нажмите кнопку «Control» или передвиньте переключатель в нижнее положение.

2. Тест дискретных портов ввода-вывода:

Переведите стенд в тестовый режим и передвиньте переключатель sw2 в верхнее положение, нажмите кнопку «Control». На дискретные порты (каналы дискретного ввода-вывода – «External PIO») будет подаваться «бегущая единица» и «бегущий ноль» с частотой примерно 1 Гц.

Для выхода из теста нажмите кнопку «Control» или передвиньте переключатель в нижнее положение.

3. Тест движковых переключателей и светодиодов

Переведите стенд в тестовый режим и передвиньте переключатель sw4 в верхнее положение, нажмите кнопку «Control». На второй строке ЖКИ появится надпись – «Move switches» («Двигайте переключатели»). Теперь состояние восьми переключателей отображается на восемь светодиодов. Для выхода из теста нажмите кнопку «Control».

4. Тест памяти EEPROM

Переведите стенд в тестовый режим и передвиньте переключатель sw5 в верхнее положение, нажмите кнопку «Control». Если EEPROM работает правильно во второй строке появится надпись «ОК», в противном случае появится надпись «Failed». Для выхода из теста нажмите кнопку «Control».

|

из

5.00

|

Обсуждение в статье: Конфигурирование через интерфейс JTAG |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы