|

Главная |

Ввод и редактирование схемы

|

из

5.00

|

МИНИСТЕРСТВО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

ГОУ ВПО «ИЖЕВСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ

УНИВЕРСИТЕТ»

КАФЕДРА «ВЫЧИСЛИТЕЛЬНАЯ ТЕХНИКА»

МЕТОДИЧЕСКИЕ УКАЗАНИЯ К ВЫПОЛНЕНИЮ

ЛАБОРАТОРНЫХ РАБОТ

По дисциплинам «Основы комплексной автоматизации проектирования и производства СВТ»

«Организация ЭВМ и систем»

(Часть I )

Ижевск 2008

УДК 681.32.003

Составитель: канд.техн.наук, доцент кафедры «ВТ» К. Ю. Петухов.

Методические указания содержат основные сведения по работе в САПР QUARTUS II v. 4.1 WEB EDITION, а также приводится описание лабораторного стенда SDK 6.1, способы его подключения и конфигурирования.

Методические указания предназначены для выполнения лабораторных работ по дисциплинам «Основы комплексной автоматизации проектирования и производства средств вычислительной техники», «Организация ЭВМ и систем».

Ил. 33. Табл. 2. Библиограф.: 2 назв.

Рецензент: канд.техн.наук, доцент кафедры «РАДИОТЕХНИКА»

О. Б. Юминов

Ó Петухов К. Ю.

Содержание

ВВЕДЕНИЕ………………………………………………………………………………...............4

2. Процесс Создания проекта............................................................................. ....….. 5

Начало создания проекта.......................................................................................................5

Создание нового файла проекта...……………...……………………............….……….....7

Ввод и редактирование схемы……………………………..……………………….….…...7

Рисование цепи……………………………………………………………………….…..…10

Присвоение имени цепи.…………………………………………………………………....11

Задание констант «0» и «1»………………………………………………………………...11

Рисование шины……………………………………………………………….………........11

Формирование собственной библиотеки

МАКРОЭЛЕМЕНТОВ……………………………………………………………………...….... 11

Создание макроэлемента……………………………………………………………..….....13

Выбор подсхемы из библиотеки……………………………………………...……..…......13

Редактирование УГО макроэлемента……………………………………………..…….....13

4. КОМПИЛЯЦИЯ ПРОЕКТА…………………………………………………….……….…...14

5. моделирование схемы…………………………………………………18

6. ПОДГОТОВКА К РАЗМЕЩЕНИЮ СХЕМЫ……………………………….….….21

Редактор Назначений (Assignment Editor)………………………………………………...21

Поуровневый планировщик (FloorРlan Editor)……………………………………….…...23

7. реализация проекта на стенде SDK 6.1…..………………..….26

Особенности SDK-6.1…………………………………………………………….…….….26

Назначение SDK-6.1……………………………………………………………….…….....26

Подготовка схемы для размещения ее на кристалле…………………….…….………....27

Состав и параметры SDK-6.1………………………………………….………….………..28

Структурная схема SDK 6.1………………………………………………….………….....30

Конфигурирование ПЛИС…………………………………………….……….……….….29

8. ЛИТЕРАТУРА …………………………………………………………………………….....…34

ПРИЛОЖЕНИЕ……..………………………………………………….…….………..…….……35

Таблица распайки выводов и сигналов ПЛИС и элементов управления стендa…..…....35

Таблица каналов дискретного ввода-вывода…………………………………….………..36

Тест стенда SDK-6.1…………………………………………………...………….…….…..38

ВВЕДЕНИЕ

Основные возможности пакета Quartus II v.4.1:

· Различные способы ввода поведенческих , потоковых и структурных описаний проекта

· Интегрированные средства помощи для создания сложных проектов Mega Wizard & SOPC

· Система синтеза проекта

· Система размещения внутренних ресурсов и разводки ПЛИС

· Система моделирования проекта

· Система временного анализа и анализа потребляемой энергии проекта

· Система программирования ПЛИС

· Средства оптимизации быстродействия проекта - LogicLock

· Система интеграции с другими САПР

· Система проектирования блоков цифровой обработки сигналов (DSP)

· Поддержка использования IP-модулей (IP-Cores - от англ. Intellectual Property – интеллектуальная собственность)

· Поддержка ОС – Windows, Linux, Solaris, HPUS

Способы ввода описания проекта в рамках пакета Quartus II:

ü Текстовый ввод (VHDL, AHDL, VerilogHDL)

ü Посредством редактора памяти (Hex-, Mif-файлы)

ü Схемный ввод (Block Diagram File)

· Импорт проекта из других САПР в виде списка соединений (EDIF Netlist File)

· Использование мегафункций фирмы Altera и IP- модулей

· Сочетание различных способов

Текстовый ввод описания проекта:

· Возможности:

Ø Нумерация линий

Ø Использование заготовок языковых конструкций

Ø Отображение ключевых слов цветом

· Используемые языки

Ø AHDL (Altera Hardware Design Language) - <файл .tdf>

Ø VHDL (Very High Speed Integrated Circuit Hardware Description Language - язык описания аппаратных средств сверхбыстродействующих интегральных микросхем) - <файл .vhd>

Ø VerilogHDL (Verilog Hardware Description Language) - <файл .v>

Схемный ввод описания проекта:

При схемном вводе описания проекта могут использоваться:

· Простейшие логические элементы (примитивы)

· Параметризируемые модули

· Мегафункции компании Altera

· Ранее созданные компоненты

Вход в систему

Для входа в систему Quartus II v.4.1 Web Edition необходимо на рабочем столе Windows дважды щелкнуть мышью пиктограмму системы:

Начало создания проекта

Работа в системе начинается либо с выбора уже существующего проекта File -> Open Project … (Ctrl + J), либо с создания нового проекта File -> New … ( Ctrl + N ).

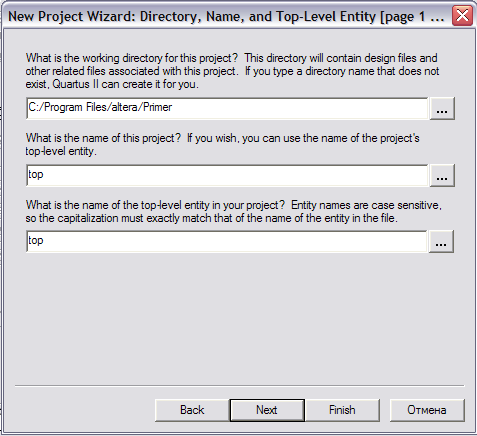

Создайте новый проект: выберите из меню File пункт New Project Wizard… - мастер создания новых проектов. В открывшемся окне нажмите кнопку Next и в окне для задания текущей директории проекта заполните все строки (в данном случае текущий проект будет назван top и будет создана директория по адресу C:/Program Files/altera/Primer- рис.1), нажмите кнопку Next несколько раз до тех пор, пока не дойдете до окна « Device Family».

Рис.1 Меню задания текущей директории проекта

В окне «Device Family» выберите семейство «Cyclone», а на вопрос: «Хотите ли вы выбрать конкретную модель?» ответьте утвердительно.

В следующем окне « Select a Target Device» значение Speed Grade выберите равным 8, а тип кристалла – EP 1 C 3 T 144 C 8 – это марка ПЛИС типа FPGA, использованной в лабораторном стенде.

Следующие файлы автоматически генерируются мастером New Project Wizard:

- Project Configuration File – файл хранит конфигурацию проекта, Имя, задаваемое по умолчанию – <имя_проекта.quartus>. Может редактироваться в текстовом редакторе.

- Project Settings File - файл с установками проекта - имя, задаваемое по умолчанию – <имя проекта.PSF >.

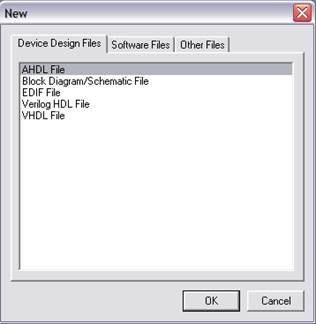

Создание нового файла проекта

После создания нового проекта произведем создание нового файла проекта. Меню File пункт New… в открывшемся диалоговом окне Рис.2 выберем тип создаваемого файла.

Рис.2 Меню выбора типа файла проекта

На закладке Device Design File можно выбрать:

- АHDL File – создать файл с описанием проекта на языке AHDL,

- Block Diagram/Schematic File – создать описание проекта в виде схемы,

- EDIF File – файл Electronic Design Interchange Format,

- VerilogHDL File – создать файл с описанием на языке VerilogHDL,

- VHDL File – создать файл с описанием на языке VHDL.

Создадим файл, содержащий описание схемы. Для этого выберем пункт Block Diagram/ Schematic File и нажмем OK. На рабочей панели Quartus II откроется окно с файлом Block1. bdf, в котором и создадим наш проект.

| ! |

Файлы графического редактора, созданные в Quartus II не могут быть открыты в системе Quartus 1.1 и более ранних версиях, включая САПР МАХ PLUS.

Ввод и редактирование схемы

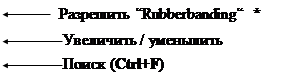

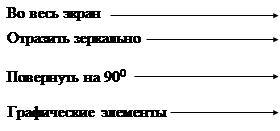

Графический (Схемный) редактор позволяет увеличивать или уменьшать масштаб изображения проекта на экране, выбирать размер шрифта, задавать стили линий, получать зеркальное отображение, поворачивать выделенные фрагменты на 90, 180 и 270 градусов, задавать размер и ориентацию текущего листа схемы (рис. 3).

При создании схемы могут использоваться:

– Простейшие логические элементы, триггеры, элементы ввода-вывода и другие элементы (primitives);

– Параметризируемые модули (мегафункции, megafunctions) - созданные фирмой Altera модули с нефиксированными параметрами;

– Ранее созданные (в текстовом или графическом редакторах) компоненты.

Для операций создания схемы применяется следующая панель инструментов (рис. 3).

|

|

|

|

|

|

|

| ||||||||

| ||||||||

|  | |||||||

| ||||||||

| ||||||||

| ||||||||

| ||||||||

Рис. 3 Свойства панели инструментов

* “ Rubberbanding“ или “ Rubber- banding“ – отангл. «эластичное соединение, соединение резиновой нитью» (в компьютерной графике) – при выбранной функции соединение (цепь, проводник или шина) останется неразрывно связанным с элементом при его перетаскивании в другое место.

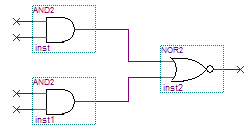

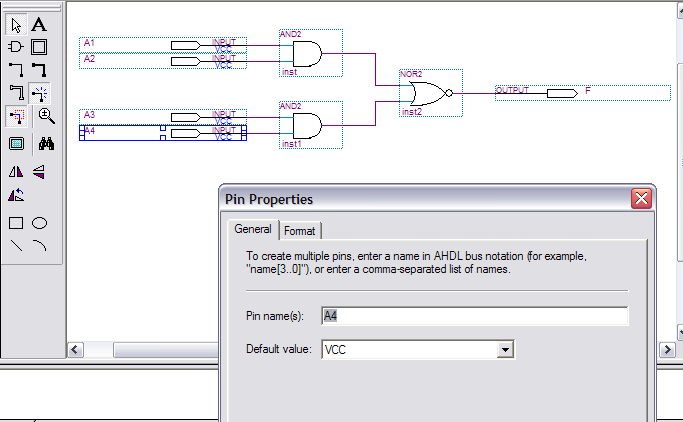

Рассмотрим процедуру создания простой схемы на примере. На рис. 4 приведена схема, которую следует ввести в графическом редакторе..

Рис. 4. Логическая схема

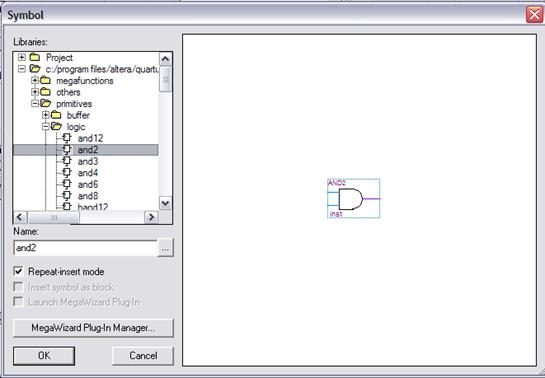

В схеме используются два элемента AND2 (2И) и один элемент NOR2 (2ИЛИ-НЕ). Эти элементы являются стандартными для системы Quartus II (т. н. «примитивы»), доступ к ним осуществляется как показано на рис. 5. Также можно просто ввести наименование элемента в поле «Name».

Рис. 5 Окно Symbol Tool

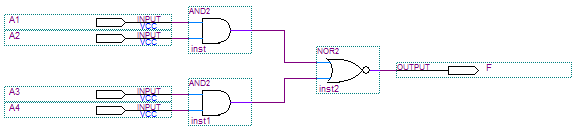

Подключите ко всем внешним контактам схемы входные и выходные элементы и дайте им названия (например, А1, А2, А3, А4 и F) (рис. 6);

Рис. 6. Логическая схема с подключенными внешними элементами

На рис. 7 показано как задать имя и тип элементов ввода-вывода в схемном редакторе.

|

|

Рис.7 Окно Pin Properties

Рисование цепи

Создание новой цепи осуществляется путем рисования ее фрагментов. Фрагмент цепи - это отрезок, соединяющий два объекта. Объектом является либо контакт (входной или выходной) элемента, либо цепь. Таким образом, фрагмент цепи соединяет контакт с контактом, контакт с цепью, цепь с контактом.

Рисование фрагмента цепи выполняется не прорисовкой конфигурации соединения, а только указанием соединяемых объектов, фрагмент цепи прорисовывается автоматически.

Можно начать рисование фрагмента цепи и на свободном поле, но закончить его вы должны на объекте.

Щелкните на панели инструментов (рис. 3)

1. кнопку «Рисование цепи» (Orthogonal Node Tool). Курсор примет вид перекрестия с маленькой пиктограммой цепи.

2. укажите щелчком левой клавиши мыши первый объект или желаемую точку на свободном поле (начало фрагмента цепи), затем вторым щелчком - второй объект (конец фрагмента цепи). После этого на экране появится автоматически прорисованный фрагмент цепи.

3. Повторите действия пункта 2 для рисования всей цепи.

Для перемещения цепи:

1. Переместите курсор на цепь и нажмите левую клавишу мыши.

2. Не отпуская клавишу, переместите цепь на требуемую позицию и отпустите клавишу мыши.

Для удаления цепи:

1. Щелкните мышью цепь, которую вы хотите удалить. Она будет выделена синим цветом. 2. Нажмите на клавиатуре клавишу Delete.

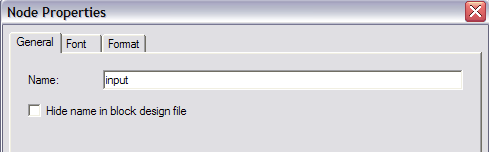

Присвоение имени цепи:

1. Щелкните правой кнопкой мыши на цепи, которой вы хотите присвоить имя. Откроется окно Node Properties (рис. 8).

2. Введите имя и нажмите кнопку OK.

|

Рис. 8 Окно Node Properties

Задание констант «0» и «1»

Для подачи на вход элемента постоянного сигнала «0» необходимо подсоединить к нему символ «земля». Для этого из библиотеки элементов (кнопка «Symbol» на рис. 3 или выберите команду Edit->Insert Symbol) необходимо извлечь элемент с именем GND.

Для подачи на вход элемента постоянного сигнала «1» необходимо подсоединить к нему символ «питание». Для этого из библиотеки элементов необходимо извлечь элемент с именем VCC. Элементы удобно выбирать, задавая их имя в поле «Name».

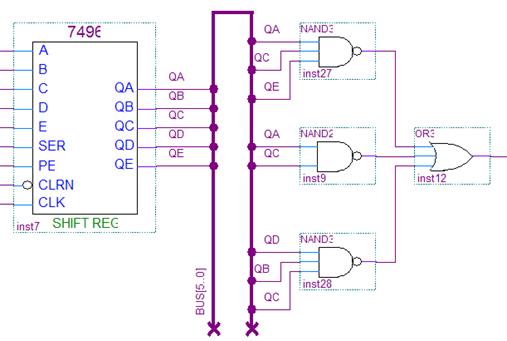

Рисование шины

Для более наглядного представления схемы и создания удобств ее рисования в системе предусмотрено использование шин.

Шина - это совокупность одиночных проводников, изображаемая на рисунке одной утолщенной линией.

Имя шины состоит из идентификатора и индексных пределов, заключенных в квадратные скобки: BUS_ NAME [ X.. Y], где X и Y - целые числа больше или равные 0.

Каждый проводник (сигнал), входящий в шину, получает имя шины и индекс: BUS_NAMEN, где n - индексное значение, заключенное между X и Y. Например, шина DATA[3:0] представляет набор дискретных сигналов:

DATA3, DATA2, DATA1, DATA0,

здесь DATA3 - старший бит шины,

а шина DATA[0:3] представляет тот же набор сигналов, но в обратном порядке:

DATA0, DATA1, DATA2, DATA3,

здесь старший бит шины - DATA0.

Это позволяет изменять соединения в схеме без удаления и перерисовки шинных соединений, для этого достаточно в имени шины поменять местами индексы X и Y.

| ! |

Имя шины не должно заканчиваться цифрой. Иначе могут быть непредвиденные подключения. Например, шины DATA1[0:7] и DATA[0:10] совместно используют сигнал DATA10, который является членом обеих шин.

Для примера приведем схему шинного соединения:

Рис. 9. Шина BUS[5..0] c подключенными контактами

Как видно из рис. 9 выходы QА … QЕ сдвигового регистра (Shift Register) получают имена QА … QЕ и выходят на некую комбинационную схему.

Следует заметить, что проектирование только в графическом редакторе является непрофессиональным. Связано это с тем, что зачастую синтезируемые логические функции достаточно громоздки, и рисовать полученную комбинационную схему весьма долго и трудоемко, к тому же теряется прозрачность решения. Создавать проект только в текстовом редакторе тоже не следует по той же самой причине - теряется наглядность. Поэтому разработка любого цифрового устройства должна носить «тексто-графический» характер

|

из

5.00

|

Обсуждение в статье: Ввод и редактирование схемы |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы