|

Главная |

Простейшие ЛЭ имеют следующие характеристики

|

из

5.00

|

1. Быстродействие – один из важнейших параметров, характеризуемый средним временем задержки распространения сигнала:

где  и

и  - задержка включения и выключения схемы.

- задержка включения и выключения схемы.

2. Нагрузочная способность – показывает, на сколько логических входов может быть одновременно нагружен выход данного ЛЭ без нарушения его работоспособности.

3. Коэффициент объединения по входу – определяет максимально возможное число входов ЛЭ. Увеличение входов ЛЭ расширяет их возможности за счет реализации функции от большего числа аргументов на одном элементе, однако при этом ухудшаются быстродействие и помехоустойчивость.

4. Помехоустойчивость – характеризует способность ЛЭ правильно функционировать при наличии помех. Она определяется максимально допустимым напряжением помехи, при котором обеспечивается работоспособность схемы.

5. Потребляемая мощность

где Ро и Рз – потребляемая мощность в открытом и закрытом состоянии.

ЛЭ характеризуются также количеством используемых источников питания и значениями напряжения питания, а также полярностью и уровнями водного и выходного сигналов.

Основные параметры ЛЭ.

1. Коэффициент разветвления по выходу Краз. Определяет число входов однотипных интегральных ЛЭ, которые одновременно могут быть подключены к выходу данного ЛЭ при сохранении его работоспособности в заданных условиях эксплуатации.

2. Коэффициент объединения по входу Коб. Определяет число входных сигналов ЛЭ, которые участвуют в формировании заданной логической функции.

3. Статические. К ним относятся: входная, определяющая зависимость входного тока от входного напряжения; выходная, задающая связь между выходными напряжением и током; передаточная,которая определяет зависимость выходного напряжения от входного.

4. Динамические. От них зависит быстродействие ЛЭ. К ним относятся: время перехода ЛЭ из состояния 1 в состояние 0 t1,0 , и перехода в обратное состояние t0,1, указанные временные интервалы измеряются на уровнях 0,1-0,9 от установившихся значений в цепочке из однотипных ЛЭ; время задержки включения  ; время задержки выключения

; время задержки выключения  ; время задержки распространения при включении

; время задержки распространения при включении  ; время задержки распространения при выключении

; время задержки распространения при выключении  .

.

5. Вид реализуемой логической функции. И, НЕ, ИЛИ, И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ.

ТРЕТИЙ ВОПРОС.

В настоящее время выпускается широкая номенклатура ИЛЭ в составе различных серий ИМС на основе биполярных и полевых транзисторов. При построении КЦУ выбор ИЛЭ осуществляется по их характеристикам и параметрам.

Наиболее широкое применение в микропроцессорной технике, используемой для построения устройств ЧПУ, нашли ИЛЭ построенные по технологиям ТТЛ, ТТЛШ, ЭСЛ и КМОП.

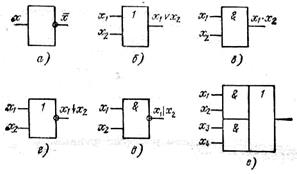

Условные графические обозначения интегральных логических

элементов на принципиальных электрических схемах.

а) элемент НЕ; б) элемент ИЛИ; в) элемент И; г) элемент ИЛИ-НЕ, стрелка Пирса, сложение с отрицанием; д) элемент И-НЕ, штрих Шеффера, умножение с отрицанием; е) элемент реализующий умножение и сложение нескольких аргументов.

Элементы, реализующие простейшие логические функции схематически изображают в виде прямоугольников, на поле которых изображается символ, обозначающих функцию, выполняемую данным элементом.

Входные переменные (х1, х2) принято изображать слева, а выходные (у) – справа. Считается, что передача информации происходит слева на право.

Если выходы одних элементов соединить с входами других, то получим схему, реализующую более сложную функцию.

Совокупность различных типов элементов, достаточных для воспроизведения любой логической функции, называют логическим базисом.

Логическим базисом являются логические элементы: И и НЕ, И-НЕ.

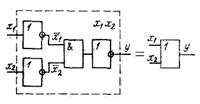

С помощью соединения ЛЭ И и НЕ можно получить элемент ИЛИ.

Логический базис может состоять и из одного типа элементов, например И-НЕ. Соединение таких элементов позволяет реализовать логические функции И, ИЛИ, НЕ.

Схема реализации в логическом базисе И-НЕ функций а) И; б) ИЛИ.

Универсальность элемента И-НЕ обеспечила ему широкое применение при создании логических устройств цифровой техники.

Существует и ряд других элементов, реализующих простейшие логические функции. К их числу, например, относятся элементы суммирования по модулю два, реализующих функцию неравнозначности двух переменных:

Функция неравнозначности равна единице лишь в случае, когда переменные х1 и х2 имеют разные значения.

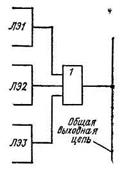

При построении цифровых устройств на базе ИЛЭ часто возникает необходимость объединения выходов нескольких ЛЭ с целью перехода на общую выходную цепь. Эта задача может решаться разными способами. Можно выполнить объединение нескольких выходных цепей с помощью логического элемента ИЛИ.

При этом приходится мириться с дополнительными затратами и увеличением задержки прохождения цифровых сигналов. Другой способ основан на применении в ЛЭ выходных цепей с открытым коллектором или эмиттером.

На рисунке, а показано объединение выходных цепей с открытым коллектором, к которым через внешний резистор подключен источник питания. Такое включение эквивалентно использованию дополнительного ЛЭ ИЛИ, поэтому его иногда называют «проводным (монтажным) ИЛИ». На функциональных схемах наличие выхода с открытым коллектором часто отмечается специальным символом в обозначении элемента (рис. б). Аналогично может быть организовано объединение выходных цепей с открытым эмиттером. На функциональных схемах такой выход также отмечается специальным символом (рис. в).

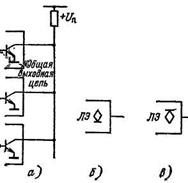

Один из наиболее широко используемых способов объединения выходов элементов основан на применении выходных цепей, допускающих управляемое отключение от нагрузки, называемое часто переходом в третье состояние. Обычно для этой цели используется выходной каскад на двух транзисторах.

Кроме состояний на выходе U0 (транзистор VT2 открыт, VT1 – заперт) и U1 (транзистор VT2 заперт, VT1 – открыт) может быть реализовано третье состояние, когда оба транзистора заперты. Такое состояние соответствует отключению выходного каскада от нагрузки. Наличие у ЛЭ выходов с тремя состояниями позволяет объединять выходы без использования дополнительных элементов.

Литература:

1. В.В. Стрыгин «Основы вычислительной, микропроцессорной техники и программирования» стр.: 72-82.

2. Б.Я. Лихтциндер «Микропроцессоры и вычислительные устройства в радиотехнике» стр.: 38-39, 45-46.

3. Э.В. Евреинов «Цифровая и вычислительная техника» стр.: 63-68.

4. В.А. Скаржепа «Электроника и микросхемотехника» ч. 1, стр.: 203-207.

ЗАНЯТИЕ 1.1.2 Назначение и классификация триггеров. Логика работы

функционально разных схем триггеров.

ВОПРОСЫ ЗАНЯТИЯ:

1. Триггеры. Общие сведения, назначение и классификация.

2. Логика работы функционально разных схем триггеров.

ПЕРВЫЙ ВОПРОС

Триггер – один из важнейших элементов цифровых вычислительных устройств. Триггеры могут быть собраны на транзисторах, на логических элементах в интегральном исполнении, а также выпускаются как готовые изделия в виде микросхем (один или несколько триггеров в общем корпусе).

Триггером называют устройство, которое может находиться в одном из двух устойчивых состояний и переходить из одного состояния в другое под воздействием входного сигнала с учетом состояния, в котором он находился в предшествующий момент времени.

Триггеры можно классифицироватьпо различным признакам.

1. По способу приема информации: асинхронные и синхронные.

Асинхронные триггеры воспринимают информационные сигналы и реагируют на них в момент их появления на входах триггера.

Синхронные триггеры реагируют на информационные сигналы при наличии разрешающего сигнала на специальном управляющем входе С, называемом входом синхронизации. Синхронные триггеры подразделяются:

- триггеры со статическим управлением воспринимают информационные сигналы при подаче на С-вход уровня 1 (прямой С-вход) или 0 (инверсный С-вход).

- триггеры с динамическим управлением воспринимают информационные сигналы при изменении сигнала на С-входе от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход).

Переход от 0 к 1 осуществляется по переднему фронту, а от 1 к 0 по заднему фронту. Наиболее широко используются – вторые. Их называют триггерами с внутренней задержкой. Возможность задержки момента опрокидывания триггера на время, равное длительности тактового импульса эффективно используется при обработке информации, позволяя по переднему фронту считывать, а по заднему записывать информацию.

2. По принципу построения триггеры со статическим управлением можно разделить на одноступенчатые и двухступенчатые.

Одноступенчатые триггеры характеризуются наличием одной ступени запоминания информации.

В двухступенчатых триггерах имеются две ступени запоминания информации. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе.

3. По функциональным возможностям различаются:

- триггеры с раздельной установкой состояний 0 и 1 (RS-триггеры);

- триггеры с приемом информации по одному входу D (D-триггер или триггер задержки);

- триггер со счетным входом Т (Т-триггер);

- универсальный триггер с информационными входами J и K (JK-триггер).

Существуют и другие типы триггеров, но они применяются реже, поэтому ограничимся приведеными выше.

Триггеры, не зависимо от их элементной базы и переключательных свойств, характеризуются рядом параметров: быстродействием, чувствительностью, потребляемой мощностью, помехоустойчивостью, функциональным возможностям.

Быстродействие определяется максимальной частотой переключения и достигает сотен мегагерц.

Чувствительность триггера определяется наименьшим напряжением на входе (пороговым напряжением), при котором происходит переключение.

Помехоустойчивость характеризуется способностью триггера нормально работать в условиях помех.

Функциональные возможности характеризуются числом входных сигналов.

Для триггера имеется стандартное обозначение. Здесь S и R – информационные входы, Q и  - выходы, Т - обозначает триггер. Для обозначения функциональных возможностей триггеров в интегральном исполнении используется следующая маркировка: TR – RS-триггер, ТВ – JK-триггер, ТМ – D-триггер.

- выходы, Т - обозначает триггер. Для обозначения функциональных возможностей триггеров в интегральном исполнении используется следующая маркировка: TR – RS-триггер, ТВ – JK-триггер, ТМ – D-триггер.

Рис.1. УГО триггера.

Для удобства использования в схемах ПЦУ триггеры имеют два выхода прямой – Q и инверсный  . Состоянию триггера 1 соответствует на выходе Q – высокий уровень, а на выходе

. Состоянию триггера 1 соответствует на выходе Q – высокий уровень, а на выходе  - низкий. Состоянию триггера 0 соответствует на выходе Q - низкий уровень сигнала, а на выходе

- низкий. Состоянию триггера 0 соответствует на выходе Q - низкий уровень сигнала, а на выходе  - высокий. Уровни сигналов на обоих выходах всегда противоположны.

- высокий. Уровни сигналов на обоих выходах всегда противоположны.

Входы триггера делятся на информационные и вспомогательные (управляющие). Сигналы, поступающие на информационные входы, устанавливают состояние триггера. Сигналы на вспомогательных входах используются для предварительной установки триггера в требуемое состояние и синхронизации. Вспомогательные входы могут использоваться и в качестве информационных. Число входов триггера зависит от его структуры и назначения. Информационные входы обозначаются: S, R, J, K, T, D а управляющие C и V.

Надо отметить, что если на выходе Q триггера уровень логической 1, то говорят, что триггер находится в единичном состоянии, если логический 0 – в нулевом состоянии, если значения выходов триггера не меняют своего значения – триггер находится в состоянии хранения информации.

В цифровых устройствах выходное напряжение зависит от входного и может иметь только одно из двух значений: равное (или почти равное) напряжению питания схемы и равное (или почти равное) напряжению на общей шине – нулевому. Эти уровни называются соответственно «логическая 1» и «логический 0».

ВТОРОЙ ВОПРОС

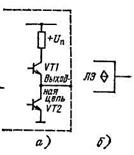

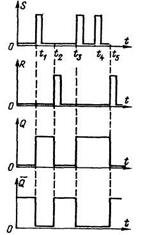

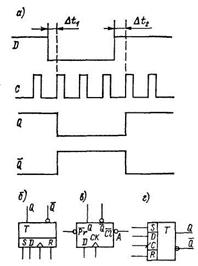

RS-триггеры.У триггеров этого типа поочередное поступление импульсов на информационные входы (R и S) ведет к смене состояния триггера. Если после подачи импульса на вход R импульс на вход 5 не поступит, а на вход R придет еще один импульс (на рис. 1.2 третий импульс на входе R), то на этот повторный импульс триггер не отреагирует и состояние его не изменится. Сказанное относится и к входу S (четвертый импульс на входе S).

Одновременное поступление импульсов на входы R и S (на рисунке второй импульс показан штрихами) не разрешается. Здесь требуется пояснить смысл предупреждения «не разрешается», которое будет встречаться в дальнейшем.

Рекомендация избегать определенной комбинации входных сигналов связана не с опасностью повреждения интегральной микросхемы, а с возможностью прихода в так называемое неопределенное состояние, которое заранее нельзя предсказать (1 или 0), т. е. устройство уже не будет действовать как истинный триггер с двумя строго определенными взаимно инверсными выходными уровнями (Q и Q).

Рис. 2. RS--триггер: а — временная диаграмма асинхронного триггера; б, в и г — условное графическое обозначение синхронного триггера с записью информации по фронту тактового импульса в болгарской, американской и советской литературе; д — условное графическое обозначение асинхронного триггера в советской литературе.

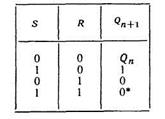

Таблица 1. Состояния RS-триггера

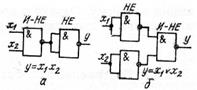

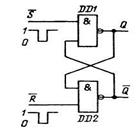

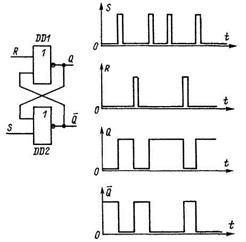

-триггер на логических элементах И—НЕ.Наиболее распространенный вид логических элементов в интегральном исполнении — это элементы И—НЕ. Как пример микросхем ТТЛ на биполярных транзисторах можно назвать микросхемы К155ЛАЗ и К555ЛАЗ, а микросхем КМОП на полевых транзисторах —К176ЛА7, К561ЛА7, 564ЛА7. На основе всех этих микросхем легко построить триггеры.

-триггер на логических элементах И—НЕ.Наиболее распространенный вид логических элементов в интегральном исполнении — это элементы И—НЕ. Как пример микросхем ТТЛ на биполярных транзисторах можно назвать микросхемы К155ЛАЗ и К555ЛАЗ, а микросхем КМОП на полевых транзисторах —К176ЛА7, К561ЛА7, 564ЛА7. На основе всех этих микросхем легко построить триггеры.

На рис. 2.5 приведена схема и временная диаграмма простейшего асинхронного  - триггера. Он содержит только два логических элемента И—НЕ. Один его вход обозначен

- триггера. Он содержит только два логических элемента И—НЕ. Один его вход обозначен  и служит для установки триггера в состояние 1, другой —

и служит для установки триггера в состояние 1, другой —  и служит для возвращения в состояние 0. Штрихи над обозначениями входов показывают, что управление осуществляется сигналами в момент их перехода от высокого уровня к низкому.

и служит для возвращения в состояние 0. Штрихи над обозначениями входов показывают, что управление осуществляется сигналами в момент их перехода от высокого уровня к низкому.

Как следует из рисунка, когда на входы  и

и  не поступают внешние сигналы (низкого уровня),триггер сохраняет свое состояние: неподключенный (открытый) вход микросхем ТТЛ «ведет» себя так, как если бы на нем был сигнал высокого уровня. Для микросхем КМОП входы открытыми оставлять нельзя. Неиспользуемые входы обязательно следует подключать к проводу питания или общему проводу в зависимости от конкретной реализуемой логической функции.

не поступают внешние сигналы (низкого уровня),триггер сохраняет свое состояние: неподключенный (открытый) вход микросхем ТТЛ «ведет» себя так, как если бы на нем был сигнал высокого уровня. Для микросхем КМОП входы открытыми оставлять нельзя. Неиспользуемые входы обязательно следует подключать к проводу питания или общему проводу в зависимости от конкретной реализуемой логической функции.

Если, например, Q=l и  =0, т. е. триггер в единичном состоянии _(на выходе Q — напряжение высокого уровня, и на выходе

=0, т. е. триггер в единичном состоянии _(на выходе Q — напряжение высокого уровня, и на выходе  — низкого),то вследствие соединения выхода элемента DD1 с одним из входов DD2 и выхода DD2 с одним из входов DD1 на обоих входах элемента DD2

— низкого),то вследствие соединения выхода элемента DD1 с одним из входов DD2 и выхода DD2 с одним из входов DD1 на обоих входах элемента DD2

действует напряжение высокого уровня, а на его выходе — низкого, что соответствует  =0. В это же время на одном из входов элемента DD1 напряжение низкого уровня (с выхода DD2),что достаточно для обеспечения на выходе DD1 напряжения высокого уровня (Q=l).

=0. В это же время на одном из входов элемента DD1 напряжение низкого уровня (с выхода DD2),что достаточно для обеспечения на выходе DD1 напряжения высокого уровня (Q=l).

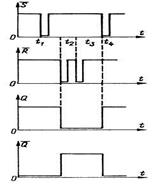

Если в этом состоянии триггера на вход  поступит сигнал указанной на диаграмме полярности (момент t1), состояние триггера не изменится. Поступление сигнала на второй вход DD1 только временно изменит сочетание сигналов на обоих входах (было высокое и низкое напряжение, а стало низкое и низкое), но при этом уровень выходного напряжения остается неизменным. Если, однако, сигнал поступит на вход

поступит сигнал указанной на диаграмме полярности (момент t1), состояние триггера не изменится. Поступление сигнала на второй вход DD1 только временно изменит сочетание сигналов на обоих входах (было высокое и низкое напряжение, а стало низкое и низкое), но при этом уровень выходного напряжения остается неизменным. Если, однако, сигнал поступит на вход  (момент t2), то на одном входе DD2 будет высокий уровень, а на другом — низкий, уровень напряжения на выходе изменится и станет высоким.

(момент t2), то на одном входе DD2 будет высокий уровень, а на другом — низкий, уровень напряжения на выходе изменится и станет высоким.

Рис. 3.  -триггер на логических элементах И—НЕ.

-триггер на логических элементах И—НЕ.

Рис. 4. Временные диаграммы работы  -триггера.

-триггера.

С этого момента на обоих входах DD1 окажется напряжение высокого уровня и на выходе состояние изменится с высокого уровня на низкое, т. е. триггер скачком перейдет в другое состояние, при котором Q = 0 и  =_l. Поэтому только при чередовании сигналов на входах

=_l. Поэтому только при чередовании сигналов на входах  и

и  возможна смена состояний триггера.

возможна смена состояний триггера.

При одновременном поступлении импульсов низкого уровня на оба входа  и

и  устройство теряет триггерные свойства и на обоих выходах возникает напряжение высокого уровня; с прекращением входных импульсов состояние триггера становится неопределенным. Поэтому одновременная подача импульсов на оба входа (

устройство теряет триггерные свойства и на обоих выходах возникает напряжение высокого уровня; с прекращением входных импульсов состояние триггера становится неопределенным. Поэтому одновременная подача импульсов на оба входа (  и

и  ) не разрешается. Это ограничение не связано с опасностью повреждения интегральной микросхемы, а только служит отражением того факта, что состояние триггера становится неопределенным и схема утрачивает свойства триггера. Исполнение логических элементов И—НЕ (ТТЛ или КМОП) не влияет на способ их включения в схеме триггера и на временные диаграммы, но всегда следует иметь в виду различие обоих видов интегральных микросхем и особенности их использования.

) не разрешается. Это ограничение не связано с опасностью повреждения интегральной микросхемы, а только служит отражением того факта, что состояние триггера становится неопределенным и схема утрачивает свойства триггера. Исполнение логических элементов И—НЕ (ТТЛ или КМОП) не влияет на способ их включения в схеме триггера и на временные диаграммы, но всегда следует иметь в виду различие обоих видов интегральных микросхем и особенности их использования.

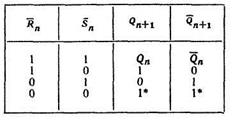

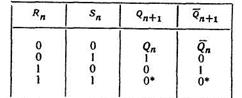

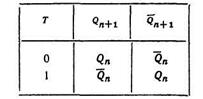

Таблица состояний  -триггера имеет следующий вид:

-триггера имеет следующий вид:

-триггеp реализуется на двух логических элементах И— НЕ. Смена состояния

-триггеp реализуется на двух логических элементах И— НЕ. Смена состояния  -триггеpa происходит при поступлении на входы сигналов низкого уровня. Триггер реагирует на первый импульс в последовательности импульсов, поступающих на вход

-триггеpa происходит при поступлении на входы сигналов низкого уровня. Триггер реагирует на первый импульс в последовательности импульсов, поступающих на вход  или

или  .

.

Напомним, что входные сигналы, обозначенные  и

и  , относятся к одному интервалу времени (такту) tn, а выходные сигналы Qn+1 и

, относятся к одному интервалу времени (такту) tn, а выходные сигналы Qn+1 и  — к другому интервалу времени (такту) tn+1, следующему после tn.

— к другому интервалу времени (такту) tn+1, следующему после tn.

RS-триггер на логических элементах И—НЕ. Как и  -триггер (см. рис. 2.5), RS-триггер «запоминает» своим выходным состоянием, на какой из двух входов (R или S) поступил последний импульс: если на вход R, триггер принимает нулевое состояние (Q = 0 и

-триггер (см. рис. 2.5), RS-триггер «запоминает» своим выходным состоянием, на какой из двух входов (R или S) поступил последний импульс: если на вход R, триггер принимает нулевое состояние (Q = 0 и  =l), а если на вход S,— единичное

=l), а если на вход S,— единичное

состояние (Q=l и  =0).

=0).

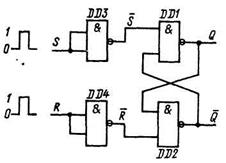

На рис. 2.6 приведена схема RS-триггера на логических

элементах И—НЕ. Она повторяет схему  -триггера (логические элементы DD1 и DD2 на рис. 2.5) — с той разницей, что к каждому входу добавлено по инвертору (DD3 и DD4), которые только меняют уровень входных сигналов: переключающим вместо сигнала с 0 на 1 становится сигнал с 1 на 0. Действие триггера поясняет временная диаграмма. Изменение уровней входных сигналов от низкого к высокому приводит к смене состояния триггера (моменты времени t1, t2, t3 и t5; в момент t4 переключения не происходит, так как триггер уже установлен в единичное состояние в предшествующий момент t3). Все сказанное о

-триггера (логические элементы DD1 и DD2 на рис. 2.5) — с той разницей, что к каждому входу добавлено по инвертору (DD3 и DD4), которые только меняют уровень входных сигналов: переключающим вместо сигнала с 0 на 1 становится сигнал с 1 на 0. Действие триггера поясняет временная диаграмма. Изменение уровней входных сигналов от низкого к высокому приводит к смене состояния триггера (моменты времени t1, t2, t3 и t5; в момент t4 переключения не происходит, так как триггер уже установлен в единичное состояние в предшествующий момент t3). Все сказанное о  -триггере остается в силе и для RS-триггера. Единственное различие касается уровней входных сигналов: R вместо

-триггере остается в силе и для RS-триггера. Единственное различие касается уровней входных сигналов: R вместо  и S вместо

и S вместо  .

.

Рис. 5. RS-триггер на логических элементах И—НЕ.

Рис. 6. Временная диаграмма работы RS-триггера.

Поведение RS-триггера отображает следующая таблица:

Одновременная подача сигналов высокого уровня на оба входа не разрешается.

Триггер меняет свое состояние при чередовании на входах

импульсов вида c 0 на1.Он реагирует на первый (из последовательности) импульс, поступающий на вход R или S.

RS-триггер на логических элементах ИЛИ—НЕ.Из логических элементов ИЛИ—НЕ наибольшее распространение имеют следующие типы: К155ЛЕ1, К555ЛЕ1 (интегральные микросхемы ТТЛ) и К176ЛЕ5, К561ЛЕ5, 564ЛЕ5 (интегральные микросхемы КМОП). В корпусе каждой из упомянутых микросхем содержится четыре независимых двухвходовых элемента, связанных общим питанием. RS-триггер, схема и временная диаграмма которого приведены на рис. 2.7, собран из таких элементов.

Состояние этого триггера определяется сигналами, поступающими на входы R и S. Если R = S = 0, триггер сохраняет свое состояние, так как выходные уровни обоих логических элементов не изменяются. При S=1и R=0 уровень выходного напряжения логического элемента DD2 становится низким, т. е.  =0, независимо от значения сигнала на втором входе этого элемента.

=0, независимо от значения сигнала на втором входе этого элемента.

Рис. 7. RS-триггер на логических элементах ИЛИ—НЕ.

Поскольку на обоих входах логического элемента DD1 в данный момент действуют сигналы низкого уровня, на его выходе будет сигнал высокого уровня и, следовательно, Q=l. Это напряжение обеспечит сохранение состояния  =0 и в том случае, когда напряжение на входе S снова станет низкого уровня (S = 0). Подобным же образом при S = 0 и R=1 на выходе будет Q = 0 и

=0 и в том случае, когда напряжение на входе S снова станет низкого уровня (S = 0). Подобным же образом при S = 0 и R=1 на выходе будет Q = 0 и  =l, т. е. триггер установится в другое устойчивое состояние.

=l, т. е. триггер установится в другое устойчивое состояние.

При одновременном появлении на входах сигналов S = R=1напряжение на обоих выходах станет низкого уровня (Q =  = 0), и если после этого входные сигналы одновременно изменятся на S = R=0, то выходное состояние триггера с равной вероятностью может стать Q=l и

= 0), и если после этого входные сигналы одновременно изменятся на S = R=0, то выходное состояние триггера с равной вероятностью может стать Q=l и  =0 либо Q = 0 и

=0 либо Q = 0 и  =l. По этой причине сочетание входных сигналов S = R=1считается запрещенным. Однако подчеркнем еще раз, что это ограничение не связано с опасностью для самой схемы. Оно лишь отражает тот факт, что при подаче такой комбинации сигналов на входы схема утрачивает триггерные свойства.

=l. По этой причине сочетание входных сигналов S = R=1считается запрещенным. Однако подчеркнем еще раз, что это ограничение не связано с опасностью для самой схемы. Оно лишь отражает тот факт, что при подаче такой комбинации сигналов на входы схема утрачивает триггерные свойства.

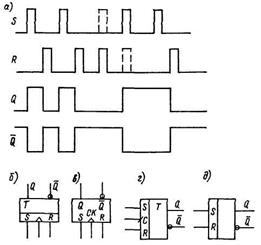

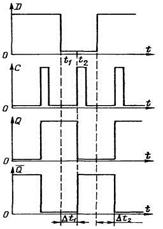

D-триггеры.Втриггерах этого типа на выходе Q устанавливается тот же уровень напряжения, что и на информационном входе D, но не сразу, а после того как на тактовый вход С поступит синхронизирующий импульс, т. е. с некоторой задержкой (рис. 1.3). На рисунке показаны два дополнительных

входа (S и R либо Рr и Сl), которые служат для установки начального (исходного) состояния триггера. На практике в основном используются синхронные D-триггеры.

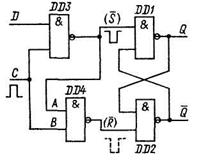

D-триггер на логических элементах И—НЕ.На рис. 2.8 показано, что можно создать D-триггер, используя только логические элементы И—НЕ. Это интегральные схемы К155ЛАЗ, К555ЛАЗ (ТТЛ) либо К176ЛА7, К561ЛА7, 564ЛА7 (КМОП).

Схема D-триггера содержит четыре логических элемента И— НЕ. Здесь элементы DD1 и DD2 образуют знакомый  -триггер (ср. с рис. 2.5).

-триггер (ср. с рис. 2.5).

Дополнительные элементы DD3 и DD4 обращают его в D-триггер. Действует этот триггер следующим образом. Если D=1то при наличии на входе С тактового сигнала С= 1на выходе DD3 формируется сигнал, вид которого представлен на временной диаграмме и который действует подобно сигналу  на входе

на входе  -триггера (см. рис. 2.5), в результате чего на выходе Q установится напряжение высокого уровня (Q=l, a

-триггера (см. рис. 2.5), в результате чего на выходе Q установится напряжение высокого уровня (Q=l, a  = 0).

= 0).

Рис. 8. D-триггер: а — временная диаграмма; б, в и г — условное графическое обозначение триггера с записью информации по фронту тактового импульса в болгарской, американской и советской литературе. Входы S и R (Рr и Сl) — установочные.

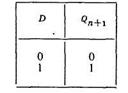

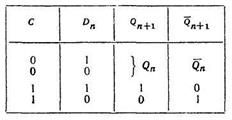

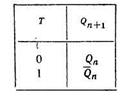

Таблица 2. Состояния D- триггера

В этом случае на выходе DD4 — напряжение высокого уровня, поскольку в отсутствие тактового импульса на входе А будет напряжение высокого и на входе В — низкого уровня. С приходом тактового импульса (С=1) на входе А возникает напряжение низкого, а входе В — высокого уровня.

Рис. 9. D-триггер на логических элементах И—НЕ

Рис. 10. Временные диаграммы работы D-триггера.

Если на вход D подано напряжение низкого уровня, на выходе DD3 будет напряжение высокого уровня, а тактовый импульс (показан на рисунке штрихами), инвертированный логическим элементом DD4, действует подобно  сигналу. Вследствие этого триггер примет состояние Q = 0 и

сигналу. Вследствие этого триггер примет состояние Q = 0 и  = 1.

= 1.

D-триггер имеет следующую таблицу состояний:

Выход Q у D-триггера принимает то же состояние, что и на входе D, в момент появления тактового импульса на входе С.

D-триггер можно собрать из четырех элементов И—НЕ.

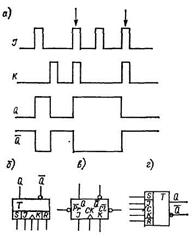

JK-триггеры.Действие JK-триггера поясняет рис. 1.4. Эти триггеры могут быть синхронными или асинхронными. Из временных диаграмм работы асинхронного JK-триггера следует, что при поочередном поступлении импульсов на входы J и К этот триггер действует подобно RS-триггеру (см. рис. 1.2, а), но отличается от него при одновременной подаче импульсов на оба входа: выходное состояние меняется на противоположное предшествующему. На рис. 1.4, а это относится к импульсам, помеченным стрелкой.

Рис. 11. УК-триггер: a— временная диаграмма; б, в и г — условное графическое обозначение триггера с записью информации по фронту тактового импульса в болгарской, американской и,, советской литературе. Входы S и R (Рr и Сl) —установочные.

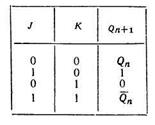

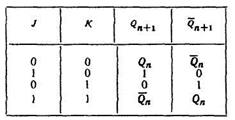

Таблица 3. Состояния JK-триггера

JK-триггер на логических элементах И—HЕ. С помощью

логических элементов И-НЕ К155ЛАЗ, К555ЛАЗ (ТТЛ) или К561ЛА7 (КМОП) нетрудно организовать JK-триггер. Для этого потребуется четыре логических элемента. Схема JK-триггера (рис. 2.10) отличается от схемы RS-триггера только тем, что элементы DD3 и DD4 используются по прямому назначению И—НЕ, а не как инверторы. Вход A3 соединен с выходом  , а вход В4 — с выходом Q. Действие его поясняют временные диаграммы. Если JK-триггер пребывает в нулевом состоянии (Q=0 и

, а вход В4 — с выходом Q. Действие его поясняют временные диаграммы. Если JK-триггер пребывает в нулевом состоянии (Q=0 и  =1, время до момента t1)и на вход J поступит сигнал указанной на диаграмме полярности, то за счет связи между выходом

=1, время до момента t1)и на вход J поступит сигнал указанной на диаграмме полярности, то за счет связи между выходом  и входом A3 сигнал на выходе элемента DD3 будет иметь вид с 0 на 1и действовать подобно сигналу

и входом A3 сигнал на выходе элемента DD3 будет иметь вид с 0 на 1и действовать подобно сигналу  на входе

на входе  -триггера, образованного элементами DD1 и DD2, т. е. вызовет смену состояния триггера. (В это время на входе К напряжение низкого уровня, на входе В4, связанном с выходом Q, тоже низкий уровень, в результате чего на выходе DD4 напряжение высокого уровня). Если JK-триггер находится в единичном состоянии (Q=l и

-триггера, образованного элементами DD1 и DD2, т. е. вызовет смену состояния триггера. (В это время на входе К напряжение низкого уровня, на входе В4, связанном с выходом Q, тоже низкий уровень, в результате чего на выходе DD4 напряжение высокого уровня). Если JK-триггер находится в единичном состоянии (Q=l и  =0 — до момента t1) и сигнал поступит на вход К, то, рассуждая аналогичным образом, можно убедиться, что на выходе DD4 появится сигнал низкого уровня (на схеме показан штрихами), который действует как сигнал

=0 — до момента t1) и сигнал поступит на вход К, то, рассуждая аналогичным образом, можно убедиться, что на выходе DD4 появится сигнал низкого уровня (на схеме показан штрихами), который действует как сигнал  , т. е. состояние триггера изменится снова. (При этом на выходе DD3 напряжение высокого уровня). Когда одновременно на обоих входах — J и К напряжение низкого уровня, состояние JK-триггера сохраняется.

, т. е. состояние триггера изменится снова. (При этом на выходе DD3 напряжение высокого уровня). Когда одновременно на обоих входах — J и К напряжение низкого уровня, состояние JK-триггера сохраняется.

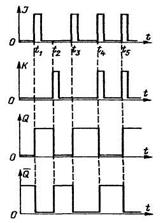

Рис. 12. JK-триггер на логических элементах И—НЕ.

Рис. 13. Временная диаграмма работы JK-триггера.

Как видим, до сих пор действие JK- и RS-триггеров полностью совпадало. При этом вход J соответствовал входу S, а К — входу R.

Когда на обоих входах — J и К одновременно появляется напряжение высокого уровня, то в зависимости от предшествующего состояния триггера возможны два случая.

1. JK-триггер был в единичном состоянии (Q=l и  = 0 — после момента t3). Поскольку на входе A3 действует сигнал

= 0 — после момента t3). Поскольку на входе A3 действует сигнал  = 0, на выходе DD3 сохраняется напряжение высокого уровня, независимо от того что на входе ВЗ элемента DD3 возникло напряжение высокого уровня J=1. При этом на выходе логического элемента DD4, который действует как И—НЕ, за счет оединения входа В4 с выходом Q (Q=l) появится сигнал

= 0, на выходе DD3 сохраняется напряжение высокого уровня, независимо от того что на входе ВЗ элемента DD3 возникло напряжение высокого уровня J=1. При этом на выходе логического элемента DD4, который действует как И—НЕ, за счет оединения входа В4 с выходом Q (Q=l) появится сигнал  и триггер

и триггер  -типа, образованный элементами DD1 и DD2, изменит свое состояние. Уровень напряжения на выходе Q станет низким, а на выходе

-типа, образованный элементами DD1 и DD2, изменит свое состояние. Уровень напряжения на выходе Q станет низким, а на выходе  — высоким (начиная с момента t4).

— высоким (начиная с момента t4).

2. JK-триггер был в нулевом состоянии (Q= 0 и  =1 — после момента t4). Рассуждая аналогичным образом, нетрудно убедиться, что на выходе DD4 сохраняется напряжение высокого уровня, а на выходе DD3— низкого, которое действует как сигнал

=1 — после момента t4). Рассуждая аналогичным образом, нетрудно убедиться, что на выходе DD4 сохраняется напряжение высокого уровня, а на выходе DD3— низкого, которое действует как сигнал  , переключающий

, переключающий  -триггер (напряжение на выходе Q станет высоким, а на выходе

-триггер (напряжение на выходе Q станет высоким, а на выходе  — низким — после момента t5).

— низким — после момента t5).

Таким образом, в обоих случаях JK-триггер меняет свое состояние. В этом как раз и состоит различие между JK- и RS-триггерами.

Работа JK-триггера определяется следующей таблицей состояний:

Триггер можно собрать из логических элементов И-НЕ.

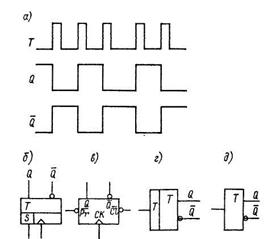

T-триггеры.Эти триггеры — асинхронные, имеют только один информационный вход, и каждый импульс, поступающий на него, ведет к смене выходного состояния (рис. 1.5).

Часто для иллюстрации действия триггеров пользуются не временными диаграммами, а таблицами состояний (табл. 1.1... 1.4). В таблицах индексом п обозначено состояние триггера до момента воздействия сигнала на информационном входе, а индексом п+1 — после этого момента.

Рис. 14. T-триггер: а — временная диаграмма; б, в и г, д — условное графическое обозначение в болгарской, американской и советской литературе.

Таблица 4. Состояния T-триггера

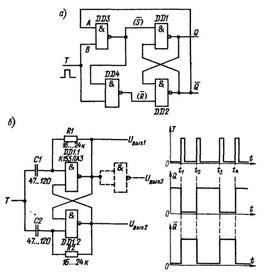

Т-триггер на логических элементах И—НЕ.Из уже упоминавшихся логических элементов в интегральном исполнении типа К155ЛАЗ, К555ЛАЗ (ТТЛ) либо типа К176ЛА7, К561ЛА7 (КМОП) легко собрать Т-триггер. Для этого потребуется четыре логических элемента И—НЕ. Схема приведена на рис. 2.9, а.

В отличие от D-триггера (см. рис. 2.8) вход А логического элемента DD3 постоянно соединен с выходом  . Действие этого триггера легко понять. Когда Q=l, на другом выходе

. Действие этого триггера легко понять. Когда Q=l, на другом выходе  = 0. Так как вход А соединен с выходом

= 0. Так как вход А соединен с выходом  , то и А=0. После поступления тактового импульса на вход Т на выходах установится Q=0 и

, то и А=0. После поступления тактового импульса на вход Т на выходах установится Q=0 и  =l. На выходе А при поступлении следующего тактового импульса уже будет напряжение высокого уровня и произойдет очередная смена состояния.

=l. На выходе А при поступлении следующего тактового импульса уже будет напряжение высокого уровня и произойдет очередная смена состояния.

Рис. 15. Т-триггер на логических элементах И—НЕ: а — на четырех элементах; б — на двух элементах с RС-цепочками.

Работа Т-триггера характеризуется следующей таблицей состояний:

Смена состояния Т-триггера происходит после поступления на вход очередного импульса.

Т-триггер можно собрать из логических элементов И—НЕ.

У всех рассмотренных триггеров смена состояний происходит по фронту импульса. Существуют триггеры, для которых активным может быть срез (спад) импульса. В дальнейшем эти случаи будут специально оговариваться.

Установочные входы служат для пре

|

из

5.00

|

Обсуждение в статье: Простейшие ЛЭ имеют следующие характеристики |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы