|

Главная |

Методы Изоляции элементов друг от друга в микросхемах 8 страница

|

из

5.00

|

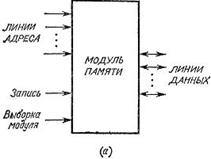

Различаются они только линиями данных. У модели на рис. 1(a) имеется лишь один комплект линий данных, по которым передаются как поступающие данные при записи, так и выдаваемые данные при чтении. Модель на рис. 1 (б) содержит два раздельных комплекта линий для поступающих и выдаваемых данных.

Рисунок 1 - Линии внешних сигналов в модулях памяти с произвольным доступом.

(а) Модуль с двунаправленными линиями данных.

(б) Модуль с раздельными линиями для поступающих и выдаваемых данных.

Обе модели имеют комплект адресных линий, сигналы на которых определяют ячейку, к которой осуществляется обращение для считывания или записи данных. В обеих моделях управляющая линия «запись» задает режим записи («запись»=1) или режим чтения («запись»=0). Наконец, управляющая линия «выборка модуля» в обоих случаях либо разрешает выполнение операций чтения/записи в данном модуле («выборка модуля» =1), либо запрещает ее выполнение («выборка модуля»=0).

Для того чтобы модули памяти, соответствующие любой из двух моделей, можно было включать в многомодульную систему ЗУ с шинной организацией, на линиях выдачи данных (т. е. на линиях данных в модели рис. 1(a) и на линиях выходных данных в модели на рис. 1(б)) используются вентили, допускающие монтажную логику. Модуль памяти любой модели выдает данные на выходные линии только при чтении; во всех остальных ситуациях этими линиями могут пользоваться другие модули памяти или устройства, подключенные к линиям. Это особенно важно для случая на рис. 1(a), поскольку при записи для передачи данных в ЗУ должны использоваться те же линии.

Состояние линий выходных данных, когда в модуле не выполняется чтение, конечно, зависит от типа монтажной логики. Например, для монтажного И на схемах ТТЛ с открытым коллектором состояние на свободной линии должно соответствовать логической 1, поскольку в данном случае 0 доминирует над 1 и, следовательно, другое устройство или модуль памяти сможет задать нужное ему состояние на линии. Для монтажного ИЛИ свободное состояние должно быть логическим 0. Для тристабильной монтажной логики свободное состояние — это, конечно, третье состояние с высоким импедансом, эквивалентное отсутствию соединения с линией. В любом случае линия выходных данных оказывается в свободном состоянии, когда либо подана логическая 1 на линию «запись», либо подан логический 0 на линию «выборка модуля».

Внутренняя организация ЗУ с произвольным доступом

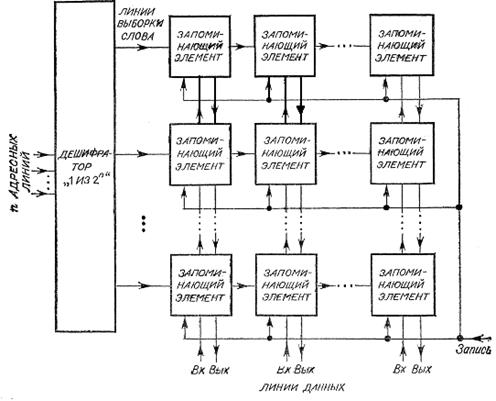

Рассмотрев внешние характеристики типичных модулей памяти с произвольным доступом, перейдем теперь к их внутренней организации. Одна из возможных схем, позволяющая выбирать нужную ячейку и осуществлять передачу информации в нее или из нее, представлена на рис. 2. В запоминающем элементе для хранения одного бита слова применяется асинхронный RS-триггер. Помимо триггера, каждый запоминающий элемент содержит вентили для передачи информации между триггером и внутренними линиями данных.

Рассмотрев внешние характеристики типичных модулей памяти с произвольным доступом, перейдем теперь к их внутренней организации. Одна из возможных схем, позволяющая выбирать нужную ячейку и осуществлять передачу информации в нее или из нее, представлена на рис. 2. В запоминающем элементе для хранения одного бита слова применяется асинхронный RS-триггер. Помимо триггера, каждый запоминающий элемент содержит вентили для передачи информации между триггером и внутренними линиями данных.

Рисунок 2 - Внутренняя организация памяти с произвольным доступом.

Одна из двух операций, чтение или запись, выполняется одновременно для всех элементов одной «строки». Каждая «строка» представляет собой ячейку для хранения слова и имеет свой адрес. Дешифратор «1 из 2n» служит для выбора ячейки по заданному адресу. На n входных линиях дешифратора возможны 2n комбинаций. Именно на них подается адрес нужной ячейки. Выходные 2n линий дешифратора называются линиями выборки слова. В зависимости от поданной на вход дешифратора комбинации какая-то одна линия выборки слова получает значение логической 1, а все остальные — логического 0. Каждая линия выборки слова используется как линия, разрешающая операцию чтения или записи во всех элементах строки.

В каждом столбце имеются по две внутренние линии: одна — для передачи данных в память (вход), а другая — из памяти (выход). Состояние линии «:выход» определяется состоянием запоминающего элемента в выбранной строке. Для этого выход триггера в каждом элементе логически умножается на сигнал «выборка слова», а логическая сумма всех результатов поступает в линию «:выход». Таким образом, чтение слова из памяти осуществляется подачей адреса нужного слова на вход дешифратора и наблюдением состояния на линиях «выход».

Линия «вход» каждого столбца используется для передачи информации в запоминающий элемент выбранной строки при выполнении операции записи. Это осуществляется с помощью двух вентилей И на каждый запоминающий элемент, которые при наличии сигналов «выборка слова» и «запись» передают сигнал из линии «вход» на вход S триггера, а его дополнение — на вход R. Таким образом, запись слова в память производится заданием адреса нужной ячейки на входе дешифратора, а записываемого слова — на линии «вход» и затем — логической 1 на управляющей линии «запись».

Нужно обратить внимание, что в приведенном выше описании фигурировали сигналы на линиях «запись», «вход» и «выход», являющиеся внутренними для модуля памяти. Эти сигналы связаны с внешними по отношению к модулю сигналами с помощью соответствующих вентилей и буферных схем. Такая связь может быть реализована различными способами в зависимости от требуемых внешних характеристик модуля.

Например, внешние характеристики модуля на рис. 1(a) можно получить с помощью схемы рис. 3. На ней три внешние линии: «запись», «выборка модуля» и «данные». Внутренний сигнал «запись» получается как И от внешних сигналов «запись» и «выборка модуля». Внутренние линии «вход данных» и «выход данных» для каждого бита в слове соединяются с внешней линией «данные» через входную буферную схему и тристабильный выходной формирователь, как показано на рисунке. Тристабильный формирователь управляется сигналом И от сигнала «выборка модуля» и инверсии сигнала «запись». Таким образом, внешняя линия данных работает как двунаправленная, подавая информацию на линию входа данных при записи и принимая информацию с линии выхода данных при чтении.

Рисунок 16 - Связь между внешними и внутренними сигналами в модуле памяти

2. Запоминающие устройства на биполярных транзисторах

Транзисторно-транзисторная логика — это одно из важнейших семейств логических элементов. Вентили этого семейства выполнены исключительно на биполярных транзисторах. Одна из возможных схем ТТЛ-вентиля представлена на рис. 3. Логические значения 0 и 1 соответствуют номинальным уровням потенциала 0В и +5 В. Как показано на рисунке, схему можно условно разделить на три части, рассмотренные нами в предыдущем разделе: комбинатор, восстановитель и буфер. Действие каждой из этих частей мы будем теперь изучать по отдельности.

Рисунок 3 - ТТЛ-вентиль с нагрузочным резистором.

Комбинационная часть вентиля представлена многоэмиттерным транзистором Т1. На схеме показаны два эмиттера, но их может быть и больше. Каждый входной сигнал подается на свой эмиттер. Каждый эмиттер образует pn-переход с базой. При этом подразумевается, что если хотя бы один переход база-эмиттер имеет достаточное прямое смещение, то транзистор находится в проводящем состоянии, т. е. через вывод коллектора может протекать ток.

Поскольку на базу через резистор подается положительный потенциал, то переход база-эмиттер оказывается смещенным вперед всякий раз, когда потенциал соответствующего эмиттера близок к «нулевому», т. е. к потенциалу заземленной точки. Таким образом, транзистор будет находиться в проводящем состоянии, если хотя бы один эмиттер имеет низкий потенциал (логический 0). В этом случае через эмиттеры с низким потенциалом будет протекать заметный ток, обусловленный в основном током базы. Когда на все эмиттеры подается высокий потенциал (логическая 1), транзистор закрыт и ток во всех эмиттерах очень слабый.

Восстановительная часть вентиля состоит из транзистора Т2 и двух резисторов. База транзистора Т2 соединена с коллектором Т1, так что ток коллектора Т1 является током базы Т2. Когда транзистор Т1 комбинатора открыт, ток протекает от его коллектора к эмиттеру или эмиттерам, имеющим низкий потенциал. Направление этого тока противоположно тому, которое должен иметь ток базы транзистору Т2 для того, чтобы его переход база-эмиттер имел прямое смещение. Это означает, что всякий раз, когда транзистор Т1 открыт, транзистор Т2 закрыт.

В действительности заметней ток протекает от базы Т2 к коллектору Т1 лишь в течение коротких периодов, требующихся для того, чтобы Т2 перешел из насыщенного состояния в закрытое. Этот ток поддерживается уходящими из области базы Т2 зарядами, накопившимися за то время, пока транзистор Т2 находился в насыщенном состоянии. После того как Т2 оказывается закрытым, через его базу проходит лишь очень слабый ток.

С другой стороны, если транзистор Т1 закрыт, его переход база-коллектор смещен в прямом направлении, благодаря тому что к резистору базы приложен потенциал +5 В. Поэтому переход база-коллектор Т1 , как и любой pn-диод, имеющий прямое смещение, должен находиться в проводящем состоянии. Это в свою очередь обусловливает прямое смещение перехода база-эмиттер Т2, так что Т2 оказывается в насыщенном (проводящем состоянии). Каждое из этих двух противоположных состояний транзистора Т2 (отсечка и насыщение) наблюдается на самом деле для целого диапазона условий на входе. В этом смысле цепь транзистора Т2 действительно играет роль восстановителя сигнала.

Буферная часть вентиля состоит из транзистора Т3 и резистора. Потенциал базы Т3 управляется эмиттером транзистора Т2восстановителя. Когда транзистор Т2 находится в проводящем состоянии, потенциал его эмиттера принимает некоторое положительное значение между 0 и +5 В; конкретное значение зависит от двух резисторов в цепи восстановителя. Это в свою очередь приводит к тому, что переход база-эмиттер буферного транзистора Т3 имеет прямое смещение, вследствие чего транзистор Т3 оказывается открытым. В такой ситуации на выходе вентиля наблюдается потенциал, близкий к потенциалу «земли».

С другой стороны, когда транзистор Т2 восстановительной цепи не проводит, уровень потенциала на его эмиттере оказывается «нулевым». По этой причине переход база-эмиттер транзистора Т3 не будет иметь прямого смещения, и, следовательно, Т3 будет закрыт. В этой ситуаций благодаря резистору в коллекторной цепи буфера на выходе вентиля установится потенциал, близкий к потенциалу питания +5 В. Действительная величина потенциала на выходе зависит от падения напряжения на резисторе, которое обусловлено проходящим через этот резистор током нагрузки. Поведение рассмотренного нами ТТЛ-вентиля описано в табл. 1. Если заменить значения 0 В и 5 В соответственно на 0 и 1, то мы увидим, что табл. 1 описывает поведение логического вентиля, реализующего функцию И-НЕ. Если схема имеет лишь один эмиттер на входе, то такой вентиль является инвертором.

Таблица 1 - Действие ТТЛ-вентиля, изображенного на рис. 3

| А В | Состояние Т1 Состояние Т2 Состояние Т3 | Выход |

| 0 В 0 В 0 В 5 В 5 В 0 В 5 В 5 В | Открыт Закрыт Закрыт Открыт Закрыт Закрыт Открыт Закрыт Закрыт Закрыт Открыт Открыт | ~5 В

~5 В

~5 В

~0 В

|

Теперь вернемся опять к буферной части вентиля. Буфер должен быть способен пропустить ток, который необходим для правильной работы входных цепей подключенных к нему других вентилей. Существенный ток на входе ТТЛ-вентиля наблюдается лишь тогда, когда этот вход имеет низкий потенциал. В этом случае ток течет от входа управляемого вентиля к выходу управляющего вентиля. Рассмотренная нами буферная цепь удовлетворяет требованиям, предъявляемым к управляющему вентилю, если его буферный транзистор способен пропустить через себя суммарный ток, приходящий ото всех управляемых им входов, а также от своего коллекторного резистора.

Однако задержка распространения сигнала для такого вентиля будет большой из-за того, что для переключения от низкого потенциала на выходе к высокому при закрытом буферном транзисторе используется резистор. Между выходной линией вентиля и «землей» всегда образуется довольно ощутимая паразитная емкость. Эта емкость складывается не только из емкости монтажных соединений, но и из емкости на переходах транзисторов.

Паразитная емкость должна успеть зарядиться, прежде чем выход вентиля сможет перейти от низкого уровня потенциала к высокому. Ток заряда в основном течет через коллекторный резистор. Таким образом, потенциал на выходе растет экспоненциально с постоянной времени, определяемой сопротивлением резистора и паразитной емкостью. Переключение от высокого потенциала к низкому происходит значительно быстрее, поскольку емкость разряжается на землю через низкое сопротивление открытого транзистора.

3. Запоминающие устройства на полевых транзисторах.

Существует несколько семейств элементов на полевых транзисторах. Два широко известных семейства построены на основе n-МОП-технологии и p-МОП-технологии и используют соответственно n-канальные и р-канальные транзисторы. Третье семейство, построенное на основе КМОП-технологии, использует в одном вентиле как n-канальные, так и р-канальные транзисторы.

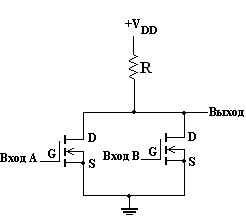

Логические элементы на n-канальных и p-канальных МОП-транзисторах обычно выполнены в виде схем с непосредственной связью. Это означает, что для реализации различных логических функций используется последовательное-параллельное соединение транзисторов, действующих как переключатели. Например, вентиль ИЛИ-НЕ с двумя входами можно построить путем параллельного соединения двух n-канальных нормально закрытых (работающих в режиме обогащения) МОП-транзисторов. Этот вентиль изображен на рис. 8.

Рисунок 8 - Вентиль ИЛИ-НЕ с двумя входами, построенный на n-канальных нормально закрытых МОП-транзисторах.

Если к одному из транзисторов приложено положительное напряжение, он переходит в открытое состояние и образует тем самым путь низкого сопротивления между выходной линией и землей. В результате на выходе устанавливается низкий потенциал. С другой стороны, если к обоим транзисторам приложен потенциал земли, они будут закрыты. В этой ситуации через линию резистора R на выходе установится потенциал, приблизительно равный VDD , так как закрытые транзисторы имеют высокий импеданс. В рамках положительной логики вентиль на рис. 8 реализует логическую операцию ИЛИ-НЕ, потому что низкий уровень на выходе наблюдается тогда и только тогда, когда по крайней мере на один из входов подан высокий потенциал.

Если n-канальные нормально закрытые МОП-транзисторы соединить последовательно, как показано на рис. 9, то получится вентиль И-НЕ. В этом случае, лишь когда оба входа имеют высокий потенциал, последовательно соединенные транзисторы образуют путь со сравнительно низким сопротивлением между выходом и землей. Если хоти бы один вход имеет низкий потенциал, на выходе будет приблизительно VDD . Поскольку при последовательном соединении сопротивлении складываются, количество последовательно соединенных транзисторов ограничено.

Рисунок 9 - Вентиль И-НЕ с двумя входами, построенный на n-канальных нормально закрытых МОП-транзисторах.

Устройство р-МОП-вентилей в основном аналогично n-МОП-схемам. Однако р-канальные МОП-транзисторы работают при отрицательном напряжении на затворе и стоке по отношению к истоку. Поэтому р-МОП-вентили, подобные изображенному на рис. 10 инвертору, имеют отрицательное питающее напряжение, и уровни потенциала на выходе у них отрицательные.

Рисунок 10 - p-МОП-инвертор.

МОП-транзисторы отличаются очень высоким сопротивлением для тока затвора, вследствие чего в статическом состоянии МОП-вентили практически не потребляют тока от управляющих ими схем. Это означает, что они имеют большой коэффициент разветвления по выходу. Наряду с этим они позволяют достичь сравнительно высокой плотности упаковки логических элементов в интегральной схеме. С другой стороны, емкости, образующиеся между затвором МОП-транзистора, истоком, стоком и подложкой, довольно значительны. Поэтому вентили на МОП-транзисторах отличаются меньшим быстродействием по сравнению с биполярными семействами—эти емкости должны успеть перезарядиться, прежде чем произойдет переключение. Кроме того, ток, перезаряжающий емкости, должен поступать от управляющего вентиля, что приводит к значительному увеличению рассеиваемой мощности при высокой частоте переключения.

ДВУМЕРНАЯ АДРЕСАЦИЯ

Недостаток рассмотренной схемы ЗУ произвольного доступа связан с большим размером адресного дешифратора. Например, при n = 10 адресный дешифратор должен иметь 210= 1024 выхода. Каждый выход должен быть соединен с запоминающим элементом в строке. Количество связей можно уменьшить, если часть функций дешифратора передать самому запоминающему элементу.

Чтобы показать, каким образом это может быть сделано, возьмем один столбец ЗУ с организацией, приведенной на рис. 2, и построим из него прямоугольную матрицу. При n=10 число запоминающих элементов равно 210. Можно построить матрицу размером 25х25 или в общем случае 2nx2n-m эту как показано на рис. 4. Каждый элемент исходного столбца теперь лежит на пересечении новых строки и столбца прямоугольной матрицы. Возьмем два дешифратора с n/2 входными и 2n/2 выходными линиями в каждом (будем считать, что n четно и матрица квадратная). При n=10 число 2n2 равно 32. Выходные линии одного дешифратора будут служить для выборки строки, а другого — для выборки столбца матрицы. Общее число выходных линий в дешифраторах при таком подходе равно 2n/2+2n/2=2n/2+1, что существенно меньше 2П линий при одном адресном дешифраторе.

ЗАПОМИНАЮЩИЕ ЭЛЕМЕНТЫ

Рисунок 4 - Двумерная адресация ЗУ с произвольным доступом.

В каждом запоминающем элементе должна выполняться операция И над линиями выборки строки и столбца. Эта операция даст логическую 1 только для одного элемента, находящегося на пересечении выбранных строки и столбца, и логический 0 для всех остальных элементов, поскольку для них либо сигнал выборки столбца, либо строки будет равен 0. Выходной сигнал вентиля И выполняет функции сигнала выборки бита, который разрешает чтение или запись в данном элементе.

Аналогичные двумерные матрицы нужны для всех остальных битов в слове. Матрицы можно считать лежащими в параллельных плоскостях. Оба адресных дешифратора работают сразу на все плоскости, таким образом, все биты ячейки адресуются одновременно. Полезно обратить внимание на то, что число выходных линий в дешифраторах при этом не увеличивается.

ЗУ С ВНУТРЕННЕЙ ДВУНАПРАВЛЕННОЙ ШИНОИ ДАННЫХ

Дальнейшее сжижение числа внутренних связей в модуле памяти с произвольным доступом можно получить за счет внутренних входных и выходных линий данных, показанных на рис. 2. Для этого обе линии данных каждого бита слова заменяются одной двунаправленной линией. При записи информация посылается по этой линии в выбранную ячейку. При чтении информация из выбранной ячейки выдается на эту же линию. Здесь вполне применима монтажная логика и методика ее использования. Применение монтажной логики позволяет получить еще и дополнительную экономию в связи с тем, что становятся ненужными вентили ИЛИ, присутствующие в каждом запоминающем элементе на схеме рис. 2 и связывающие все элементы столбца с выходной линией данных.

&Л/70ММНА ЮЩ. ИСХГ7е:М£МТ&Г

X

I

I

ь

ёФ в & «5, (Л а *■ х га

ё

I

ЛМРеСЛ СГОМБЦЛ

.^Я/Ит'Ь'С

Тф*Т

У7Р*НМИ

Рисунок 5 - ЗУ с двумерной адресацией и двунаправленной линией данных. Показана плоскость одного бита слов.

Такая схема модуля памяти приведена на рис. 5. На том же рисунке приведена логическая схема запоминающего элемента с изменениями, требующимися для двумерной адресации и для работы с одной двунаправленной линией данных. Сигнал «запись» определяет направление передачи по линии данных. Логическая 1 на линии «запись», как и прежде, разрешает передачу данных в запоминающий элемент выбранной ячейки. Логический 0 разрешает обратную передачу. Это обеспечивается наличием в каждом запоминающем элементе вентиля И, на входы которого подаются три сигнала: инверсия «записи», «выборка бита» и выход триггера. Здесь применяется специальный вентиль И, позволяющий получить монтажное ИЛИ. Соединение выходов вентилей И с линией данных дает монтажное ИЛИ этих выходов.

ВЫБОРКА СТОЛБЦА С ПОМОЩЬЮ СЕЛЕКТОРА ДАННЫХ

Последняя рассмотренная схема часто встречается в варианте, представленном на рис. 6. Как следует из рисунка, здесь также используется двумерная адресация запоминающих элементов. Однако, вместо того чтобы выделять выбранный столбец в самом запоминающем элементе, выделение столбца делается «на границе матрицы» в специальном двунаправленном селекторе данных. Строка выбирается обычным способом. Данные между элементами и селектором в, каждом столбце передаются по отдельным двунаправленным линиям.

линий

АДРЕСА

СТОЛБЦА

Запись

МШИ И

Рисунок 6 - Двумерная матрица для одного бита памяти с произвольным доступом при использовании селектора данных для выборки столбца.

При чтении по линиям, соответствующим столбцам, содержимое всех элементов строки посылается в селектор, а селектор уже выбирает бит одного, столбца в соответствии с заданным адресом и выдает этот бит на выходную линию данных. При записи селектор возбуждает линию только одного столбца, соответствующего заданному адресу, подавая в нее значение входной линии данных. Это значение доминирует над значением, которое выдает в линию элемент выбранной строки. Специальные схемы в запоминающем элементе осуществляют как доминирование («старшинство») поступающего извне значения, так и сохранение этого значения в запоминающем элементе выбранной строки. В результате достигается дальнейшее снижение числа соединений, поскольку с помощью одной линии на столбец выполняется и выборка столбца, и передача данных.

Рассмотренные схемы позволяют понять общие принципы работы запоминающих устройств с произвольным доступом. Они обладает возможностями как запоминать информацию в заданной ячейке, так и получать ее из заданной ячейки. Такие ЗУ называются ЗУ со считыванием и записью или оперативными ЗУ, сокращенно ОЗУ. Во многих ситуациях желательно получать информацию из заданных ячеек, не имея возможности изменить их содержимое. ЗУ такого типа называют постоянными ЗУ или, сокращенно, ПЗУ.

ЭЛЕКТРОННЫЕ СХЕМЫ ОПЕРАТИВНОЙ ПАМЯТИ

По способу хранения информации в запоминающих элементах полупроводниковые ОЗУ делятся на две основные категории:

статические и

динамические.

Статические элементы способны хранить информацию как угодно долго, пока подается электропитание. Все рассмотренные нами триггеры обладали этим свойством.

Динамические запоминающие элементы, напротив, способны хранить информацию только короткое время. Поэтому для сохранения информации ее нужно периодически обновлять, или, другими словами, регенерировать. В качестве динамического элемента, хранящего бит информации, можно воспользоваться заряженным конденсатором. Использование динамических элементов приводит к упрощению схем, снижению потребляемой мощности, а иногда и к повышению скорости работы.

Для обеих категорий оперативных ЗУ уже существует много различных электронных схем и еще больше, по-видимому, появится в будущем. Их разнообразие отражает не только разнообразие технологий (ТТЛ, МОП, КМОП, ЭСЛ и т. п.) и конструкций, но еще и разнообразие требований, предъявляемых к модулям памяти в отношении быстродействия, емкости, плотности упаковки логических элементов и потребляемой мощности.

Для иллюстрации мы выбрали и рассмотрим в этом разделе три типичных примера схем, хотя, конечно, из различных технических описаний можно получить детальные сведения о многих других вариантах ОЗУ. В качестве примеров мы выбрали статическое ОЗУ на ТТЛ-схемах, а также статическое и динамическое ОЗУ на МОП-схемах.

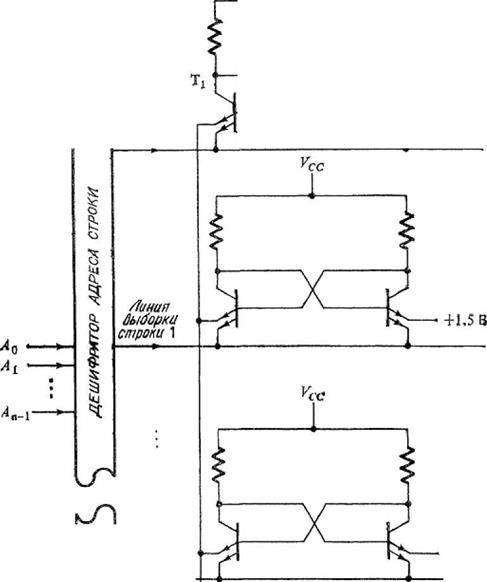

Статическое ОЗУ на ТТЛ-схемах

На рис. 20 показана конфигурация модуля статического ОЗУ на ТТЛ-схемах и электронная схема каждого запоминающего элемента. В схеме два транзисторных каскада, соединенных крест-накрест и способных находиться в двух устойчивых состояниях. В каждом транзисторе по два эмиттера, что позволяет осуществлять как хранение информации, так и выборку элемента. Такой транзистор открыт, т. е. проводит ток, если открыт (имеет прямое смещение) хотя бы один переход база-эмиттер.

Следовательно, состояние транзистора зависит от того из двух эмиттеров, на котором потенциал ниже.

X

+ 1.5 В

+1.5$

ДРУГИЕ

СТОЛБЦЫ

Пиния

ёыбарт

СЯфШ/О

АДРЕС

Линия Выборки строки 2*4

Замечание I Есаа эашшь=й,

та усихитет считывания Ланин номвтяьни тдВержвдвет

ванных на сваей входной ланш

Вшивные ванные

Рисунок 20 - Статическое ОЗУ на ТТЛ-схемах.

входные

ванные'

Запись

потенцией 1.5 В. Лвзтвшу содержимое счатыва&мога элемента не разрушает о я

Если строка, где находится рассматриваемый запоминающий элемент, не выбрана, то соответствующая линия выборки несет низкий потенциал, и он подается на нижние по схеме эмиттеры. В этом случае схема ведет себя, как обычная бистабильная схема, и сохраняет то состояние, в которое она была установлена раньше. А именно если транзистор Т открыт, то его коллектор и, следовательно, база транзистора Т2 имеют низкий потенциал. При этом Т2 окажется закрытым, что приведет к высокому потенциалу на его коллекторе и базе Т2.

Высокий потенциал на базе Т означает, что Т открыт, как и было предположено сначала. Таким образом, это состояние стабильно, т. е. самоподдерживается. В силу симметрии противоположное состояние, когда Т закрыт, а Т2 проводит, также стабильно. Легко видеть, что наша схема аналогична обычному триггеру, составленному из двух вентилей И-НЕ, соединенных крестообразно. Фактически каждый транзисторный каскад нашей схемы выполняет функцию двухвходового вентиля И-НЕ.

С другой стороны, если строка с данным элементом выбрана, то линия выборки и нижние эмиттеры транзисторов имеют высокий потенциал. Следовательно, проводимость транзистора будет зависеть от верхнего эмиттера. На верхний эмиттер транзистора Т2 подан фиксированный уровень 1.5 В. Поэтому состоянием схемы можно управлять, меняя потенциал верхнего эмиттера в транзисторе Т относительно уровня 1.5 В.

Если на линию данных подать низкий уровень, то Т станет проводящим. Это справедливо, так как потенциал коллектора Т2, равный потенциалу базы Т2, должен быть выше 1.5 В, и это гарантирует прямое смещение верхнего перехода база-эмиттер, достаточное, чтобы открыть транзистор Т . Проводимость Т приводит к низкому потенциалу на базе Т2 и к его закрытию. Это состояние схемы ассоциируется с логической

1.

В противоположное состояние схему можно привести, если оставить верхний эмиттер Т «свободным» (плавающим). В этом случае Т будет закрыт, что приведет к высокому потенциалу на его коллекторе и базе Т2. Следовательно, Т2 будет открыт. Это состояние ассоциируется с логическим 0.

В каждом столбце на линию данных, подсоединенную к верхним эмиттерам всех транзисторов Т2, работает вентиль И-НЕ с открытым коллектором. На один вход этого вентиля подается сигнал с линии «входные данные», т. е. с источника бита, записываемого в рассматриваемом столбце, а на другой вход подается сигнал «запись». Если значение сигнала «запись» равно логической 1, то логическая 1 на линии «входные данные» дает низкий потенциал на выходе вентиля И-НЕ, что приводит выбранный запоминающий элемент в состояние 1; с другой стороны, при логическом 0 на линии «входные данные» выход вентиля остается «свободным» (плавающим), что приводит выбранный

запоминающий элемент в состояние 0.

Если же на линии «запись» логический 0, то запись не должна производиться и ни один элемент не должен менять своего состояния. Более того, в этой ситуации может выполняться операция чтения. Для достижения обеих этих целей в каждом столбце предусмотрен специальный усилитель считывания, реагирующий на ток. Разрешающим сигналом для этого усилителя является логический 0 в линий «запись». Когда усилитель открыт, он поддерживает потенциал в линии данных для столбца близким к 1.5 В. Это обеспечивает неизменность состояния запоминающего элемента в выбранной строке, поскольку оба его верхних эмиттера имеют равные потенциалы. Более того, усилитель реагирует на наличие тока в линии данных столбца и выдает на линию «выходные данные» соответствующее напряжение.

|

из

5.00

|

Обсуждение в статье: Методы Изоляции элементов друг от друга в микросхемах 8 страница |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы