|

Главная |

Вычитатель для положительных операндов

|

из

5.00

|

Схемы выполнения арифметических операций

Выполнение арифметических операций в ЭВМ осуществляется с помощью арифметико-логических устройств (АЛУ), являющихся универсальным средством для этих целей. АЛУ работают под микропрограммным управлением и в качестве цены за универсальность имеют сложную структуру и не всегда отвечают требованиям, предъявляемым к их быстродействию.

В системах автоматики часто требуется выполнение какой-либо одной арифметической операции, производимой быстро и с минимальными аппаратными затратами. Поэтому специализированные БИС, предназначенные для использования в этих системах, часто содержат встроенные арифметические устройства с жесткой управляющей логикой, имеющие высокое быстродействие и не требующие внешнего управления. Рассмотрению этих устройств посвящена данная глава

Сумматор и вычитатель

Существуют различные схемы сумматоров и вычитателей чисел, представленных в двоичном коде. О способах их построения можно прочитать в книгах [2,3]. Эти схемы имеют в своем составе несколько типов элементов, отличающихся логическими функциями и числом входов, содержат подчас элементы со сложными логическими функциями (например, И-ИЛИ-НЕ). Они вполне могут быть реализованы в К-МОП базисе, однако их характеристики не будут соответствовать ожидаемым, и, кроме того, площадь, занимаемая ими на кристалле, оказывается значительной.

При конструировании устройств в К-МОП базисе следует стремиться к минимуму логических (а значит и конструктивно-топологических) единиц, составляющих схему в целом, и избегать применения многовходовых элементов и элементов со сложными логическими функциями, поскольку они имеют низкое быстродействие.

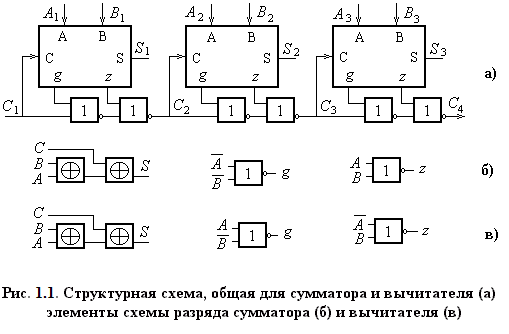

Рассмотрим схему сумматора с минимальным количеством типов логических элементов. Для понимания схемы приведем логику ее построения. На рис.1.1а приведена блок-схема сумматора, в которой выделена цепь последовательного (сквозного) переноса, состоящая из элементов 2ИЛИ-НЕ, а устройство разряда не расшифровано и изображено в

виде многополюсника. На вход многополюсника подаются значения разрядов чисел A и B и сигнал переноса C. На выход выводятся значения суммы S и еще два сигнала: g - сигнал возникновения (генерации) переноса в данном разряде; z - сигнал запрета сквозного переноса.

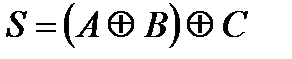

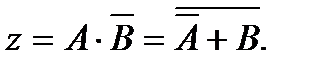

В терминах булевой алгебры значение суммы S определяется выражением:

. .

| (1.1) |

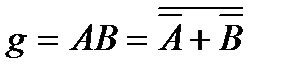

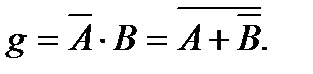

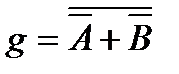

Перенос инициируется в данном разряде, если А=В=1. Поэтому

. .

| (1.2) |

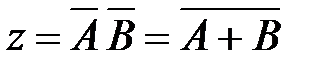

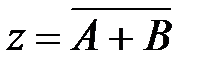

Распространение переноса по цепи сквозного переноса запрещается данным разрядом, если А=В=0. В связи с этим справедливо выражение:

. .

| (1.3) |

Выражениям (1.1), (1.2) и (1.3) соответствуют элементы схемы разряда сумматора, показанные на рис.111.1б. Схемы содержат всего два типа элементов: исключающее ИЛИ и 2ИЛИ-НЕ. Сигналы А, В, С являются входными для данного разряда, а сигналы  и

и  снимаются с внутренних линий исключающего ИЛИ. Межсоединения элементов на схеме не показаны для упрощения рисунка.

снимаются с внутренних линий исключающего ИЛИ. Межсоединения элементов на схеме не показаны для упрощения рисунка.

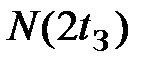

Максимальное время задержки сумматора, содержащего N разрядов, определяется временем распространения сигнала переноса до выхода и равно  .

.

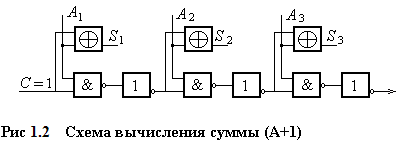

В ряде случаев необходимо выполнить операцию сложения числа А с единицей (А+1). Схему, выполняющую эту операцию, можно получить, упростив схему сумматора (рис.1.1а ,1.1б), полагая сигнал В=0 и С=1. Такая схема дана на рис.1.2. Как видно из рисунка, разряд не инициирует перенос  , в то время как запрет распространения переноса возникает при А=0.

, в то время как запрет распространения переноса возникает при А=0.

Рассмотрим формирование разности (А-В) двух положительных двоичных чисел А и В для случая А>В. Покажем, что процесс вычитания осуществляется устройством, блок-схема которого не отличается от блок-схемы сумматора (рис.1.1а). В вычитателе имеется цепь сквозного распространения заема, а в многополюснике формируются три сигнала: g- сигнал генерации заема; z - сигнал запрета распространения заема; S - сигнал разности (сохраним прежние обозначения).

Рассмотрим функции многополюсника. Нетрудно заметить, что в любом разряде, на входы которого подаются значения А, В и сигнал заема из младшего разряда С, значение разности S совпадает со значением суммы, которая формировалась в сумматоре при сложении А, В и С. Поэтому разность S будет определяться выражением (1.1).

Разряд будет генировать заем, если А=0 и В=1. Поэтому

| (1.4) |

Разряд запрещает распространение заема по цепи при А=1 и В=0. В связи с этим

| (1.5) |

Булевым выражениям (1.1), (1.4), и (1.5) соответствует схема устройства многополюсника вычитателя, показанная на рис. 1.1в.

Время формирования разности схемой вычитателя равно  .

.

Следует отметить особенность вычитателя, используемую для реализации сложных устройств, в которых он является составной частью. Вычитатель формирует знак разности Зн, в качестве которого выступает потенциал на линии заема старшего разряда. Наличие "1" на линии заема (Зн=1) говорит об отрицательной разности чисел (А-В). При этом полученное на выходе схемы число не является разностью (A-B). Для получения истинной разности необходимо провести дополнительные преобразования. Рассмотренные простые устройства используются в схемах вычитателей

положительных операндов, сумматоров чисел с произвольными знаками , схемах умножения и деления.

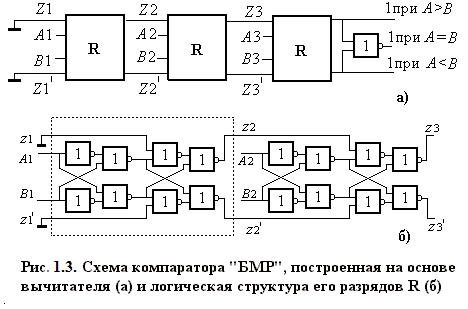

1.2. Компаратор "БМР" на основе вычитателя

Схема вычитателя может использоваться для построения компаратора. В этом случае она должна быть упрощена исключением блока формирования разности S (двух схем исключающее ИЛИ). Сравнение чисел А и В проводится путем вычитания.

Сигнал заема определяет результат сравнения. Используя два таких вычитателя для разностей (А-В) и (В-А), можно построить компаратор "Больше - Меньше - Равно" (БМР), схема которого дана на рис.1.3.

При объединении двух вычитателей оказывается, что появляются логические элементы, одинаковые в обеих схемах, которые можно объединить. Поэтому схема компаратора БМР получается компактной.

Выходные сигналы "1" при А>В и при А<B являются сигналами заема при вычитании (А-В) и (В-А), соответственно. Если сигналы по обеим шинам равны 0, то это обозначает ситуацию: А=В, что фиксируется логическим элементом 2ИЛИ-НЕ.

На рис.1.3 пунктиром выделен базовый элемент, соответствующий одному разряду R компаратора. Для многоразрядного компаратора этот элемент мультиплицируется.

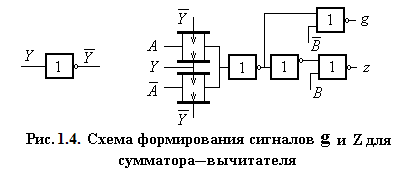

Сумматор-вычитатель

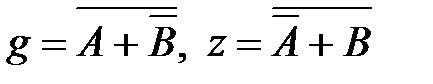

Сопоставляя элементы схем разряда сумматора и вычитателя (рис.1.1б и рис.1.1в), можно заметить, что их отличие состоит лишь в значении сигнала А на входе формирователей сигналов g и z.

Учитывая это обстоятельство, несложно построить единую схему, которая по сигналу управления Y может выполнять функцию сумматора (например, при Y=1) и вычитателя (при Y=0). Универсальная схема формирователей сигналов g и z показана на рис.1.4. Как следует из рисунка, при Y=1 открыт верхний проходной ключ, обеспечивающий  и

и  , что соответствует операции суммирования. При Y=0 открытым является нижний ключ, и

, что соответствует операции суммирования. При Y=0 открытым является нижний ключ, и  определяют операцию вычитания.

определяют операцию вычитания.

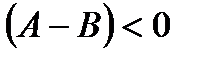

Напомним, что рассмотренные схемы вычитания дают правильный результат при выполнении операции лишь в случае (А-В)>0. Однако сумматор - вычитатель используется в других схемах, например в схеме сложения чисел с произвольными знаками.

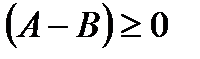

Вычитатель для положительных операндов

Рассмотрим операцию вычитания для положительных чисел А и В, когда В может быть как меньше, так и больше А. Будем считать, что оба числа представлены на фиксированной разрядной сетке разрядностью n. Для представления разности S в схеме вычитателя выделим дополнительный (старший) разряд, в котором будет отображаться знак разности Зн. При  значение Зн=0, а при

значение Зн=0, а при  Зн=1.

Зн=1.

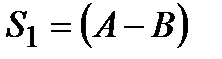

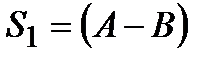

Операцию получения разности чисел S=(А-В) организуем с использованием средств, рассмотренных в предыдущих разделах, в соответствии со следующим алгоритмом:

1. Получим с помощью вычитателя значение разности  и ее знак Зн (Зн - сигнал заема вычитателя, сформированный на выходе старшего разряда);

и ее знак Зн (Зн - сигнал заема вычитателя, сформированный на выходе старшего разряда);

2. Если Зн=0, то разность S1является конечным результатом, ее выведем и перейдем на 4;

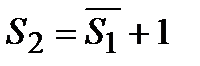

3. Если Зн=1, то

3.1. Разность  проинвертируем, т.е. заменим 0 на 1, а 1 на 0 во всех разрядах, исключая знаковый разряд, и полученное число обозначим

проинвертируем, т.е. заменим 0 на 1, а 1 на 0 во всех разрядах, исключая знаковый разряд, и полученное число обозначим  ;

;

3.2. Найдем сумму  , являющуюся конечным результатом и ее выведем.

, являющуюся конечным результатом и ее выведем.

4. Конец.

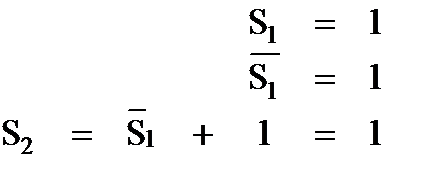

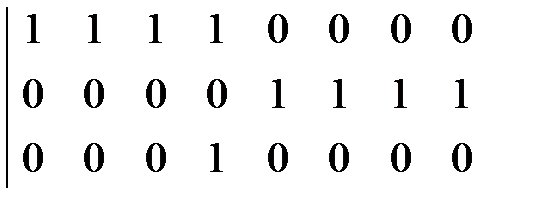

Проиллюстрируем приведенный алгоритм числовым примером для случая А<В. Пусть сетка фиксированной длины, на которой представляются числа, достаточна для 8 разрядных чисел. В соответствии с п.1 найдем разность А-В для А=9, В=25:

| Зн | о п е р а н д ы | ||||||||

| А=9 | |||||||||

| B=25 | |||||||||

| S1 |

Единицы в числе S1 в разрядах 6, 7, 8 и Зн появились вследствие заема при вычитании.

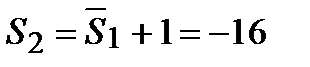

Поскольку значение Зн=1, то необходимо S1 проинвертировать и сложить с 1:

Как видим, значение конечного результата  , что соответствует истине.

, что соответствует истине.

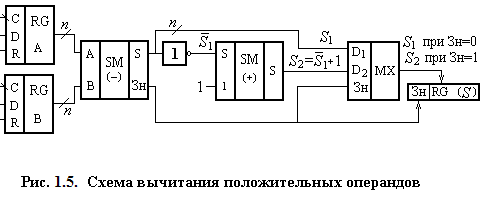

Схема вычитания положительных операндов приведена на рис. 1.5.

Операнды А и В записываются в регистры, предварительно установленные в состояние "все нули". При этом неиспользуемые старшие разряды регистров оказываются заполненными нулями. Вычитатель  , имеющий ту же разрядность, что и регистры, формирует разность

, имеющий ту же разрядность, что и регистры, формирует разность  и ее знак Зн (на выходе цепи сквозного распространения заема). Разность

и ее знак Зн (на выходе цепи сквозного распространения заема). Разность  по одному из каналов поступает на вход мультиплексора MХ, а по второму на вход инверторов. После инвертирования разность

по одному из каналов поступает на вход мультиплексора MХ, а по второму на вход инверторов. После инвертирования разность  суммируется с 1 и сумма

суммируется с 1 и сумма  поступает на второй вход мультиплексора MХ. Сигнал Зн, полученный от вычитателя SM(-) является управляющим сигналом для мультиплексора. При Зн=0 мультиплексор передает на выход значение

поступает на второй вход мультиплексора MХ. Сигнал Зн, полученный от вычитателя SM(-) является управляющим сигналом для мультиплексора. При Зн=0 мультиплексор передает на выход значение  , а при Зн=1 значение

, а при Зн=1 значение  . Знаком разности является сигнал Зн.

. Знаком разности является сигнал Зн.

|

из

5.00

|

Обсуждение в статье: Вычитатель для положительных операндов |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы